FPGA----只读存储器(ROM)

Verilog HDL:

module ROM_ex1 (addr, data, en);

input [:] addr;//地址选择信号

input en; //使能端

output reg [:] data;//数据输出端

reg[:] data1 [:];

always @(*)

begin

data1[] <= 'b1010_1001;

data1[] <= 'b1111_1101;

data1[] <= 'b1110_1001;

data1[] <= 'b1101_1100;

data1[] <= 'b1011_1001;

data1[] <= 'b1100_0010;

data1[] <= 'b1100_0101;

data1[] <= 'b0000_0100;

data1[] <= 'b1110_1100;

data1[] <= 'b1000_1010;

data1[] <= 'b1100_1111;

data1[] <= 'b1100_0001;

data1[] <= 'b1001_1111;

data1[] <= 'b1010_0101;

data1[] <= 'b0101_1100;

if (en)

begin

data[:] <= data1[addr];

end

else

begin

data[:] <= 'bzzzz_zzzz;

end

end

endmodule

Testbench:

`timescale ps/ ps

module ROM_ex1_vlg_tst();

reg [:] addr;

reg en;

wire [:] data; ROM_ex1 i1 (

.addr(addr),

.data(data),

.en(en)

);

initial

begin

addr = 'd0;

en = 'b0;

# addr = 'd5;

en = 'b1;

# addr = 'd9;

# addr = 'd12;

# addr = 'd15;

$display("Running testbench");

end endmodule

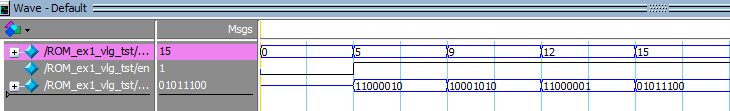

仿真波形:

观察波形可知,当 en 为“1”时,data 输出数据,否则 data 为高阻态,addr 为地址选择信号,当其输入不同的值时,data 输出相应的存储的数据。

FPGA----只读存储器(ROM)的更多相关文章

- FPGA中ROM与RAM相关知识总结(五)

把看到的关于存储的一些东西整理一下,有些话来自于网友,所以还是那句话,看到的人要带着自己的思考去看,记住尽信书不如无书,fighting!!! 一.基本概念 最熟悉的两个词语应该是RAM与ROM,RA ...

- Xilinx FPGA使用——ROM初始化文件

在调用ROM的IP Core时,需要对其进行初始化,利用MATLAB生成其初始化数据文件. 工具:ISE 14.7.MATLAB.notepad++ 废话不多说,直接上MATLAB代码,生成了一个10 ...

- 【MATLAB】产生FPGA中ROM需要的余弦表

产生的二进制数为带符号二进制数,最高位是符号位. function [ DATA ] = cos_gen( Num_addr,Num_out ) % 用来产生ROM需要的余弦表,输出为有符号二进制数 ...

- 谈谈IC、ASIC、SoC、MPU、MCU、CPU、GPU、DSP、FPGA、CPLD

IC (integrated circuit) 集成电路:微电路.微芯片.芯片:集成电路又分成:模拟集成电路(线性电路).数字集成电路.数/模混合集成电路: 模拟集成电路:产生.放大.处理各种模拟信号 ...

- ROM与RAM知识

“ROM”和“RAM”的意思: “ROM”:N年前代表一种只能写入和读取,而不能改写和擦除的设备,可以用光驱CD-ROM来说明这个道理.目前的“ROM”已经不是这个道理了,它的技术已经飞快的发展到现在 ...

- ROM及其他知识

ROM--Read Only Memory 中文意思是:只读存贮器 以前的游戏机用的都是卡带,里面是一块或几块集成电路芯片,游戏程序就是在生产厂家一次性写入这几块芯片,以后用户玩游戏的时候只能读出 ...

- 【小梅哥FPGA进阶教程】第十四章 TFT屏显示图片

十四.TFT屏显示图片 本文由杭电网友曾凯峰贡献,特此感谢 学习了小梅哥的TFT显示屏驱动设计后,想着在此基础上通过TFT屏显示一张图片,有了这个想法就开始动工了.首先想到是利用FPGA内部ROM存储 ...

- GSM BTS Hacking: 利用BladeRF和开源BTS 5搭建基站

引文 如果你已经购买了Nuand(官方)BladeRF x40,那么就可以在上面运行OpenBTS并可以输入一些指令来完成一些任务.一般来说HackRF,是一款覆盖频率最宽的SDR板卡.它几乎所有的信 ...

- 数字逻辑实践6-> 从数字逻辑到计算机组成 | 逻辑元件总结与注意事项

00 一些前言 数字逻辑是计算机组成与体系结构的前导课,但是在两者的衔接之间并没有那么流畅,比如对面向硬件电路的设计思路缺乏.这篇总结是在数字逻辑和计组体系结构的衔接阶段进行的. 虽然这篇文是两门课的 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

随机推荐

- [转] 利用CORS实现跨域请求

[From] http://newhtml.net/using-cors/ 跨域请求一直是网页编程中的一个难题,在过去,绝大多数人都倾向于使用JSONP来解决这一问题.不过现在,我们可以考虑一下W3C ...

- [转] Tomcat 禁用URL中的JSESSIONID

[From] http://stackoverflow.com/questions/962729/is-it-possible-to-disable-jsessionid-in-tomcat-serv ...

- hdu 2654 Be a hero

()Become A Hero Time Limit: 15000/5000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others) ...

- 剑指offer——面试题11:旋转数组的最小数字

#include"iostream" using namespace std; int GetMinNumber(int *data,int len) { ,right=len-, ...

- 7.使用jenkins+marathon+docker完成自动化部署

1.前置条件 1)Docker开启TCP端口,CloudBees Docker Build and Publish plugin插件会向目标主机docker生成docker镜像 开启docker ap ...

- Java中使用nextLine(); 没有输入就自动跳过的问题

转自:https://www.cnblogs.com/1020182600HENG/p/6564795.html [问题分析] 必要的知识:in.nextLine();不能放在in.nextInt() ...

- Laplace变换要点

Laplace变换在求解微分方程.信号系统.自动控制领域都有重要作用.阅读<复变函数与积分变换>华中科大第三版,小结要点. 方便应用,最先给出变换表: 定义: 性质: 周期函数与卷积:

- oracle 备份恢复篇(六)---基于12c的pdb备份与恢复

一,备份前提描述 SQL> show con_name CON_NAME ------------------------------ CDB$ROOT SQL> archive log ...

- Hadoop升级

1.停止所有MR任务 stop-mapred.sh 2.检查HDFS hadoop fsck / -files -blocks -locations > dfs-v-old-fsck-.log ...

- java使用POI进行 Excel文件解析

package com.timevale.esign.vip.util; import java.io.File; import java.io.FileInputStream; import jav ...