FPGA时序约束理解记录

最近整理了一下时序约束的内容,顺便发出来分享记录一下。

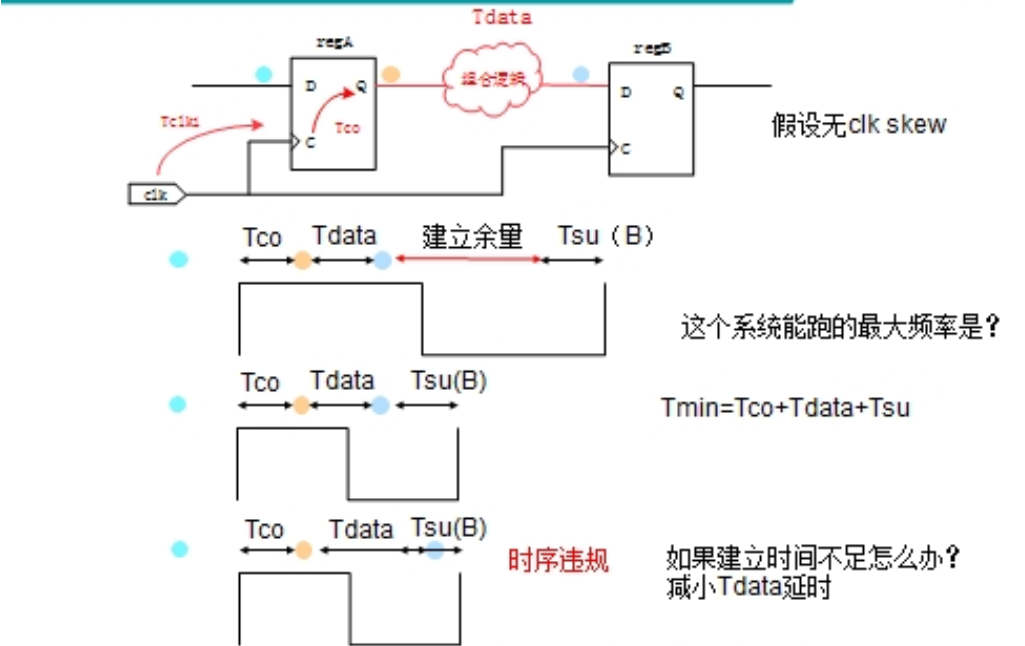

任何硬件想要工作正常,均需满足建立和保持时间,至于这个概念不再陈述。

下面将重点介绍两个概念:建立余量和保持余量。FPGA内部进行时序分析无非就是计算这两个余量,为正,则时序满足要求,否则不满足。

FPGA在与外部期间打交道时,端口如果为输入则与input delay约束相关,如果最为输出则output delay,这两种约束的值究竟是什么涵义,下文

我也会重点刨析,但是前提是需要理解图1和图2建立余量和保持余量。

建立余量:不考虑clk_skew,数据在regA 的发射沿(即第一个上升沿)经过Tco+Tdata则会一直保持不变,等待着接受沿采集,接收沿只需满足的建立时间,余量=T-Tco-Tdata即红色区所示。

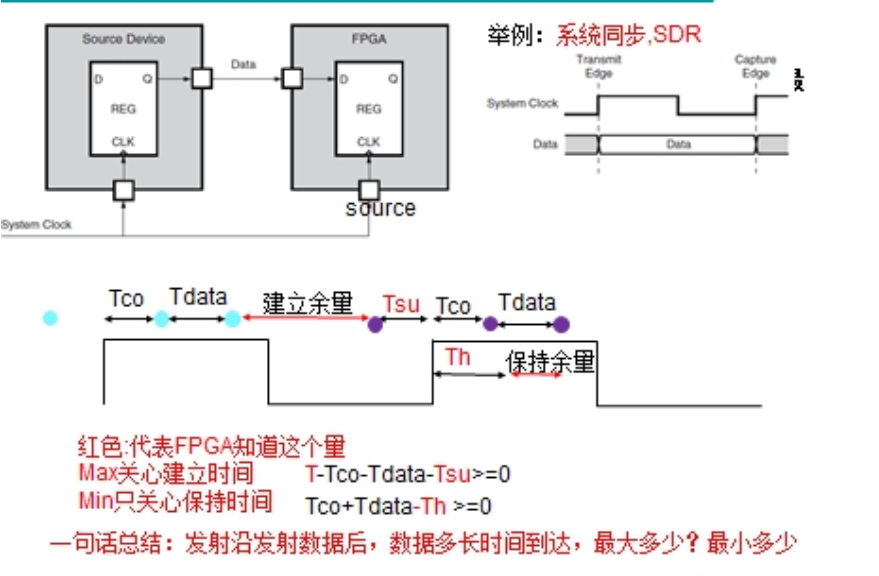

保持余量

蓝色是第一个数据,第一个上升沿是蓝色数据的发射沿,第二个上升沿是蓝色数据的接收沿

紫色是第二个数据,第二个上升沿是紫色数据的发射沿,第三个上升沿是紫色数据接收沿(图中未画)

意思是什么?第一个蓝色数据经过发射沿后延迟Tco+Tdata的时间就一直保持不变,直到紫色的数据在其发射沿来后经过Tco+Tdata时间将蓝色数据代替,蓝色数据只需要在其接收沿后停留的时间大于等于保持时间即可被正常采集,但是蓝色数据实际上能够停留多久是由Tco+Tdata决定的,因此Tco+Tdata的值决定了其在接受沿后的寿命,即Tco+Tdata>=Th就可以满足保持时间,保持余量=Tco+Tdata-Th,保持时间和时钟周期T无关,因为他的寿命是由Tco+Tdata决定的。

input delay 和output delay

对于input /output delay的保持余量和建立余量的计算方法和前面讲的是一样的,区别在于前面的例子中REGA和REGB均是在FPGA内部的,计算余量的所有参数FPGA自身是知道的,他自己可以完成整个计算分析,但是一旦涉及到input delay和output delay,即FPGA作为是接收端或者发送端与其他器件交互时,有些计算的参数FPGA自己知道,有的计算的参数是外部器件知道,为了完成余量的计算,那么就要通过约束把FPGA不知道的量告诉FPGA。

用input delay举例说明 见下图

建立余量=T-Tco-Tdata-Tsu,FPGA作为接收端Tsu,Th是知道的,但是其余两个量不知道,Tco与外部器件性能相关,可以从其数据手册中获取这个量,Tdata也许和你PCB的布线延迟等有关,为了完成计算,只需要把Tdata+Tco的最告诉fpga即可,max参数是与建立参数相关,min与保持余量相关,其最大值为 input delay max为Tco+Tdata的最大值,最小值为input delay min为Tco+Tdata的最小值。

output delay见下图,红色代表FPGA自己知道的量,其余需要通过约束告知

所以max 为Tdata+Tsu

min为Tdata-Th

下面是我做的记录

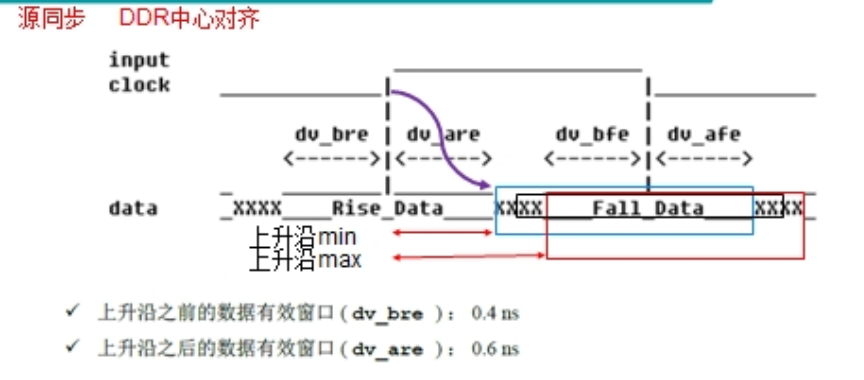

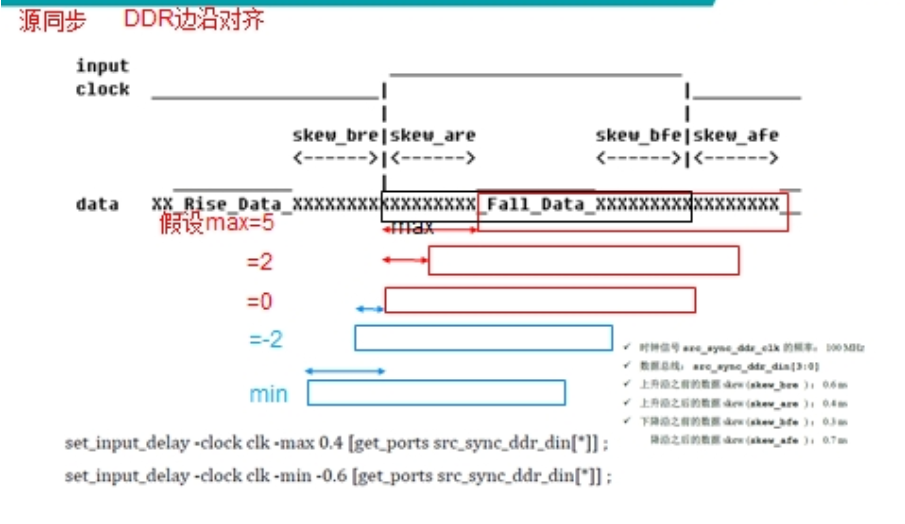

SDR和DDR的概念:S是单沿触发,D是双沿,双沿又分中心对齐和边沿对齐,见图

下图是input delay 的DDR中心对齐,其中黑色方框框起来的是理想情况下的数据,蓝色是数据整体左偏移,红色是数据整体右偏移,来回抖动的范围,图示中XXXX则表示的数据不稳定的区域,对于上升沿,最小值就是到蓝色框dv_are的大小,最大值就是到红色框边沿T/2-dv_bfe.下降沿不再赘述。

对于DDR边沿对齐,对上升沿来讲,黑色数据框是理想情况,红色是向右偏移,蓝色则是向左偏移,在第三个红色框那里,延迟已经等于0,再进一步左移则为负,蓝色所示。对上升沿来讲,max为skew_are,min为 负-skew_bre。

FPGA时序约束理解记录的更多相关文章

- FPGA时序约束的几种方法 (转)

FPGA时序约束的几种方法 对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地, ...

- FPGA时序约束和timequest timing analyzer

FPGA时序约束 时钟约束 #************************************************************** # Create Clock #****** ...

- FPGA时序约束——理论篇

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束.这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的.好的时序约束可以指导布局布 ...

- FPGA时序约束一点总结

时序约束的一点总结. 打拍.掌握好时序. 手动分配位置,这个不是一定有效. 打破层级或者物理综合,或者自动加流水等综合优化参数调整. 根据实际情况使用异步时钟策略. 换速度更快的片子. 最也进接手一个 ...

- FPGA基础学习(5) -- 时序约束(实践篇)

目录 1. 理论回顾 2. 时间裕量 3. 最大延迟和最小延迟 4. 案例分析 参考文献: 距离上一篇有关时序的理论篇已经有一段时间了(可以参考博文FPGA时序约束--理论篇),实际上此段时间,甚至到 ...

- 简述FPGA时序约束理论

FPGA时序约束简介. 时序约束的场景: 在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束.但在复杂电路中,为了减少系统中各部分延时,使系统协同工作,提高运行频率,需要进行时 ...

- 【转载】如何在FPGA设计环境中添加加时序约束

转自:http://bbs.ednchina.com/BLOG_ARTICLE_198929.HTM 如何在FPGA设计环境中加时序约束 在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序 ...

- FPGA基础学习(4) -- 时序约束(理论篇)

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束.这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的.好的时序约束可以指导布局布 ...

- Xilinx FPGA编程技巧之常用时序约束详解

1. 基本的约束方法 为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取.最普遍的三种路径为: 输入路径(Input Path),使用输入约束 寄存器到寄存器路径(Register-to ...

随机推荐

- 跨域及JSONP原理

什么是跨域:a.com 域名下的js无法操作b.com或是c.a.com域名下的对象 为什么浏览器要引入跨域问题? 跨域问题来源于浏览器的同源策略,为啥要有这个策略呢? 为了安全.假设现在有a.com ...

- centos7 scrapy安装

1.anaconda3安装 wget https://repo.anaconda.com/archive/Anaconda3-2019.03-Linux-x86_64.sh 安装报错,可能是源的问题 ...

- python常用算法学习(3)

1,什么是算法的时间和空间复杂度 算法(Algorithm)是指用来操作数据,解决程序问题的一组方法,对于同一个问题,使用不同的算法,也许最终得到的结果是一样的,但是在过程中消耗的资源和时间却会有很大 ...

- java集合类之ArrayList详解

一.ArrayList源码分析 1.全局变量 (1)默认容量(主要是通过无参构造函数创建ArrayList时第一次add执行扩容操作时指定的elementData的数组容量为10) private s ...

- LeetCode_232-Implement Queue using Stacks

题意是使用栈实现队列:队列是先进先出,后进后出. class MyQueue { public: /** Initialize your data structure here. */ MyQueue ...

- Linux上的Nginx上设置支持PHP的解析

当前的运行环境为,PHP7.2.2以 FastCGI 模式运行,默认端口为:9000,Nginx1.15.6 打开nginx配置文件 vi /usr/local/nginx/conf/nginx.co ...

- 《java编程思想》P160-P180(第八章部分+第九章部分)

1.什么是多态? 多态的定义:指允许不同类的对象对同一消息做出响应.即同一消息可以根据发送对象的不同而采用多种不同的行为方式.(发送消息就是函数调用) 现实中,关于多态的例子不胜枚举.比方说按下 F1 ...

- drf框架序列化和返序列化

0903自我总结 drf框架序列化和反序列化 from rest_framework import serializers 一.自己对于序列化和反序列化使用的分类 前后端交互主要有get,post,p ...

- PMBOK(第六版) PMP笔记-质量审计、风险审计、采购审计的区分

质量审计.风险审计.采购审计的区分 三个概念的相同之处: 都是审计的概念 都是特定知识领域的审计 三个概念的区别: (1)三个概念虽然都是审计,但分布在不同的管理过程组. ·质量审计:执行过程组, ...

- [Luogu2323] [HNOI2006]公路修建问题

题目描述 输入输出格式 输入格式: 在实际评测时,将只会有m-1行公路 输出格式: 输入输出样例 输入样例#1: 复制 4 2 5 1 2 6 5 1 3 3 1 2 3 9 4 2 4 6 1 输出 ...