《FPGA全程进阶---实战演练》第七章 让按键恢复平静

1基础理论部分

A:“怎么按键按下去之后,结果不正常?”,B:“按键你消抖了吗?”A:“消什么抖,还要消抖?”, B:“先检测按键变化,然后消抖过滤波动信号,最后输出稳定信号”,A:“我好像漏掉了什么。。。。。”。

正如上述所说,小小一个按键,里面学问也是较多的。对于按键,无论您是学什么开发板或者用什么开发板或者自己开发板子,按键资源是必不可少的,可能是整个工程中算是用到比较多的,这也是人机工程交互最直接的一个例子。下图7.1是一个常用的按键。

图7.1 按键

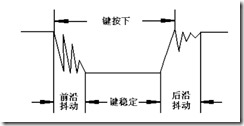

在使用的按键中,用的最多的是机械弹性按键,当机械触点断开,闭合时,由于机械触点的弹性作用,一个按键开关不会马上稳定地接通,断开时也不会一下子断开,所以这导致人在按键的过程中,会导致一连串的抖动,这样的抖动如果不及时处理,若是被捕获到,那么危害也是可想而知的。如图7.2是一个抖动的直观图。

图7.2 按键抖动

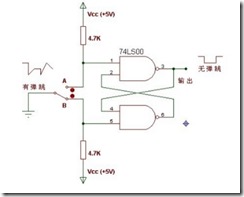

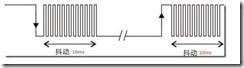

由按键的机械特性决定,一般为5~10ms,为了保持最大稳定,可以选择10ms,这足以应对正常人按键的频率了。按键消抖有两种方法,一种是硬件消抖,一种是软件消抖;图7.3是硬件消抖电路,利用两个与非门的组合电路被称为双稳态电路,经过双稳态电路可以输出稳定的波形,起到滤波作用。

在数字系统中,一般常用软件消抖,这个带来的好处是可以节约PCB的成本和空间,利用软件消抖只需一个延时操作即可,操作不麻烦。

图7.3 硬件消抖

2 Verilog代码实现部分

按照图7.4中所示的,可以进行10ms延时即可,对于人的按键完全满足要求。

图7.4 延时示意图

实现步骤:按键检测------延时------输出有效键值

|

端口名 |

功能 |

值 |

|

clk |

时钟 |

50MHz |

|

rst_n |

复位 |

初始为0 |

|

key_in |

输入按键 |

初始值全为高电平 |

|

key_valid |

输出有效值 |

按下的按键为高电平,其他为低电平 |

|

key_flag |

输出使能值,作为和下一个模块沟通的 |

高电平 |

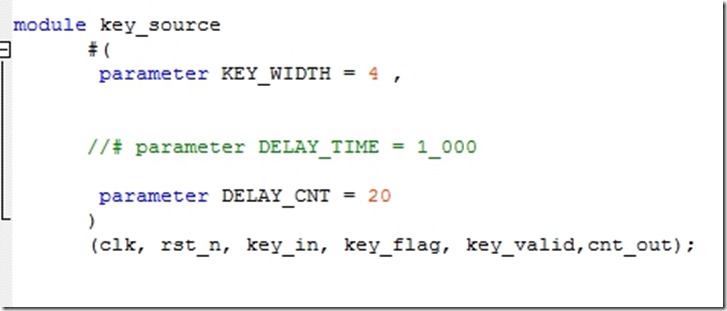

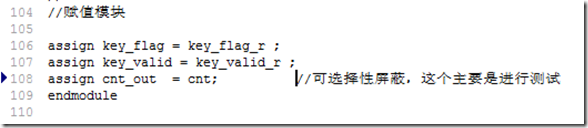

注意这种模块的书写格式,可以很方便的去更改相关的参数,达到最大化的移植。只需更改key_width就可以进行对按键数目的更改。

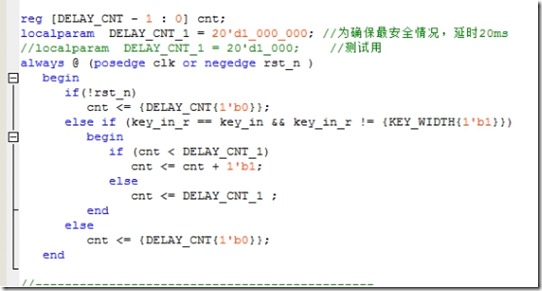

在进行计数的时候,有相应的条件,即当有键按下时才会计数,否则停止计数,这样可以节省资源。

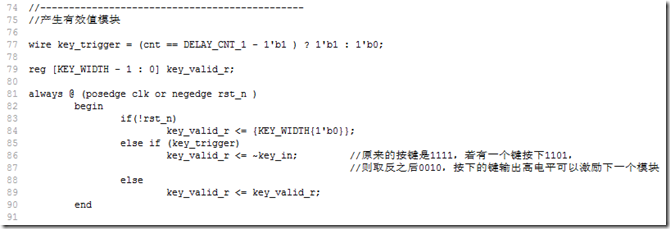

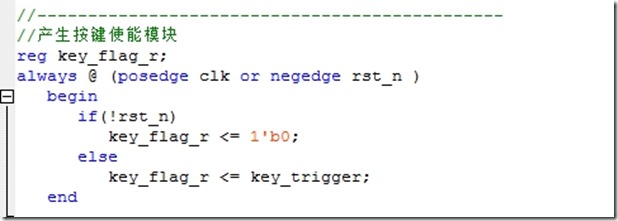

产生使能部分,方便对下一个模块的使能,能够进行良好的沟通。

3 Modelsim仿真部分

3.1 Testbench测试脚本程序:

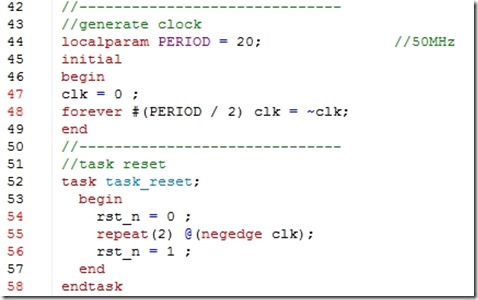

上述仍然是时钟和复位task模块。

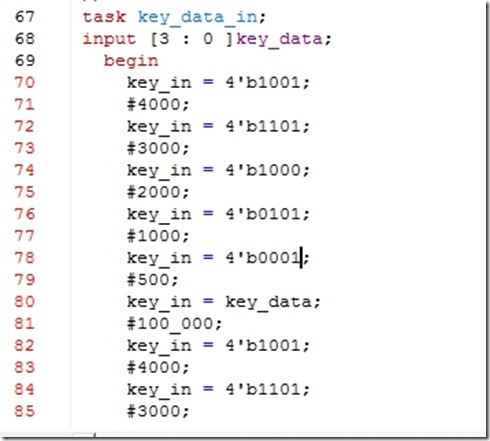

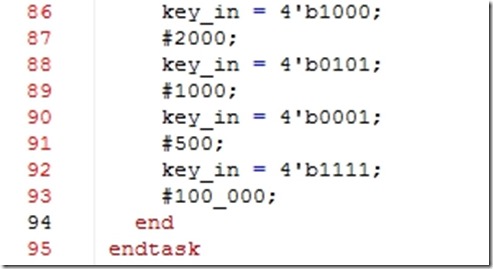

上述是模仿按键抖动的测试程序,70行到79行模拟按键刚按下时的抖动,80行输出稳定值,紧接着81行到93行是松开时抖动的情况。

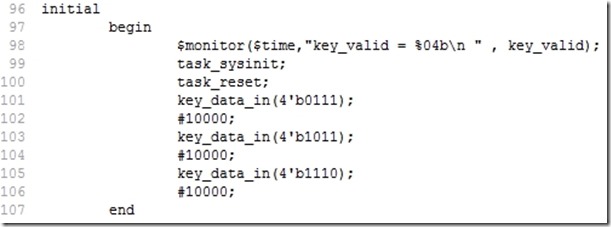

上述是运行各个模块,并输入模拟按键值。

3.2 仿真结果:

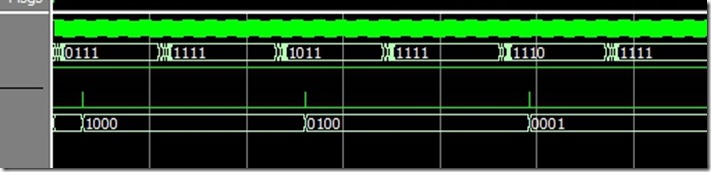

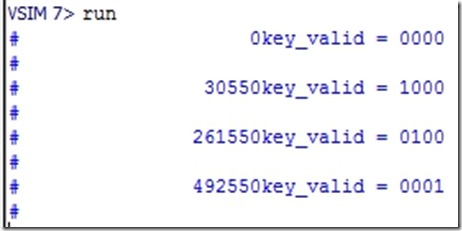

图7.5是仿真结果图,可以看到捕获到的有效信号和捕获使能信号,最终按键松开所有值恢复到高阻态。图7.6是脚本测试输出文件。

图7.5 仿真结果

图7.6 测试脚本输出

4 联合测试部分

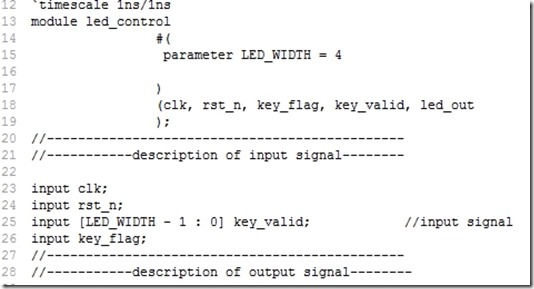

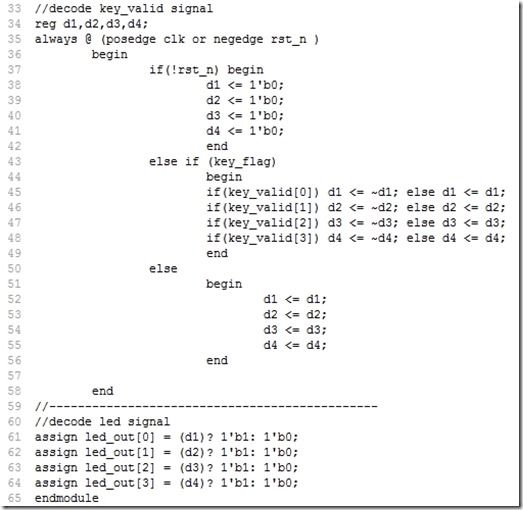

对于按键测试部分,将前面的LED部分和本节的按键进行连接即可,由按键产生的有效信号没有直接送给LED模块,而是加入一个LED_control模块用来对按键操纵LED的编码,实现的功能是按键按下LED发光,再次按下,熄灭。此部分代码在EX5_LED中。

按键key_valid信号接入led_control模块。

上述是实现按键对LED的编解码操作。

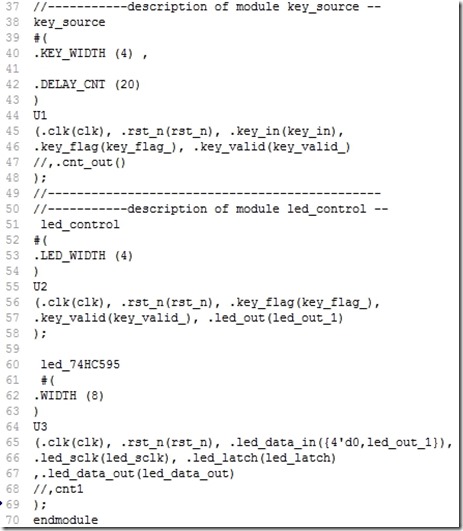

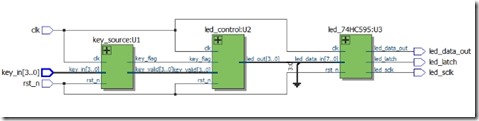

在key_led_top模块将各个信号进行连接。最终实现的RTL视图如下图7.7所示.

图7.7 RTL视图

《FPGA全程进阶---实战演练》第七章 让按键恢复平静的更多相关文章

- 《FPGA全程进阶---实战演练》第一章之如何学习FPGA

对于很多初学者,大部分都是急于求成,熟不知越是急于求成,最终越是学无所成,到头来两手空空,要学好FPGA,必须弄懂FPGA本质的一些内容. 1.FPGA内部结构及基本原理 FPGA是可以编程的,必须通 ...

- 《FPGA全程进阶---实战演练》第一章之FPGA介绍

1 什么是FPGA FPGA也即是Field Programmable Gate Array的缩写,翻译成中文就是现场可编程门阵列.FPGA是在PAL.GAL.CPLD等可编程器件的基础上发展起来的新 ...

- 《FPGA全程进阶---实战演练》第二章之焊接板子及调试注意事项

1.若是读者第一次做板子,强烈建议画完PCB板后将PCB图打印出来,然后对照你买的芯片将芯片放置对 应的位置,然后查看所有的封装格式适不适合,否则等你做出板子来后再试,为时晚矣.笔者虽然知道要这么 做 ...

- 《FPGA全程进阶----实战演练》第二章之系统搭建

1 系统方案 对于设计一款硬件平台,首先要确定整体框架,确定各个模块所需要的芯片以及电压分配情况.图2.6是笔者曾经设计的硬件平台系统. 图2.6系统框图 对于选定一个系统方案之后,接下来做的要先去查 ...

- 《FPGA全程进阶---实战演练》第二章之硬件平台的搭建

学习FPGA,多多少少应该要懂得硬件电路的设计,这样不单单增加了自己的技能,而且还能够对FPGA的硬件实现有更好的了解. 1 模块划分 对于一个基本的FPGA硬件平台,常用的几个电路部分:(1)电源电 ...

- 《FPGA全程进阶---实战演练》第九章 计数器要注意

本小节我们来做一个好玩的事情,就是计数器,还记得在做LED自加实验时我们就曾经提到过关于计数器的相关议题,那么这节我们就来讨论讨论. 探讨一下如下的问题:请用verilog记八个数的写法,分析这个可以 ...

- 《FPGA全程进阶---实战演练》第二章之PCB layout注意事项以及投板几点说明

上一篇博客讲述了各个部分的原理图,那么根据原理图画出PCB,其实PCB是一门很大的学问,想要掌握谈何容易.就笔者在画PCB时的一些注意事项做一些说明. 1.电源部分的电源线 ...

- 《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新<FPGA全程进阶---实战演练&g ...

- 《FPGA全程进阶---实战演练》第四章之实验平台软硬件使用简介

本章主要是讲解读者在进行FPGA逻辑设计之前的准备工作,需要下载Quartus II软件和 Modelsim 软件,一个是用来进行FPGA逻辑设计,一个是用来对逻辑进行理论分析与验证. 1.1 qua ...

随机推荐

- 51Nod1577 异或凑数 线性基 构造

国际惯例的题面:异或凑出一个数,显然是线性基了.显然我们能把区间[l,r]的数全都扔进一个线性基,然后试着插入w,如果能插入,则说明w不能被这些数线性表出,那么就要输出"NO"了. ...

- bootStrap中的ul导航2

<!doctype html><html > <head> <meta charset="utf-8"> <link rel= ...

- Cocos Creator代码编辑环境配置

1,可以使用较为适合js的webstorm,亦可以采用VS: 2,若需要webstorm,在下载之后,在文件,设置内外部编辑器选用webstorm.exe,即可: 3,Visual Studio Co ...

- Oracle 增加 修改 删除 列

语法结构如下: alter table tablename add (column datatype [default value][null/not null],….); alter table t ...

- 集合(2)—Collection之List的使用方法

声明集合变量 List list = new ArrayList(); 或者 : public LIst list: public 构造函数(){ this.list = new ArrayList( ...

- Android 热修复方案Tinker(一) Application改造

基于Tinker V1.7.5 Android 热修复方案Tinker(一) Application改造 Android 热修复方案Tinker(二) 补丁加载流程 Android 热修复 ...

- Java全栈程序员之04:Ubuntu下安装MySQL、注册服务及Navcat

在安装MySQL之前,我们先来介绍一下Ubuntu下软件的安装方式.首先回顾下,我们安装JDK,使用的是后缀名为tar.gz的安装包.安装idea,使用的是tar.gz:那有没有别的安装方式呢? 1. ...

- ds18b20采集温度并上报服务器

交叉编译器:arm-linux-gcc-4.5.4 Linux内核版本:Linux-3.0 主机操作系统:Centos 6.5 开发板:FL2440 温度传感器:ds18b20 注:此程序的客户端是在 ...

- GitHub for Windows简单使用

1.什么是Github gitHub是一个面向开源及私有软件项目的托管平台,因为只支持git 作为唯一的版本库格式进行托管,故名gitHub. gitHub于2008年4月10日正式上线,除了git代 ...

- MDX Cookbook 07 - 在不同层次结构的成员中实现 逻辑 OR 的效果

第一个示例:查看所有包括黑色产品的子目录产品中的 Reseller Order Quantity 和 Reseller Order Count. 第二个示例:和第一个示例查询结构一样,只是筛选的是大小 ...