时钟分频方法---verilog代码

时钟分频方法---verilog代码

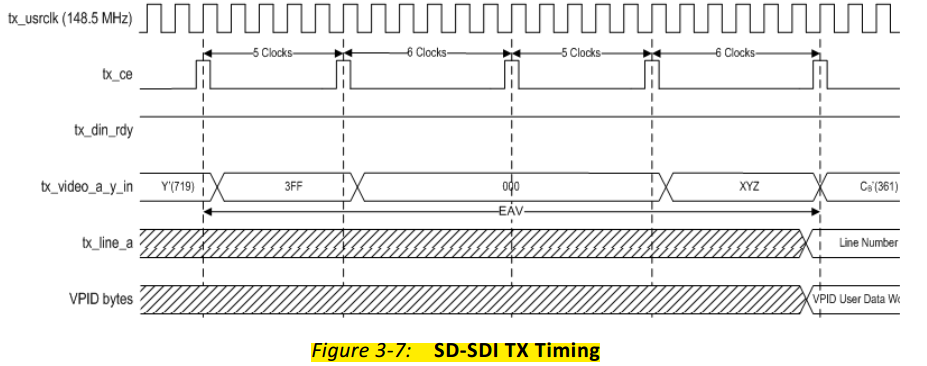

本文以SDI播出部分的工程为例,来说明一种时钟分频的写法。SD-SDI工程中播出时钟tx_usrclk为148.5MHz,但tx_video_a_y_in端的数据采样与tx_ce(门控时钟)有关。通过对tx_usrclk时钟进行分频,5clocks---6clocks---5clocks---6clocks,得到tx_ce信号。

verilog代码写法如下:

reg [:] tx_ce = 'b111;

reg tx_sd_ce = 'b0;

reg [:] tx_gen_sd_ce = 'b00000100001; // Generates 5/6/5/6 cadence SD-SDI TX clock enable

wire tx_ce_mux; // Used to generate the tx_ce signals

//

// TX clock enable generator

//

// sd_ce runs at 27 MHz and is asserted at a 5/6/5/6 cadence

// tx_ce is always 1 for 3G-SDI and HD-SDI and equal to sd_ce for SD-SDI

//

// Create 3 identical but separate copies of the clock enable for loading purposes.

//

always @ (posedge tx_usrclk)

if (tx_fabric_reset) //复位信号来源于?

tx_gen_sd_ce <= 'b00000100001;

else

tx_gen_sd_ce <= {tx_gen_sd_ce[:], tx_gen_sd_ce[]}; //此段代码用于产生 always @ (posedge tx_usrclk)

tx_sd_ce <= tx_gen_sd_ce[]; assign tx_ce_mux = tx_mode == 'b01 ? tx_gen_sd_ce[10] : 1'b1; always @ (posedge tx_usrclk)

tx_ce <= { {tx_ce_mux}};

重点关注tx_gen_sd_ce = 11'b00000100001信号,用来生成5/6/5/6序列。

always @ (posedge tx_usrclk)

if (tx_fabric_reset) //复位信号来源于?

tx_gen_sd_ce <= 'b00000100001;

else

tx_gen_sd_ce <= {tx_gen_sd_ce[:], tx_gen_sd_ce[]}; //此段代码用于产生

always @ (posedge tx_usrclk)

tx_sd_ce <= tx_gen_sd_ce[];

每当tx_usrclk上升沿到来时,tx_gen_sd_ce左移一位,最高位移到最低位。tx_sd_ce取tx_gen_sd_ce的最高位,需要注意的是:tx_gen_sd_ce 和tx_sd_ce是同时变化的,都由tx_usrclk上升沿控制。

当tx_gen_sd_ce = 10000100000时,tx_sd_ce为高电平,由此开始,当下一次tx_sd_ce为高电平时,tx_gen_sd_ce = 10000010000需要花费5clocks,当tx_sd_ce再次为高电平时,tx_gen_sd_ce = 10000100000需要花费6clocks,循环下去,由此就产生了5/6/5/6序列。

时钟分频方法---verilog代码的更多相关文章

- HD,3G视频数据中行号的插入方法---Verilog代码实现

HD,3G视频数据中行号的插入方法---Verilog代码实现 行号的生成: `timescale 1ns / 1ps //////////////////////////////////////// ...

- 分享:FIFO 同步、异步以及Verilog代码实现

FIFO 很重要,之前参加的各类电子公司的逻辑设计的笔试几乎都会考到. FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线 ...

- Verilog代码和FPGA硬件的映射关系(一)

代码和硬件之间的映射关系是一个很奇妙的过程,也展现出人类的智慧.单片机内部的硬件结构都是固定的,无法改变,我们通过代码操作着寄存器的读写,来执行各种复杂的任务.FPGA的硬件结构并不像单片机一样是固定 ...

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- 串口接收端verilog代码分析

串口接收端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- verilog 代码分析与仿真

verilog 代码分析与仿真 注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值 边沿检测 module signal_test( input wire cmos_pcl ...

- FIFO 的控制逻辑---verilog代码

FIFO 的控制逻辑---verilog代码 //fifo的例化 wire fifo_full; wire fifo_empty; : ] fifo_dout; :]rd_data_count; :] ...

- [原创][FPGA]时钟分频之奇分频(5分频)

0. 简介 有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录. 1. 奇分频 其实现很简单,主要为使用两个 ...

- FPGA边沿检测Verilog代码

FPGA边沿检测Verilog代码(上升沿,下降沿,双边沿) 实现思路:用两个一位寄存器直接异或可以实现 代码实现: module edge_detect( input clk, input rs ...

随机推荐

- anaconda jupyter notebook修改默认文件路径

使用anaconda附带的jupyter,想要改变默认运行文件路径,直接在cmd中输入jupyter notebook会提示:jupyter不是内部命令! 可能是anaconda代理了他所安装的软件, ...

- REST是什么?

REST -- REpresentational State Transfer 直接翻译:表现层状态转移. @Ivony 老师的一句话概括很精辟: 用URL定位资源,用HTTP动词(GET,POS ...

- PaddlePaddle tutorial

什么是PaddlePaddle PaddlePaddle,百度旗下深度学习开源平台.Paddle(Parallel Distributed Deep Learning,并行分布式深度学习). 2016 ...

- web(四)html表单类标签

表单类标签 操作者用于输入信息,并将信息提交给服务器的标签集合. 表单标签介绍 form标签:表单元素(其余标签)标签的容器标签 input标签:用于用户信息输入的标签. button标签:按钮标签. ...

- 【转载】 Pytorch(0)降低学习率torch.optim.lr_scheduler.ReduceLROnPlateau类

原文地址: https://blog.csdn.net/weixin_40100431/article/details/84311430 ------------------------------- ...

- 【转载】 DeepMind用ReinforcementLearning玩游戏

原文地址: https://blog.csdn.net/wishchin/article/details/42425145 原文 : http://dataunion.org/?p=639 1.引言 ...

- 完整的AJAX

$.ajax({url:"请求路径",data:{"key":前端传入后台处理的数据},type:"post", //请求方式dataTyp ...

- spawn函数的实现(前文自动执行器的翻版)

function spawn(genF) { return new Promise(function(resolve, reject) { const gen = genF(); function s ...

- RPC 原理

转载地址:你应该知道的 RPC 原理 在校期间大家都写过不少程序,比如写个hello world服务类,然后本地调用下,如下所示.这些程序的特点是服务消费方和服务提供方是本地调用关系. 而一旦踏入公司 ...

- linux通过安装包安装nginx和jdk

1.安装prce(重定向支持)和openssl(https支持,如果不需要https可以不安装.) yum -y install pcre* yum -y install openssl* 2.下载n ...