外同步信号检测---verilog---状态机

外同步信号检测---verilog---状态机

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/02/08 11:39:20

// Design Name:

// Module Name: signal_detect

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module signal_detect #

(

parameter TOTAL_TIME_CNT = ,

parameter THRESHOLD_VALUE = ,

parameter WIDTH =

)

(

input wire clk,

input wire rst,

input wire signal,

output wire signal_existence

); //--------------------------------------------------------------

外部信号边沿检测

reg signal_delay_1;

reg signal_delay_2;

wire signal_rise;

always @(posedge clk or posedge rst)

begin

if( rst )

begin

signal_delay_1 <= 'b0;

signal_delay_2 <= 'b0;

end

else

begin

signal_delay_1 <= signal;

signal_delay_2 <= signal_delay_1;

end

end assign signal_rise = !signal_delay_2 && signal_delay_1; //----------------------------------------------------------------

计数器1 用来在第一个状态计数

reg [ WIDTH- : ] time_cnt_1;

always @(posedge clk or posedge rst)

begin

if( rst )

time_cnt_1 <= ;

else if( time_cnt_1 < TOTAL_TIME_CNT - && current_state == 'b01)

time_cnt_1 <= time_cnt_1 + 'b1;

else

time_cnt_1 <= ;

end //----------------------------------------------------------------

计数器2 用来在第二个状态计数

reg [ WIDTH- : ] time_cnt_2;

always @(posedge clk or posedge rst)

begin

if( rst )

time_cnt_2 <= ;

else if( time_cnt_2 < TOTAL_TIME_CNT - && current_state == 'b10)

time_cnt_2 <= time_cnt_2 + 'b1;

else

time_cnt_2 <= ;

end //----------------------------------------------------------------

计算第一个状态下 signal_rise 的脉冲个数

reg [ WIDTH- : ] i;

always @(posedge clk or posedge rst)

begin

if( rst )

i <= ;

else if ( time_cnt_1 == )

i <= ;

else if( signal_rise && current_state == 'b01)

i <= i + 'b1;

end //----------------------------------------------------------------

计算第二个状态下 signal_rise 的脉冲个数

reg [ WIDTH- : ] j;

always @(posedge clk or posedge rst)

begin

if( rst )

j <= ;

else if ( time_cnt_2 == )

j <= ;

else if( signal_rise && current_state == 'b10)

j <= j + 'b1;

end //---------------------------------------------------------------- localparam NO_SIGNAL = 'b01;

localparam HAVE_SIGNAL = 'b10; reg [:]current_state;

reg [:]next_state;

always @ (posedge clk or posedge rst)

begin

if( rst )

current_state <= NO_SIGNAL;

else

current_state <= next_state;

end //--------------------------------------------------------------

状态机跳变条件:

1.在NO_SIGNAL状态下,先是在一定时间段内,数脉冲的个数,当脉冲的个数大于了某个阈值时,立刻判断为,外同步信号存在。

2.在HAVE_SIGNAL状态下,同样也是数脉冲的个数,当一段时间内,脉冲总数量小于某个阈值时,则判断为外同步信号丢失,状态跳转到NO_SIGNAL状态

always @(*)

begin

next_state = NO_SIGNAL;

case( current_state ) NO_SIGNAL:

begin

if( i >= THRESHOLD_VALUE )

next_state = HAVE_SIGNAL;

else

next_state = NO_SIGNAL;

end HAVE_SIGNAL:

begin

if( (time_cnt_2 == TOTAL_TIME_CNT - ) && j < THRESHOLD_VALUE )

next_state = NO_SIGNAL;

else

next_state = HAVE_SIGNAL;

end endcase

end //-------------------------------------------------------------

状态机输出信号驱动

reg signal_existence_r;

always @(posedge clk or posedge rst)

begin

if (rst)

begin

signal_existence_r <= 'b0;

end

else

begin case( current_state ) NO_SIGNAL:

begin

signal_existence_r <= 'b0;

end HAVE_SIGNAL:

begin

signal_existence_r <= 'b1;

end endcase end

end assign signal_existence = signal_existence_r; endmodule /* add_force {/signal_detect/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/signal_detect/rst} -radix hex {1 0ns} {0 150ns}

add_force {/signal_detect/signal} -radix hex {0 0ns} {1 300ns} {0 400ns} -repeat_every 500ns */

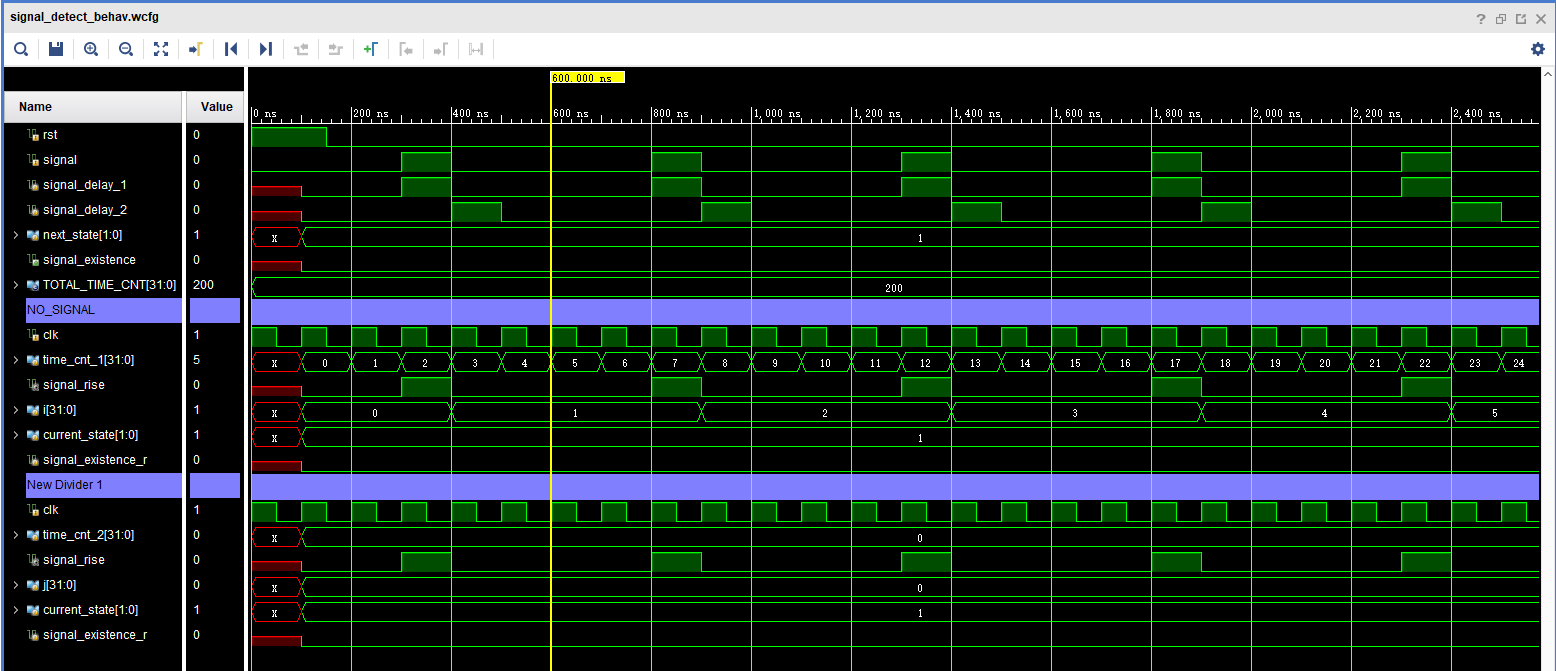

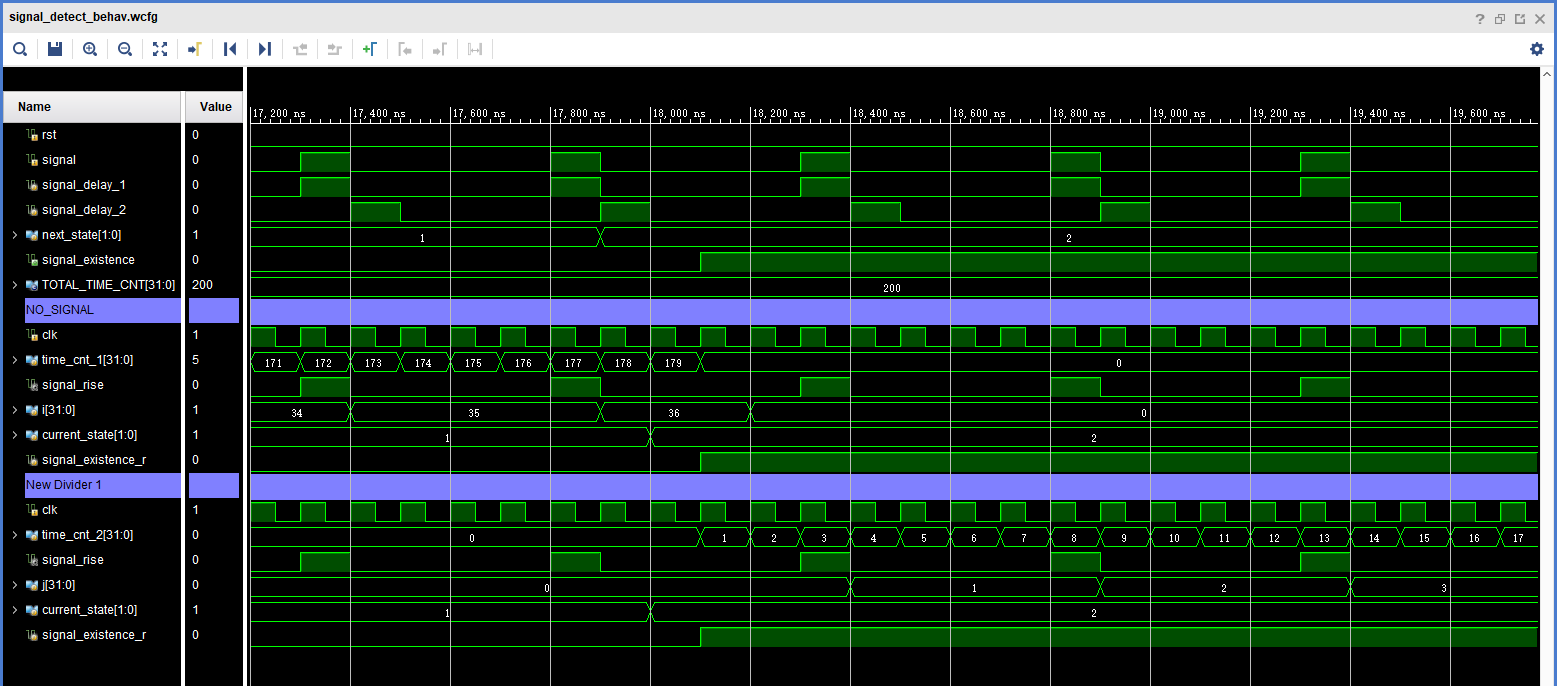

仿真波形:

1.

2.

3.

外同步信号检测---verilog---状态机的更多相关文章

- 视频外同步信号研究---fvh

视频外同步信号研究---fvh 一个时钟周期有两个edge,分别称为:(1)Leading edge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候:对于开始电压是0,那么就是0变成 ...

- C# 同步 异步 回调 状态机 async await Demo

源码 https://gitee.com/s0611163/AsyncAwaitDemo 为什么会研究这个? 我们项目的客户端和服务端通信用的是WCF,我就想,能不能用异步的方式调用WCF服务呢?或者 ...

- Verilog状态机使用技巧

“没有什么难处是通过增加一个状态机不能够解决的,如果不行,那就俩..” 在实现某种功能时,若感觉该功能的各种可能状态间的切换太绕了,此时,增加一个状态机往往能使思路变得清晰,功能的实现也就简单明了了. ...

- Verilog状态机

以1011为例 代码如下: //1011(Meay型) module state1(clk,in,rst_n,out); input clk; input rst_n; input in; outpu ...

- (原创)Verilog三段式状态机

下面以上图一个简单的FSM说明三段式Verilog状态机范式: `timescale 1ns / 1ps module FSM( clk,rst_n, in1,in2, out1,out2, CS,N ...

- RSync实现文件备份同步详解

1.rsync简介 rsync是Unix下的一款应用软件,它能同步更新两处计算机的文件与目录,并适当利用差分编码以减少数据传输.rsync中一项与其他大部分类似程序或协议中所未见的重要特性是镜像对每个 ...

- linux高级技巧:rsync同步(一个)

1.rsync基本介绍 rsync这是Unix下的一款应用软件,它能同步更新两处计算机的文件与文件夹,并适当利用差分编码以降低数据传输.rsync中一项与其它大部分类似程序或协议中所未 ...

- 160407、java实现多线程同步

多线程就不说了,很好理解,同步就要说一下了.同步,指两个或两个以上随时间变化的量在变化过程中保持一定的相对关系.所以同步的关键是多个线程对象竞争同一个共享资源. 同步分为外同步和内同步.外同步就是在外 ...

- [笔记][FPGA]有限状态机FSM学习笔记(三)

0. 简介 在数电FPGA中,FSM是一个重要的部分,藉此可以完成一些复杂算法的硬件实现等.其中有关于FSM的写法按照always块的个数来划分,又分为一段式.两段式.三段式状态机.顾名思义,一段式就 ...

随机推荐

- RESTful Web Service 架构

特点:简单,可靠,高效,跨平台和跨语言 含义: Web Service 简单来说是指提供给不同设备通过互联网(一般使用 HTTP 协议)进行通信和交换数据的一种服务.RESTful Web Servi ...

- [转]TCP滑动窗口详解

TCP滑动窗口详解 http://lyjdamzwf.blog.163.com/blog/static/75206837201193373226/ TCP滑动窗口(Sliding Window) ...

- phpStrom--我常用的快捷键

ALT+ ←/→ 切换代码视图,标签切换 ALT+ ↑/↓ 在方法间快速移动定位 ctrl+shift+r 查找 替换 alt+ctrl+l 格式化代码 CTRL+N 查找类 CTRL+W ...

- 通过javascript的日期对象来得到当前的日期,并输出--内置对象---JS

//通过javascript的日期对象来得到当前的日期,并输出. var mydate = new Date(); var week = ["星期日","星期一" ...

- 【err】VIDEOIO ERROR: V4L: index 0 is not correct!Unable to connect to camera

前言 新到手一块板子,程序编译成功之后,运行出现错误,不能连接到摄像头. 问题 VIDEOIO ERROR: V4L: index is not correct! Unable to connect ...

- fckeditor配置

<!DOCTYPE html> <html > <head> <title>发布</title> <meta name="v ...

- 环境变量、cp、mv、cat 等命令

1.环境变量: PATH 个人理解 环境变量,即是所有命令文件所存放的目录,或是人为的定义的目录,(命令文件所存放的目录,当输入一个命令的时候,系统会自动找到且不报错,并不需要输入绝对路径,来运行相关 ...

- java-Integer类

1.为什么会有基本类型包装类 * 将基本数据类型封装成对象的好处在于可以在对象中定义更多的功能方法操作该数据. 2.常用操作 * 常用的操作之一:用于基本数据类型与字符串之间的转换. * Intege ...

- python selenium自动化点击页面链接测试

python selenium自动化点击页面链接测试 需求:现在有一个网站的页面,我希望用python自动化的测试点击这个页面上所有的在本窗口跳转,并且是本站内的链接,前往到链接页面之后在通过后退返回 ...

- djjango cookie和session 的几种常用需求使用方法

------https://www.cnblogs.com/liuqingzheng/articles/8990027.html 需求情形一:正常设置cookie set_cookie(key,val ...