【FPGA】高斯白噪声的Verilog实现

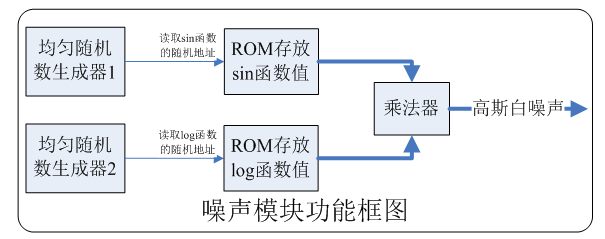

本文章主要讨论高斯白噪声的FPGA实现。简单的方法可以采用在Matlab中产生服从一定均值和方差的I、Q两路噪声信号。然后将两组数据存在FPGA中进行回放,以此来产生高斯白噪声。这种方法优点是产生方法简单占用FPGA资源少,但是他只能保证在回放噪声的一段数据是满足不相关特性的,段与段之间的数据是相关的。为了使整个过程中的噪声都满足不相关特性,可以通过LSFR序列的交错异或,得到均匀分布的伪随机信号,采用在一个ROM中存储sin函数值另一个ROM中存储log函数值。通过产生随机读地址的方式随机读取两个ROM中的数据,将两组随机的函数值相乘得到高斯白噪声。模块功能框图如下图。

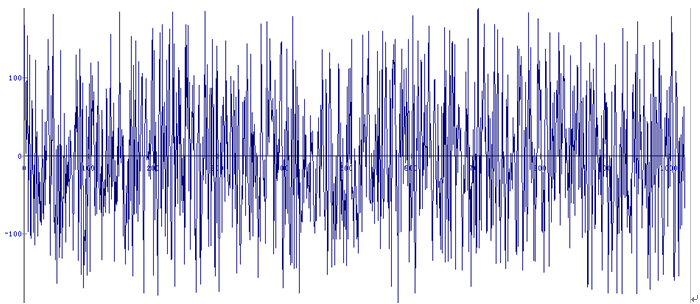

chipscope调试结果:

//////////////////////////////////////////////////////////////////////////////////

//////////////////////////////////////////////////////////////////////////////////子模块1

module rand_gen(

input wire clk100,

input wire rst,

output reg [:] orbit_sin_addr, //rand number for sin ROM addr, [10:]

output reg [:] orbit_log_addr //rand number for log ROM addr, [9:0]

);

wire resetup; // asynchronous clear, high active

wire [:] orbit_1;

wire [:] orbit_2;

wire [:] orbit_3;

wire [:] orbit_4;

parameter initval_1='b010110010010110111110001,

initval_2='b100000111100010111010001,

initval_3='b001101000001010010010001,

initval_4='b111010100110010011110001;

// 交错异或子模块

inter_feedback_rand_1 inter_feedback_rand_1_inst (

.orbit(orbit_1), //[10:0]

.clk(clk100),

.resetup(resetup),

.initval(initval_1) //[23:0]

);

//////////////////////////////////////////////////////////////////////////////////

inter_feedback_rand_2 inter_feedback_rand_2_inst (

.orbit(orbit_2), //[10:0]

.clk(clk100),

.resetup(resetup),

.initval(initval_2) //[23:0]

);

//////////////////////////////////////////////////////////////////////////////////

inter_feedback_rand_3 inter_feedback_rand_3_inst (

.orbit(orbit_3), //[9:0]

.clk(clk100),

.resetup(resetup),

.initval(initval_3) //[23:0]

);

//////////////////////////////////////////////////////////////////////////////////

inter_feedback_rand_4 inter_feedback_rand_4_inst (

.orbit(orbit_4), //[9:0]

.clk(clk100),

.resetup(resetup),

.initval(initval_4) //[23:0]

);

//////////////////////////////////////////////////////////////////////////////////

// orbit_sin_addr [10:0] //

//////////////////////////////////////////////////////////////////////////////////

always @ (posedge clk100 or posedge rst) begin

if(rst) begin

orbit_sin_addr <= 'b0;

end

else

orbit_sin_addr <= orbit_1 ^ orbit_2;

end

//////////////////////////////////////////////////////////////////////////////////

// orbit_log_addr [9:0 ] //

//////////////////////////////////////////////////////////////////////////////////

always @ (posedge clk100 or posedge rst) begin

if(rst) begin

orbit_log_addr <= 'b0;

end

else

orbit_log_addr <= orbit_3 ^ orbit_4;

end

//////////////////////////////////////////////////////////////////////////////////

// resetup //

//////////////////////////////////////////////////////////////////////////////////

reg resetup_r = 'b0;

assign resetup = resetup_r;

always @ (posedge clk100 or posedge rst) begin

if(rst)

resetup_r <= 'd1;

else

resetup_r <= 'd0;

end

endmodule

//////////////////////////////////////////////////////////////////////////////////

//////////////////////////////////////////////////////////////////////////////////子模块2

module noise_gen(

input wire clk100,

input wire rst,

input wire noise_en,

input wire [:] orbit_sin_addr,

input wire [:] orbit_log_addr,

output wire [:] noise_out

);

wire [:] sin_data;

wire [:] log_data;

// 正弦、对数、乘法IP核

Sin Sin_inst (

.clka(clk100), // input clka

.ena(noise_en), // input ena

.addra(orbit_sin_addr), // input [10 : 0] addra

.douta(sin_data) // output [7 : 0] douta

);

Log Log_inst (

.clka(clk100), // input clka

.ena(noise_en), // input ena

.addra(orbit_log_addr), // input [9 : 0] addra

.douta(log_data) // output [7 : 0] douta

);

Mult_signed Mult_signed_inst (

.clk(clk100), // input clk

.a(sin_data), // input [7 : 0] a

.b(log_data), // input [7 : 0] b

.ce(noise_en), // input ce

.sclr(rst), // input sclr

.p(noise_out) // output [15 : 0] p

);

endmodule

//////////////////////////////////////////////////////////////////////////////////

//////////////////////////////////////////////////////////////////////////////////顶层模块(部分)

rand_gen rand_gen_inst_1 (

.clk100(clk100),

.rst(rst),

.orbit_sin_addr(orbit_sin_addr_1),

.orbit_log_addr(orbit_log_addr_1)

);

noise_gen noise_gen_inst_1 (

.clk100(clk100),

.rst(rst),

.noise_en(noise_en),

.orbit_sin_addr(orbit_sin_addr_1),

.orbit_log_addr(orbit_log_addr_1),

.noise_out(noise_out_1)

);

/////////////////////////////////////////////////////////////////////////////////feedback1

`define FEXPR sr_a[]^(sr_a[]^(sr_a[]^sr_a[]))

module inter_feedback_rand_1(

output wire [:] orbit,

input wire clk,

input wire resetup, //置数,高电平有效

input wire [:] initval

);

reg[:] sr_a;

assign orbit[:]=sr_a[:];

always@(posedge clk or posedge resetup)

begin

if(resetup)

sr_a<=initval;

else

begin

sr_a[:]<=sr_a[:];

sr_a[]<=`FEXPR;

end

end

endmodule

`undef FEXPR

/////////////////////////////////////////////////////////////////////////////////feedback2

`define FEXPR sr_a[]^(sr_a[]^(sr_a[]^sr_a[]))

module inter_feedback_rand_2(

output wire [:] orbit,

input wire clk,

input wire resetup, //置数,高电平有效

input wire [:] initval

);

reg[:] sr_a;

assign orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[];

always@(posedge clk or posedge resetup)

begin

if(resetup)

sr_a<=initval;

else

begin

sr_a[:]<=sr_a[:];

sr_a[]<=`FEXPR;

end

end

endmodule

`undef FEXPR

/////////////////////////////////////////////////////////////////////////////////feedback3

`define FEXPR sr_a[]^(sr_a[]^(sr_a[]^sr_a[]))

module inter_feedback_rand_3(

output wire [:] orbit,

input wire clk,

input wire resetup, //置数,高电平有效

input wire [:] initval

);

reg[:] sr_a;

assign orbit=sr_a[:];

always@(posedge clk or posedge resetup)

begin

if(resetup)

sr_a<=initval;

else

begin

sr_a[:]<=sr_a[:];

sr_a[]<=`FEXPR;

end

end

endmodule

`undef FEXPR

/////////////////////////////////////////////////////////////////////////////////feedback4

`define FEXPR sr_a[]^(sr_a[]^(sr_a[]^sr_a[]))

module inter_feedback_rand_4(

output wire [:] orbit,

input wire clk,

input wire resetup, //置数,高电平有效

input wire [:] initval

);

reg[:] sr_a;

assign orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[],

orbit[]=sr_a[];

always@(posedge clk or posedge resetup)

begin

if(resetup)

sr_a<=initval;

else

begin

sr_a[:]<=sr_a[:];

sr_a[]<=`FEXPR;

end

end

endmodule

`undef FEXPR

转载请声明出处,谢谢。

【FPGA】高斯白噪声的Verilog实现的更多相关文章

- Matlab实现加性高斯白噪声信道(AWGN)下的digital调制格式识别分类

Matlab实现加性高斯白噪声信道(AWGN)下的digital调制格式识别分类 内容大纲 加性高斯白噪声信道(AWGN)下的digital调制格式识别分类 (1. PSK; 2. QPSK; 3.8 ...

- [转] Matlab中给信号加高斯白噪声的方法

MATLAB中产生高斯白噪声非常方便,可以直接应用两个函数,一个是WGN,另一个是AWGN.WGN用于产生高斯白噪声,AWGN则用于在某一信号中加入高斯白噪声. 1. WGN:产生高斯白噪声 y = ...

- 高斯白噪声(white Gaussian noise,WGN)

本文科普一下高斯白噪声(white Gaussian noise,WGN). 百度百科上解释为“高斯白噪声,幅度分布服从高斯分布,功率谱密度服从均匀分布”,听起来有些晦涩难懂,下面结合例子通俗而详细地 ...

- MATLAB中产生高斯白噪声的两个函数

MATLAB中产生高斯白噪声非常方便,可以直接应用两个函数,一个是WGN,另一个是AWGN.WGN用于产生高斯白噪声,AWGN则用于在某一信号中加入高斯白噪声.1.WGN:产生高斯白噪声 y = wg ...

- FPGA按键去抖verilog代码

按键去抖的原因及其分类就不罗嗦了. 在这里解释一段代码,代码是网上找的,看了半天没懂,无奈查了半天想了半天,终于明白了... module sw_debounce(clk,rst_n,sw1,sw2, ...

- FPGA 状态机-序列检测器verilog

实现功能:检测出串行输入数据4位Data二进制序列0101,当检测到该序列的时候,out=1,否则out=0 (1)给出状态编码,画出状态图 (2)门电路实现 (3)verilog实现 首先规定Q3Q ...

- 【FPGA篇章三】FPGA常用语句:Verilog基本语法要素

欢迎大家关注我的微信公众账号,支持程序媛写出更多优秀的文章 Verilog中总共有十九种数据类型,我们先介绍四个最基本的数据类型,他们是: reg型.wire型.integer型.parameter型 ...

- 【MATLAB】对离散采样信号添加高斯白噪声(已知Eb/N0)

(1)首先计算已知信号序列(采样之后得到的信号)的平均功率.该序列在第n个点处的功率为: 如果已知的信号序列中的总共的点数为N个,则该序列的平均功率为: 在MATLAB中求平均功率的方法是: Pav= ...

- python 写matlab中的加性高斯白噪声AWGN

定义 原始信号:x 噪声信号:n 信噪比:SNR 信号长度:N def wgn(x, snr): snr = 10**(snr/10.0) xpower = np.sum(x**2)/len(x) n ...

随机推荐

- 关于centos 7 systemctl自定义服务笔记

通过添加 Restart=always RestartSec=2s StartLimitBurst=10 实现systemctl服务崩溃自动重启

- java多线程基本概述(二十)——中断

线程中断我们已经直到可以使用 interrupt() 方法,但是你必须要持有 Thread 对象,但是新的并发库中似乎在避免直接对 Thread 对象的直接操作,尽量使用 Executor 来执行所有 ...

- python3和python2的区别部分

字典没有iteritems(),只有items() py2items()返回的是列表,iteritems()返回的是迭代器 py3items()返回的是迭代器

- java进制转换(无视正负数的差别)

最近看了一下学习资料,感觉进制转换其实还是挺有意思的,尤其是对于负数这一方面. 下面和大家分享一下,这里只写了十进制到二进制的转换,其实都是同样的道理 public class Test1 { pub ...

- 用Visual Studio2017写静态库

造轮子是一件有趣的事情,VS是一个强大的工具,能胜任超大规模的工程,但是讲真,对不那么大的项目配置起来不是那么友好(网上的其他教程也一点都不友好Orz).这里就展示一下构建一个简单的静态库的正确姿势. ...

- MySQL安装、输入密码闪退、workbench使用

1.安装 安装就不细说了,网上一搜一大堆,但是教程推荐这个: wikihow 网站是wikiHOW,很有意思的网站,比百度经验强大很多. 2.输入密码闪退 安装完成后,在开始菜单,打开 开始程序 界面 ...

- ASP.NET WebForm

ASP.NET WEBFORM Aspx aspx文件(新建项→Web窗体) .在aspx中可以使用<%=表达式%>的方式在页面的当前位置输出表达式(表达式至少要用protected级别, ...

- 详解全站 HTTPS 访问优化

HTTPS 协议就是 HTTP+SSL/TLS,即在 HTTP 基础上加入 SSL /TLS 层,提供了内容加密.身份认证和数据完整性3大功能,目的就是为了加密数据,用于安全的数据传输. HTTPS ...

- FME中通过HTMLExtractor向HTML要数据

如何不断扩充数据中心的数据规模,提升数据挖掘的价值,这是我们思考的问题,数据一方面来自于内部生产,一部分数据可以来自于互联网,互联网上的数据体量庞大,形态多样,之前blog里很多FMEer已经提出了方 ...

- ReactiveCocoa学习总结(1)

1. 它是什么? 官方解释: [RACSignal] is a push-driven stream with a focus on asynchronous event delivery throu ...