FPGA —— LED控制

第一次接触新东西的时候,难免会磕磕碰碰,不过遇到问题不要着急,慢慢来。原因总归是我们自己引起的,一步步找到问题的根源,然后彻底解决它,避免下次再犯。

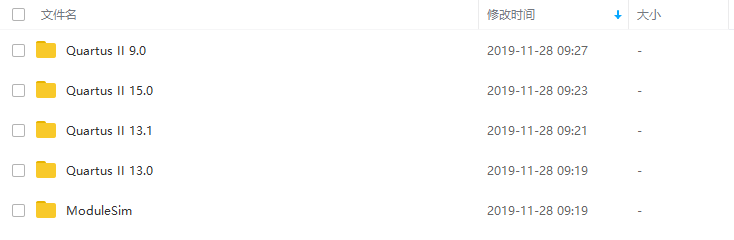

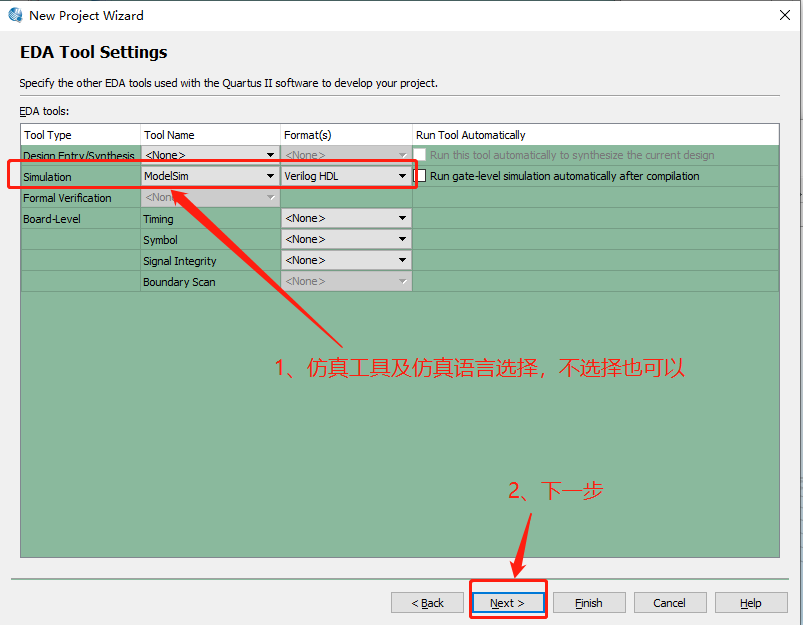

在开始之前先分享一下工具:(Quartus II 9.0、Quartus II 13.0、Quartus II 13.1、Quartus II 15.0、相应版本的器件库、Modulesim)

链接:https://pan.baidu.com/s/1RfwdpcfD5gmHJvndAgxh0A

提取码:0q8x

接下来进入正题

目标:创建 Quartus II 第一个工程 —— LED控制

开发环境:Quartus II 15.0.0.145 64Bit

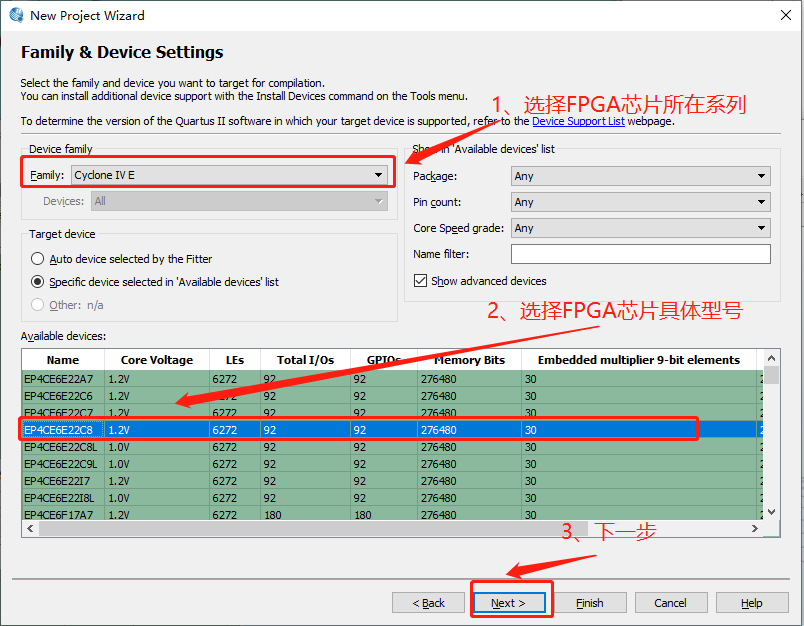

FPGA芯片:EP4CE6E22C8N

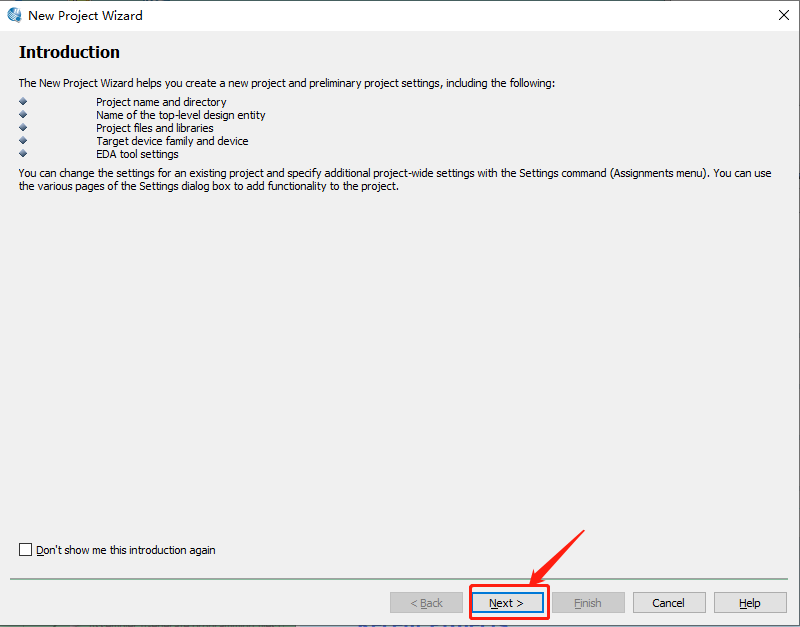

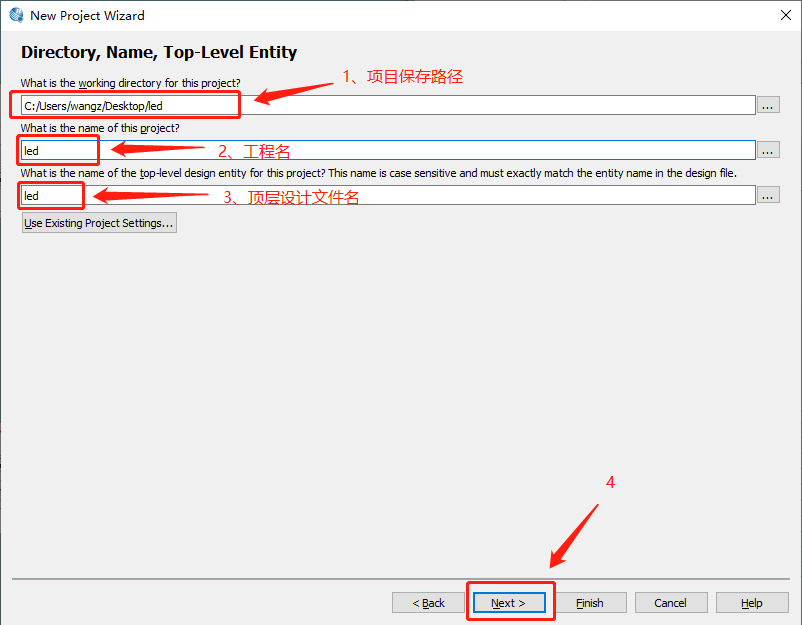

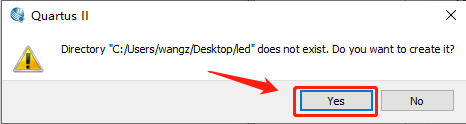

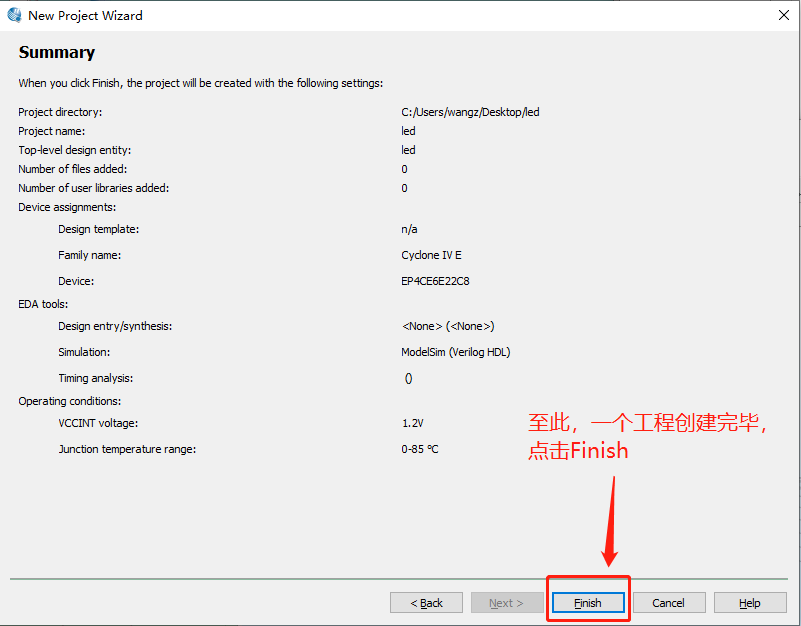

第一步:创建工程,打开Quartus II软件,选择 File->New Project Wizard,如下图:

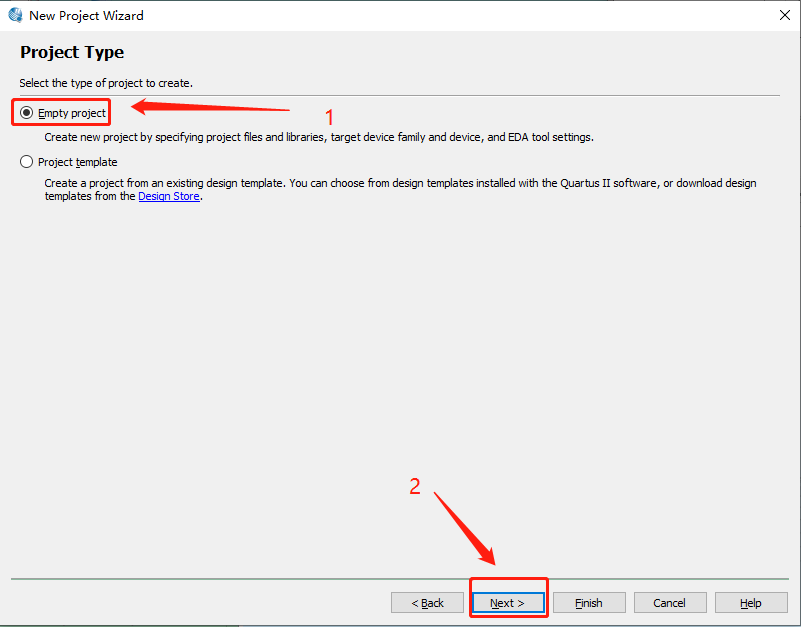

下面选择创建一个空的工程

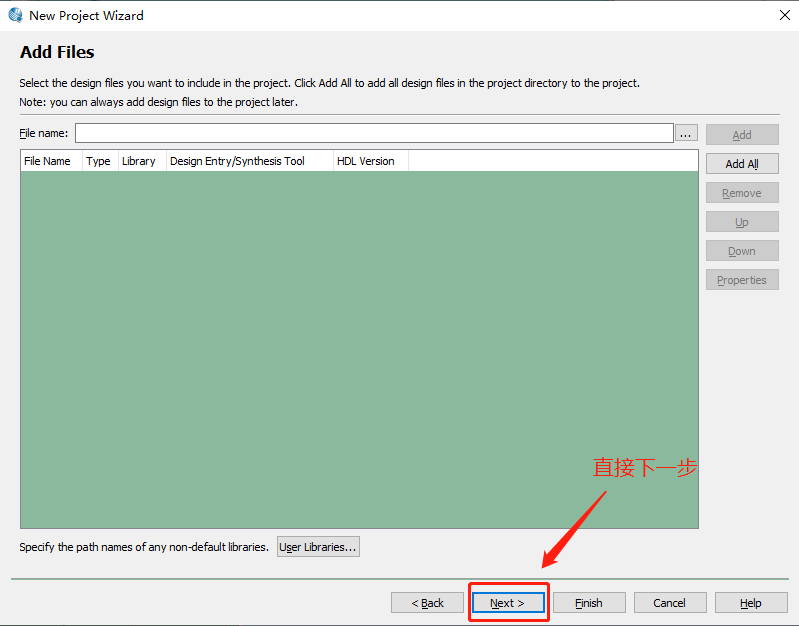

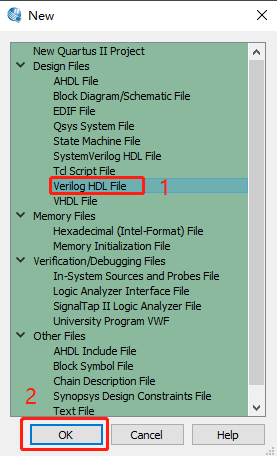

工程创建完毕,接下来就是添加代码文件,在菜单栏选择 File->New

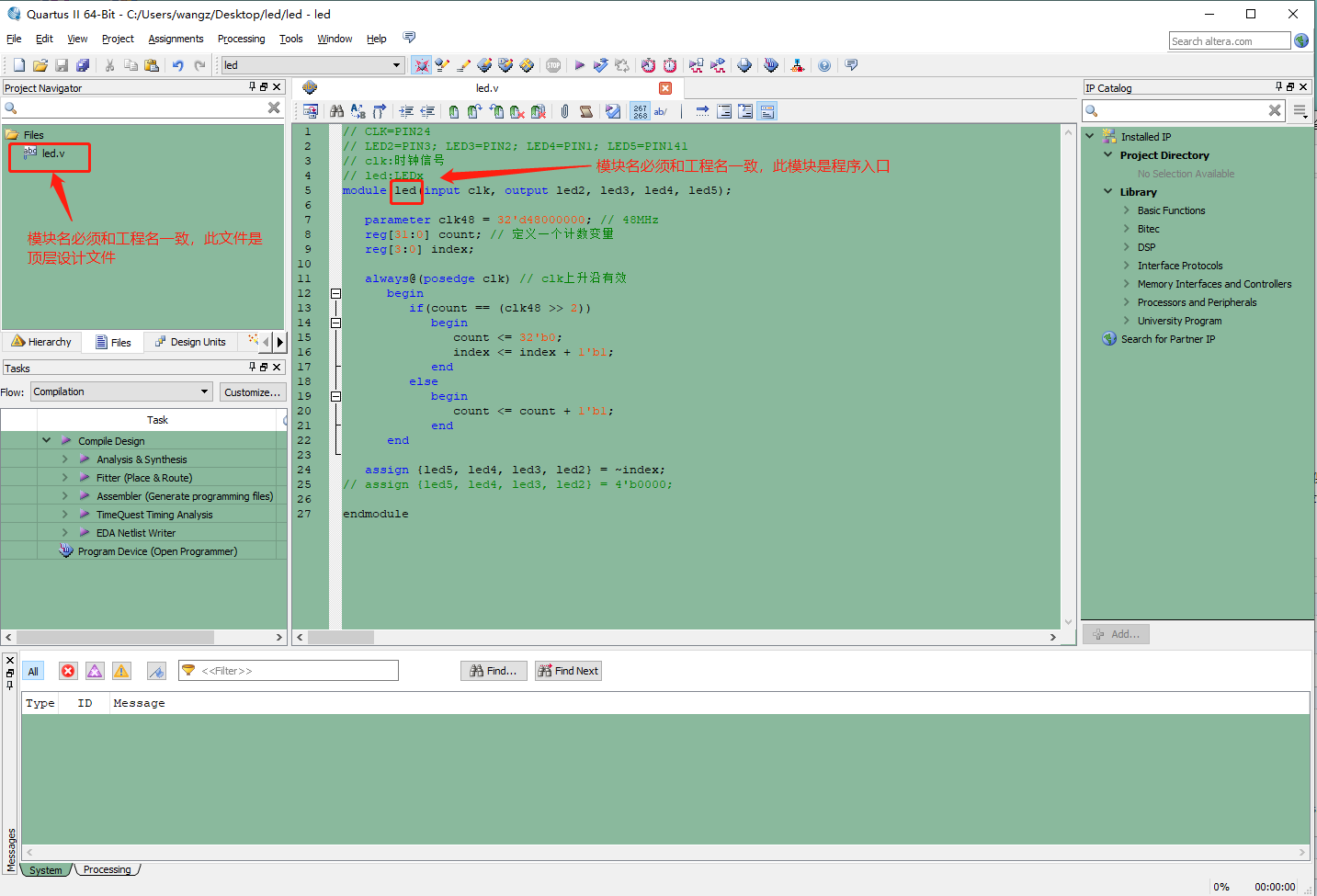

这里我选择的是Verilog HDL语言,文件创建完成后,向文件中添加代码,并保存。注意:保存的时候文件名必须和工程名一致。

我们都知道在单片机中程序入口函数是main函数,但是Quartus II不一样,在Quartus II的工程中必须要有一个顶层设计文件,并且顶层设计文件中的模块名必须和工程名一致。

顶层设计文件名也必须和工程名一致,而这个顶层设计文件中和工程同名的模块就是程序入口。

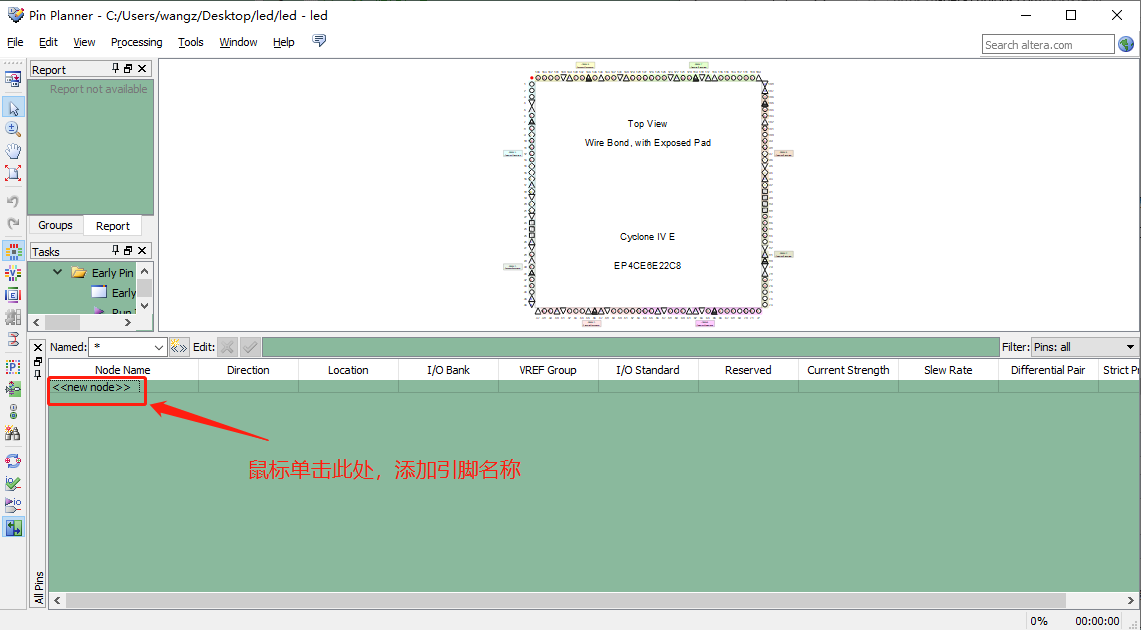

在单片机中要控制LED就必须要指定IO,并初始化IO,在这里IO不需要我们去初始化,我们只要指定就好了。

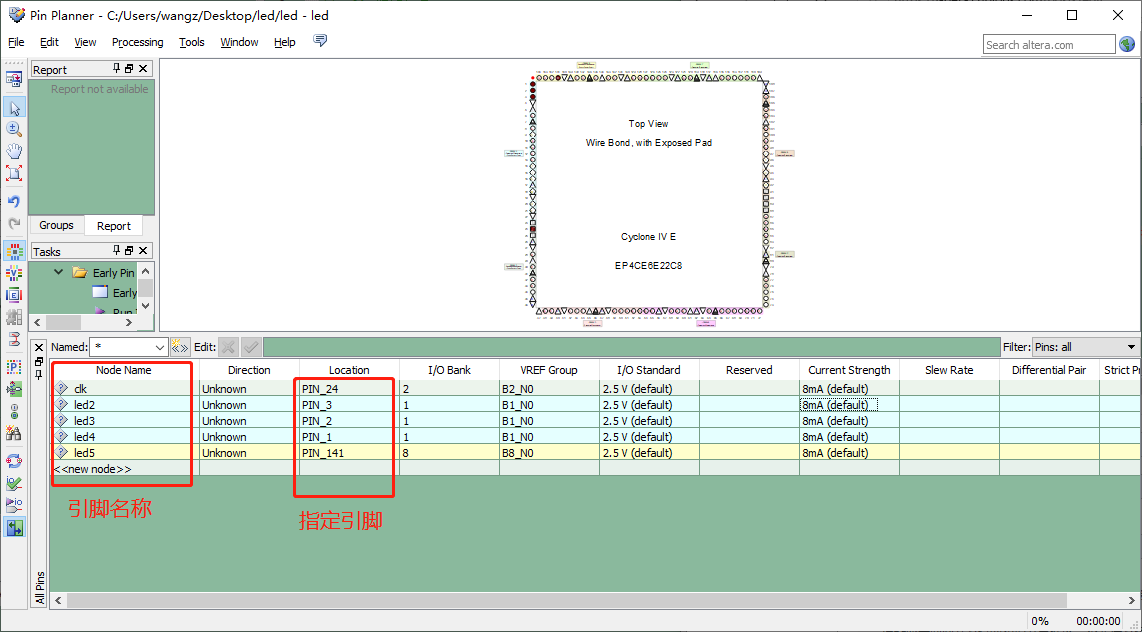

使用快捷键 Ctrl + Shift + N 打开引脚分配窗口,或者菜单栏 Assignments -> Pin Planner 打开引脚分配窗口。

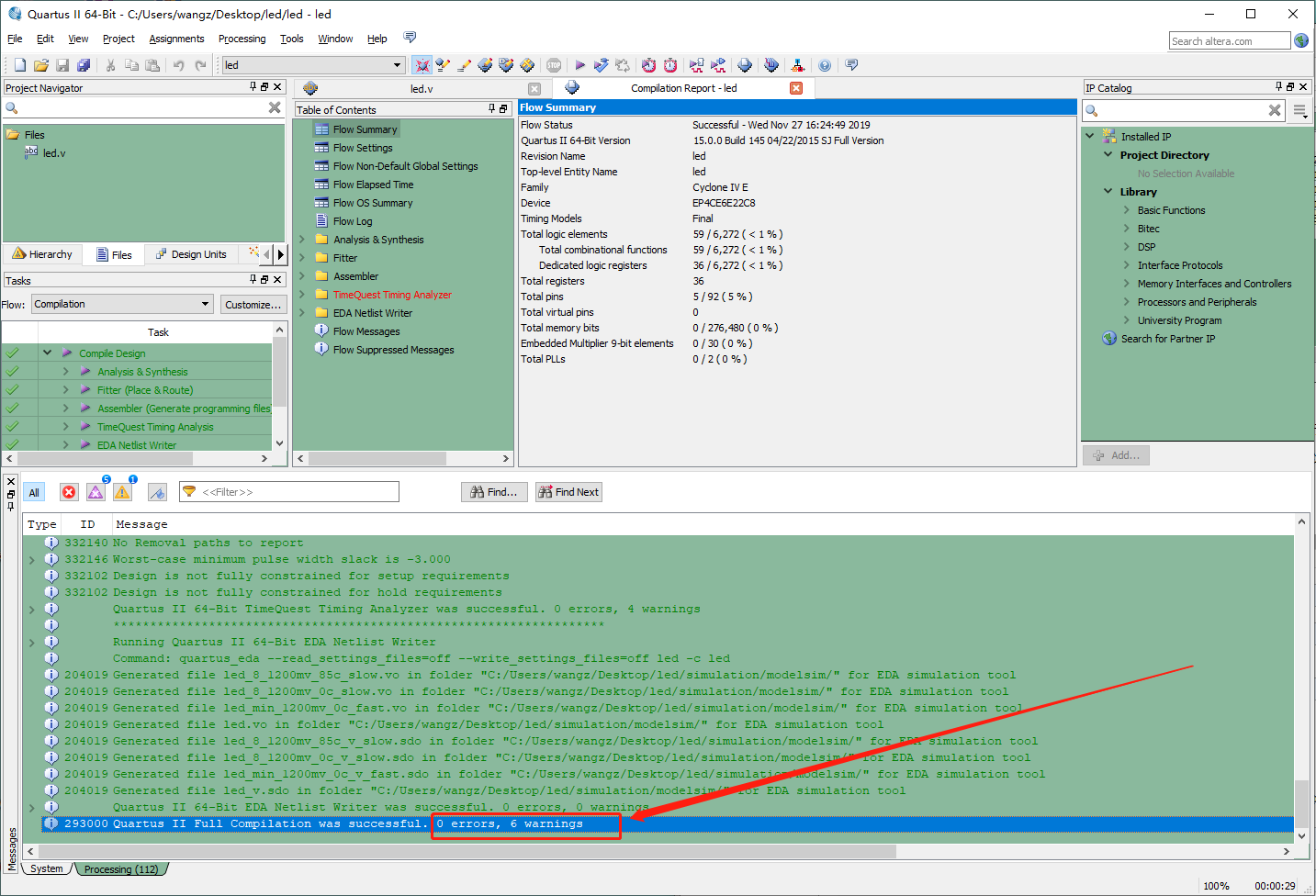

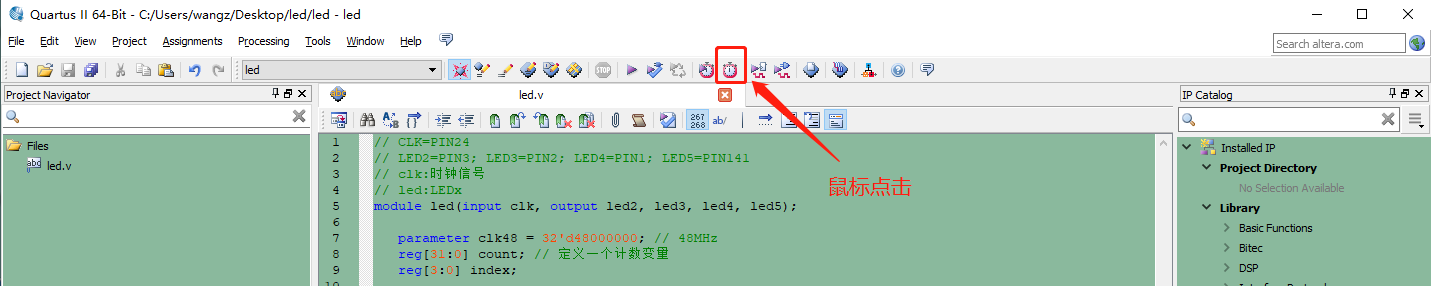

OK启动编译。编译结果:Info (293000): Quartus II Full Compilation was successful. 0 errors, 6 warnings

第一个警告:Warning (15714): Some pins have incomplete I/O assignments. Refer to the I/O Assignment Warnings report for details

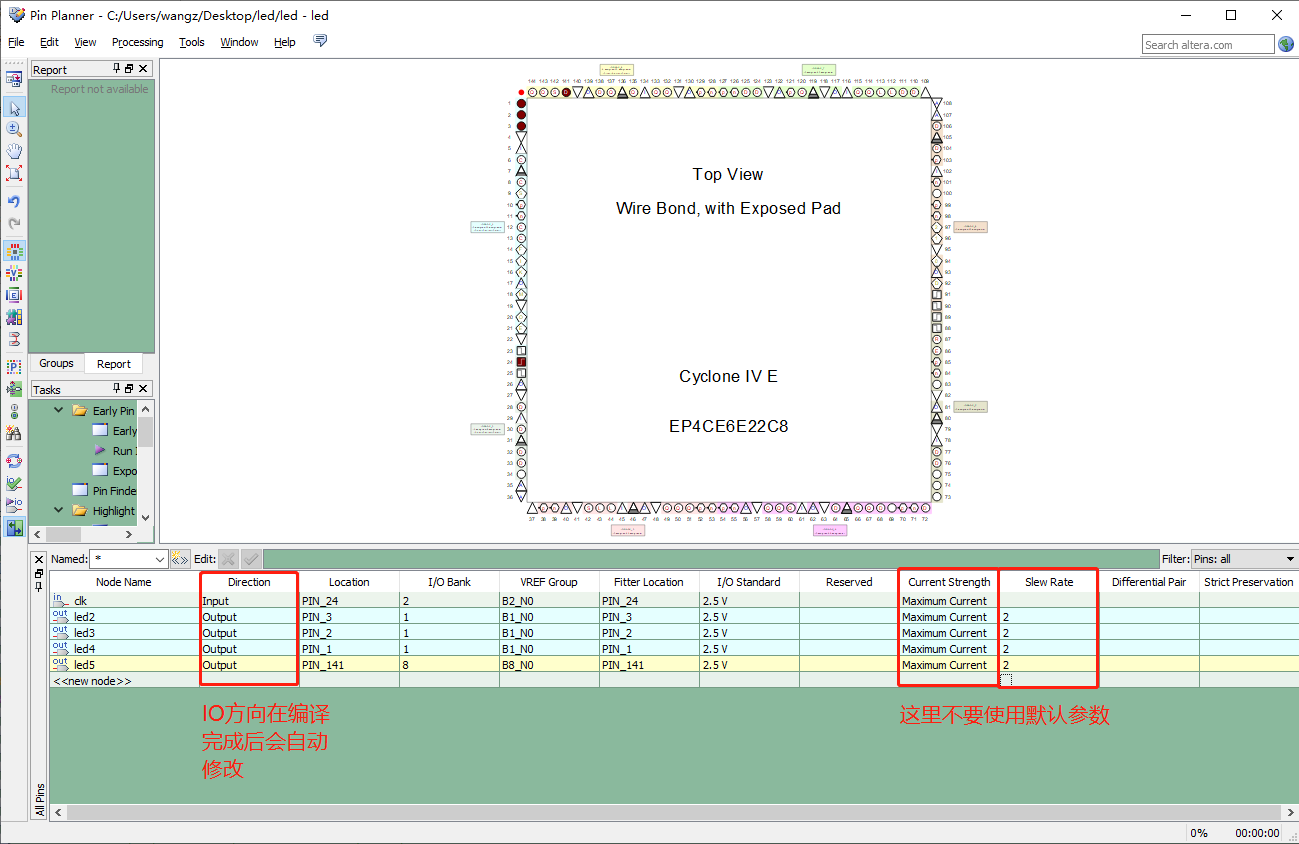

这个警告的意思是IO参数配置不完整,解决方法如下:

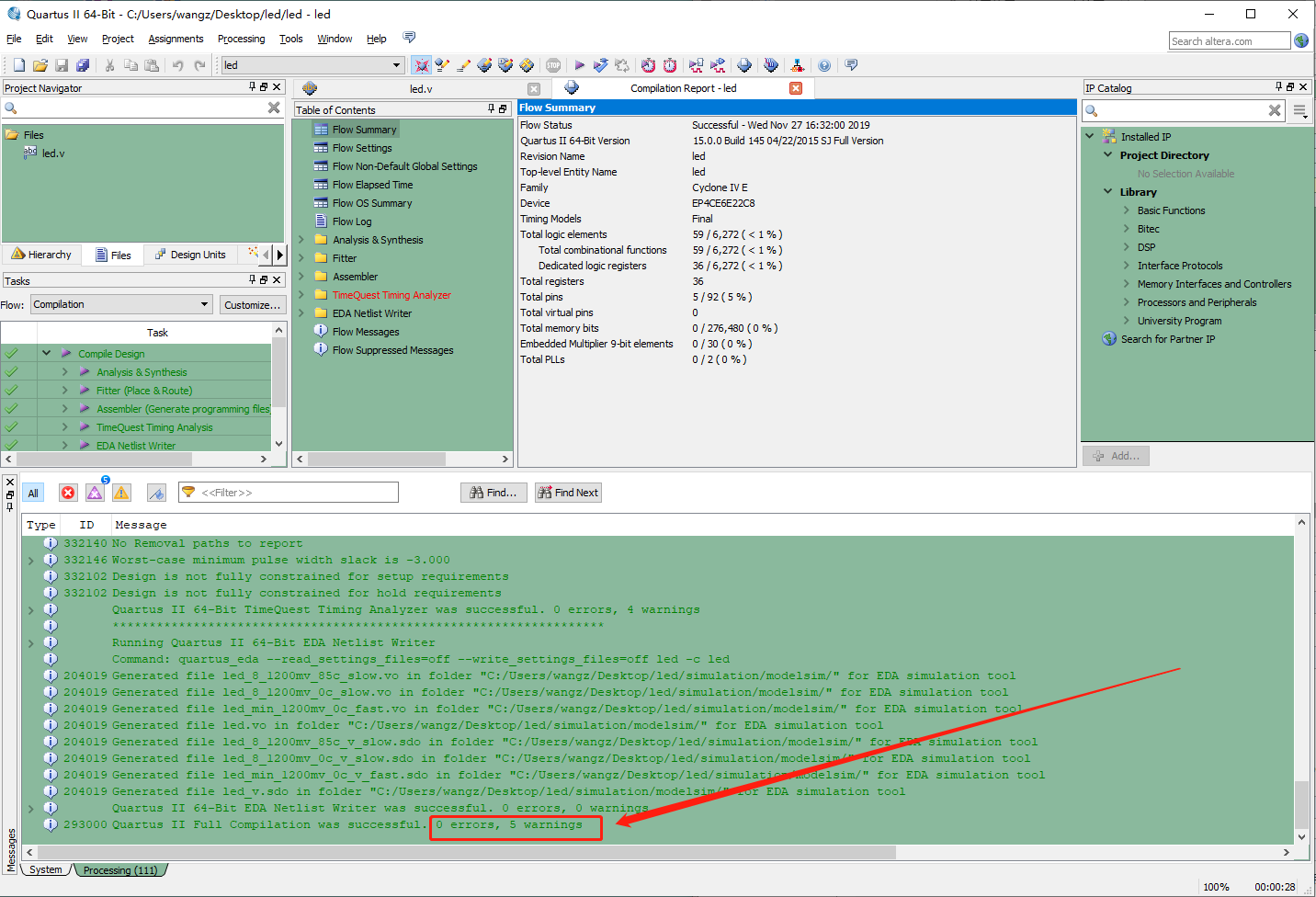

执行编译,编译后还有五个警告。

警告信息如下:

1、Critical Warning (332012): Synopsys Design Constraints File file not found: 'led.sdc'. A Synopsys Design Constraints File is required by the TimeQuest Timing Analyzer to get proper timing constraints. Without it, the Compiler will not properly optimize the design.

2、Critical Warning (332012): Synopsys Design Constraints File file not found: 'led.sdc'. A Synopsys Design Constraints File is required by the TimeQuest Timing Analyzer to get proper timing constraints. Without it, the Compiler will not properly optimize the design.

3、Critical Warning (332148): Timing requirements not met

4、Critical Warning (332148): Timing requirements not met

5、Critical Warning (332148): Timing requirements not met

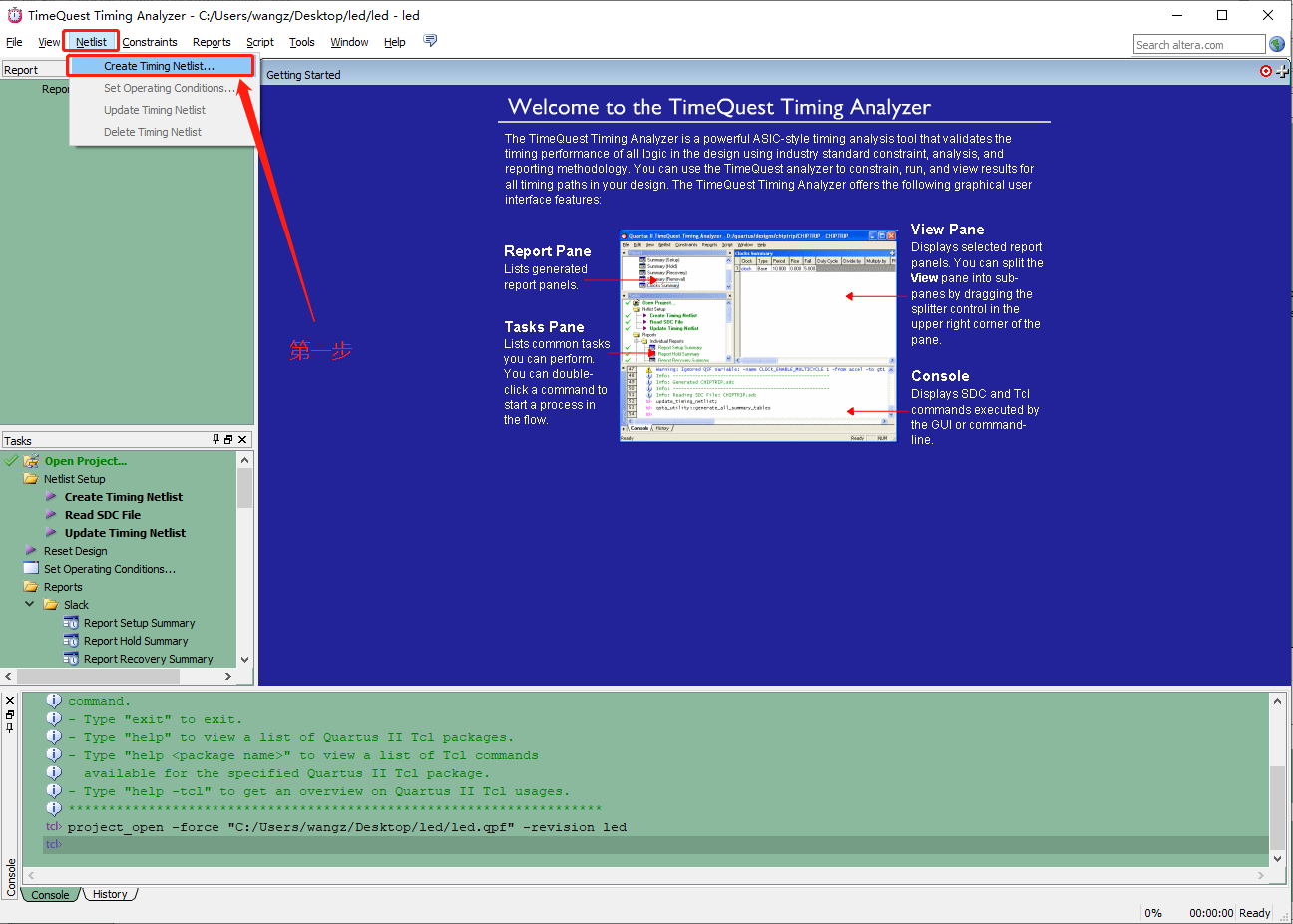

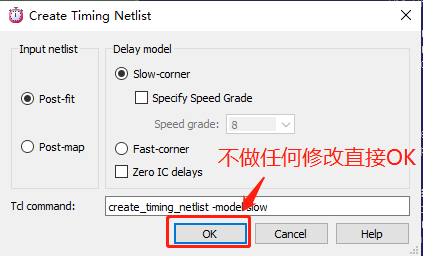

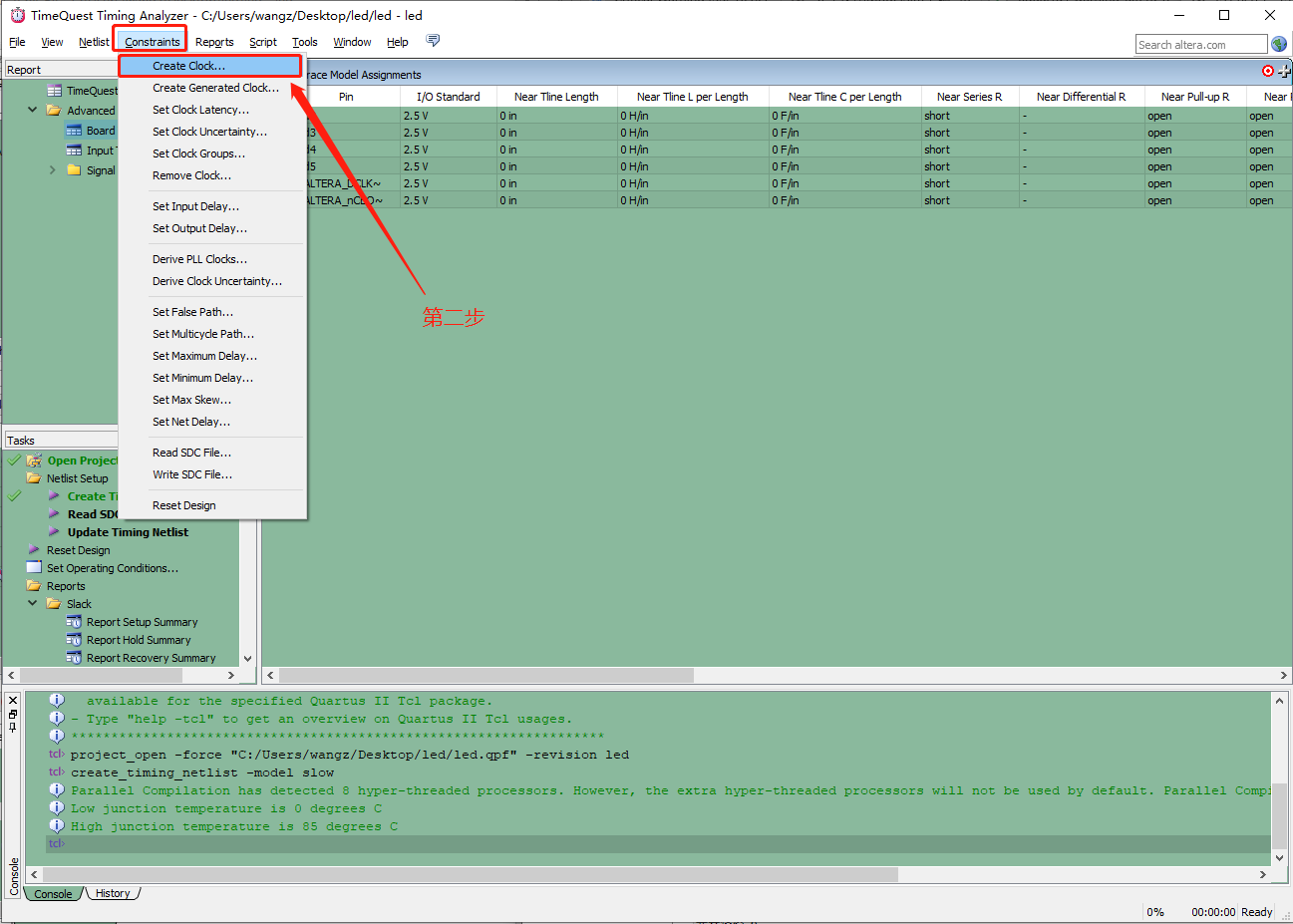

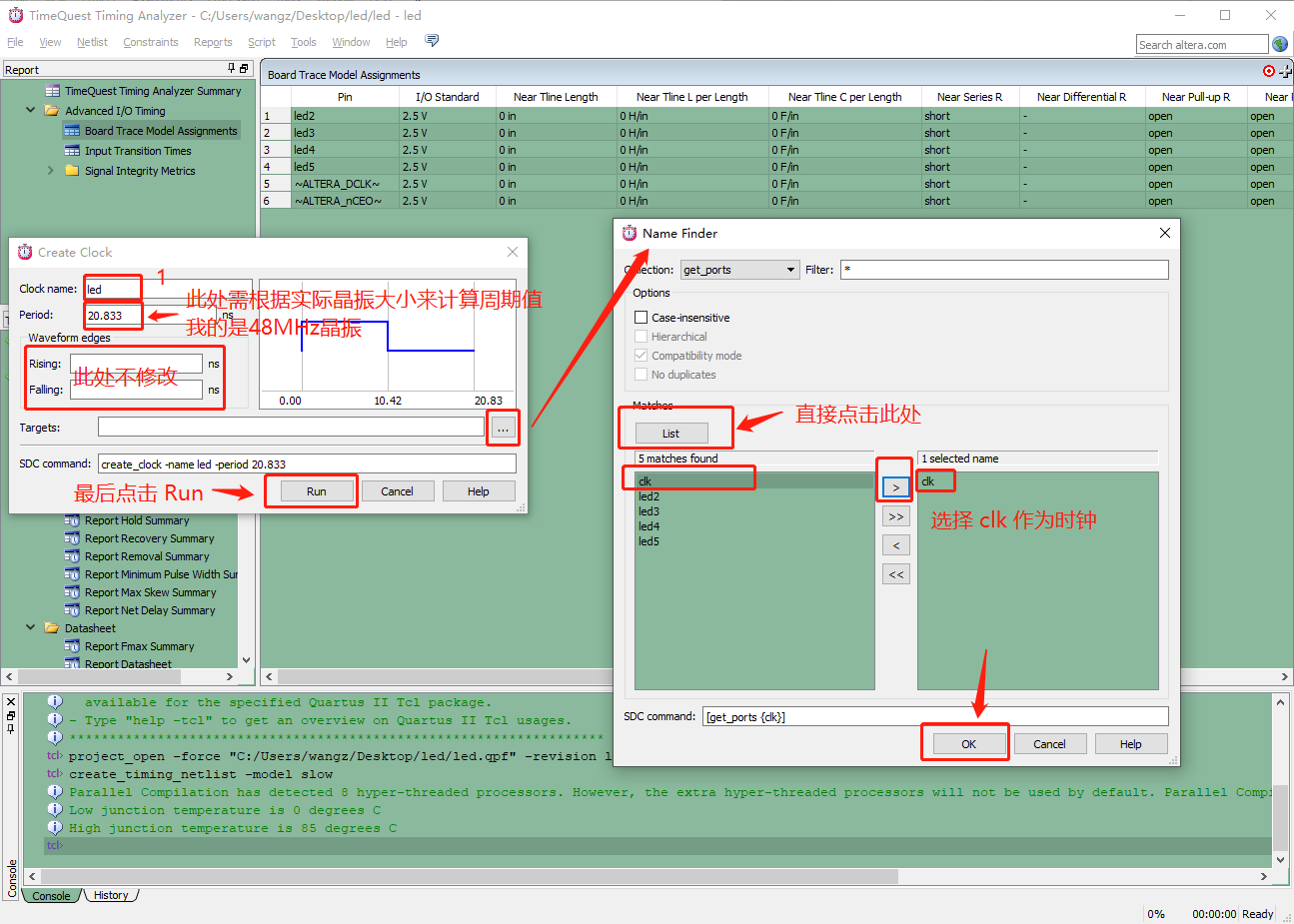

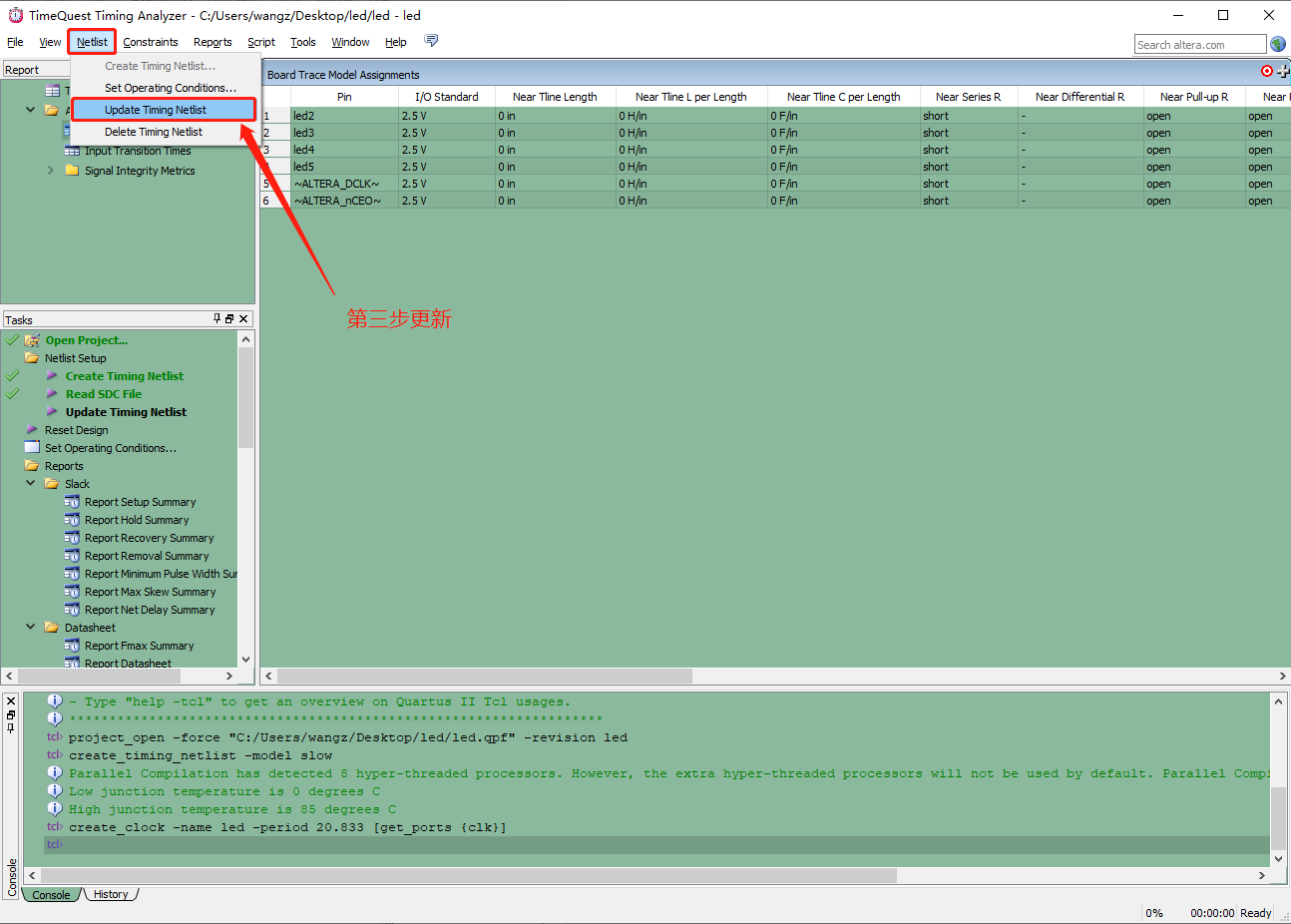

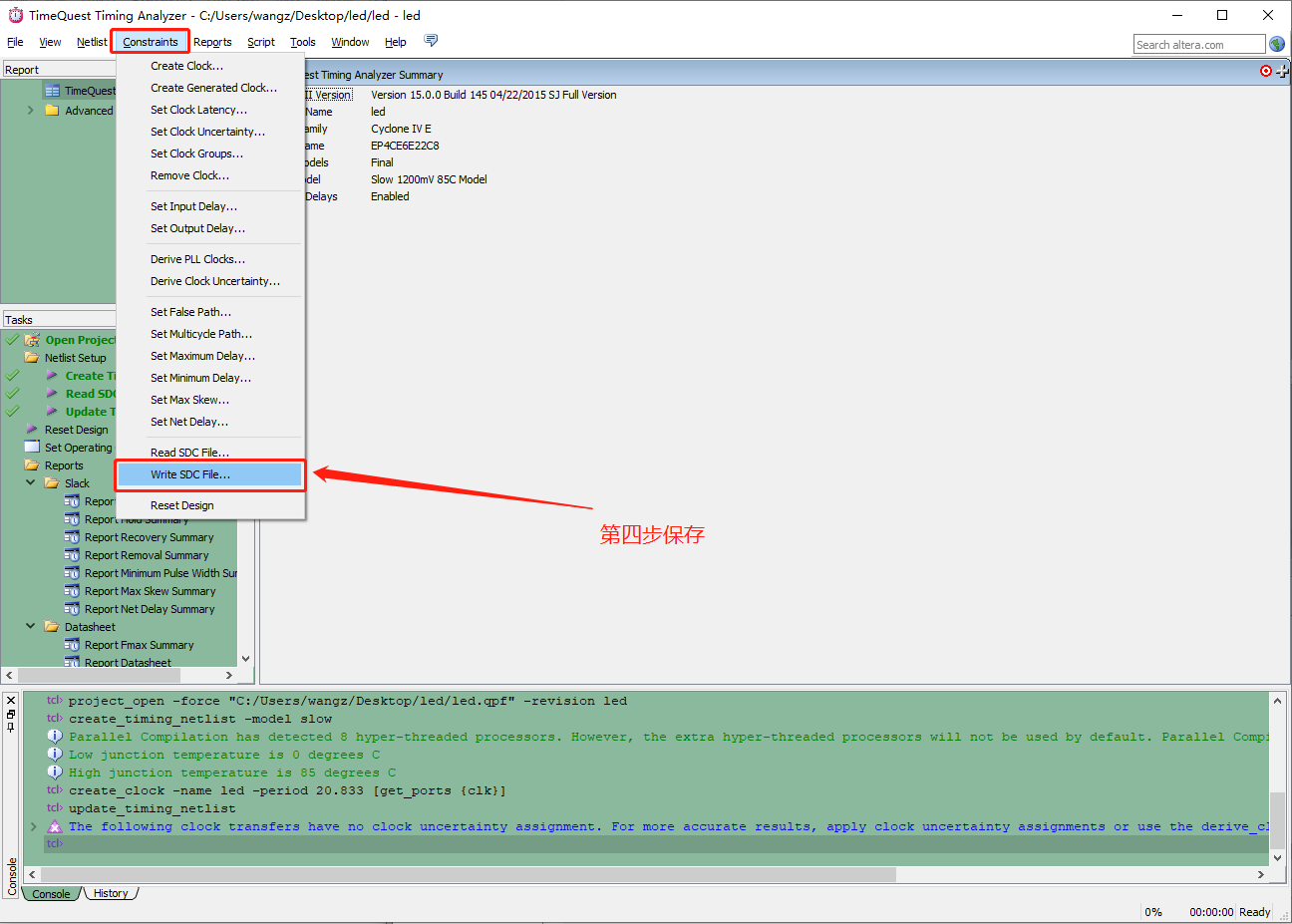

以上警告信息其实是一个时钟约束的问题所导致的,问题解决方法如下:

关闭窗口,再编译一次,编译后发现结果与理想中的不一样,警告信息如下:

1、Critical Warning (332168): The following clock transfers have no clock uncertainty assignment. For more accurate results, apply clock uncertainty assignments or use the derive_clock_uncertainty command.

2、 Critical Warning (332169): From led (Rise) to led (Rise) (setup and hold)

警告信息:时钟传输没有时钟不确定性分配。要获得更精确的结果,请应用时钟不确定性分配或使用derive_clock_uncertainty命令。解决方法如下:

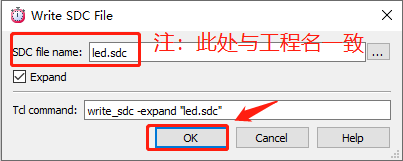

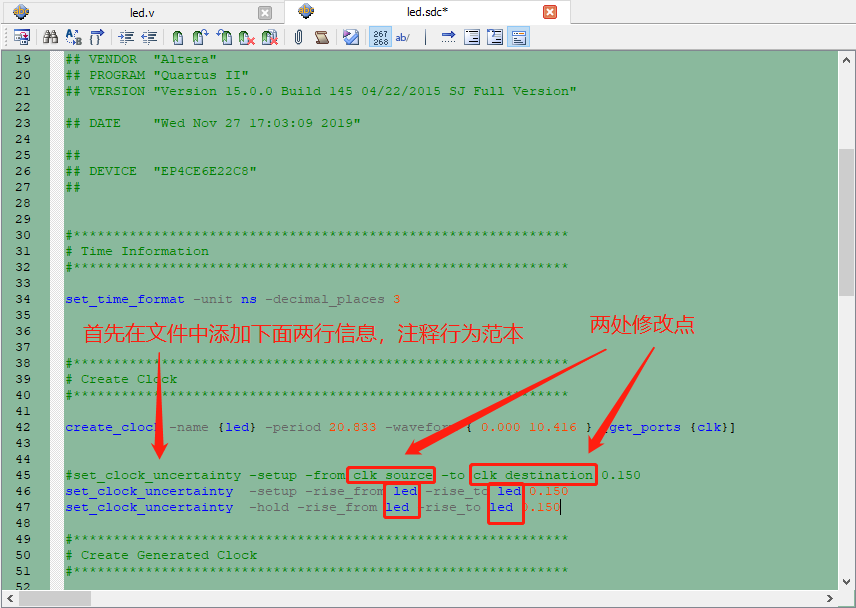

打开我们刚保存的 led.sdc 文件,该文件就在工程目录下,然后添加两行信息,并将 clk_source 和 clk_destination 改为自己设置的 Clock name(第二步中 Create Clock 窗口中设置的 Clock name,我设置的 Clock name 是 led)。

添加信息如下:

#set_clock_uncertainty -setup -from clk_source -to clk_destination 0.150

set_clock_uncertainty -setup -rise_from led -rise_to led 0.150

set_clock_uncertainty -hold -rise_from led -rise_to led 0.150

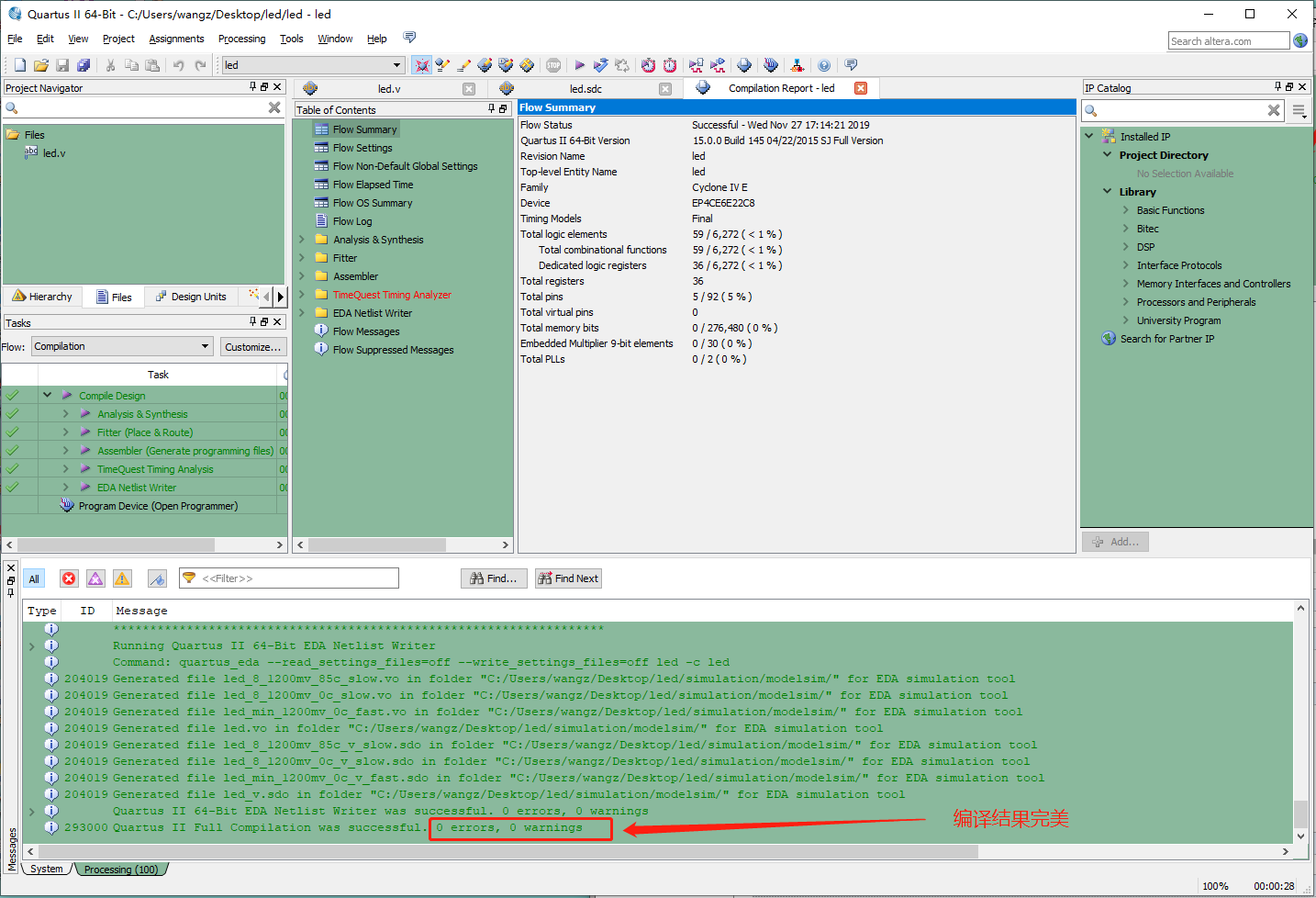

保存文件再编译,编译结果如下:

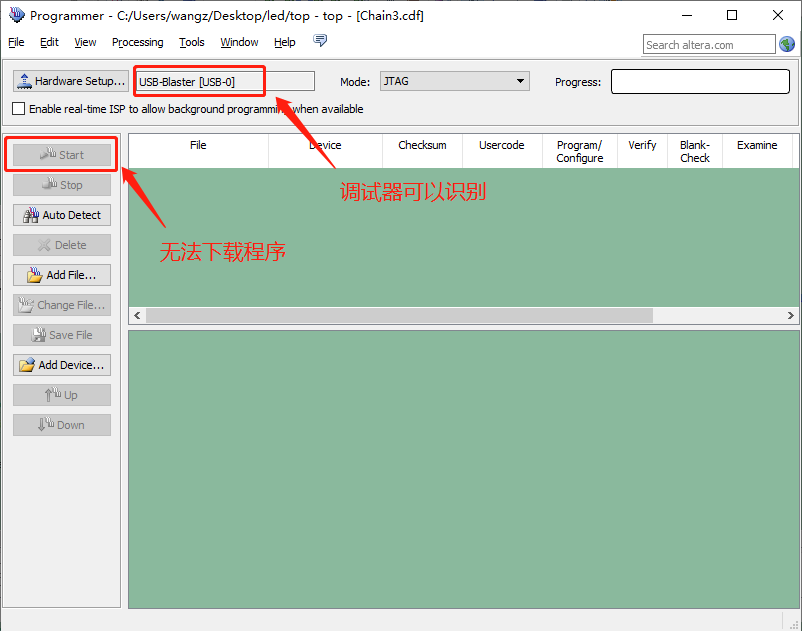

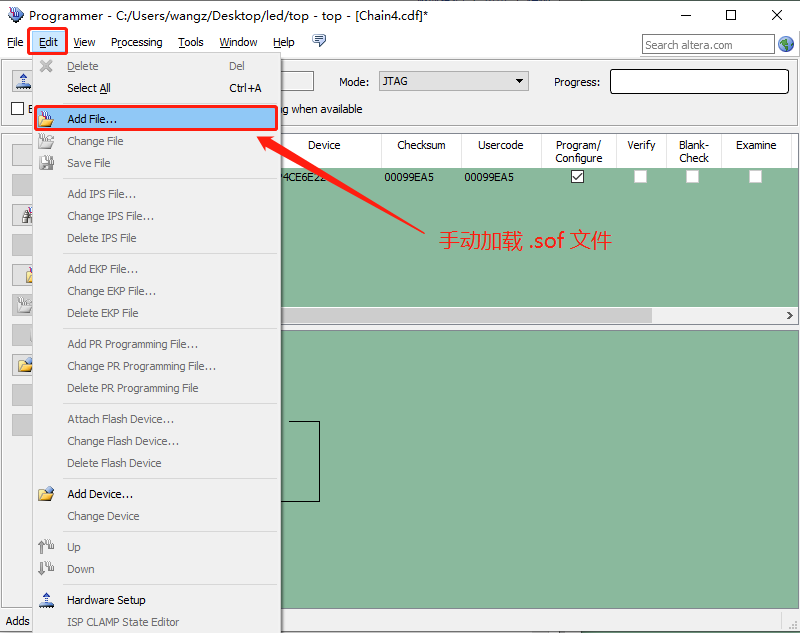

修改后编译警告没有了,打开下载窗口下载程序。此时发现可以识别调试器,但是 Start 按钮是灰色的,无法点击。

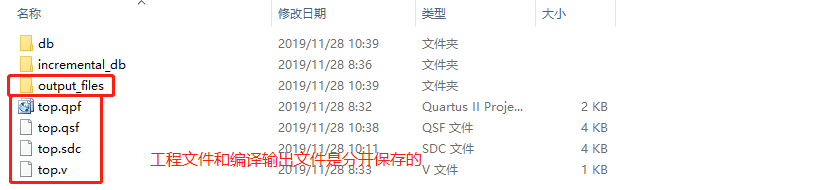

导致这个问题的原因是 Programmer 软件只会查找工程文件所在路径,当生成文件和工程文件不在同一路径下,就会导致这一问题。

解决方法如下:

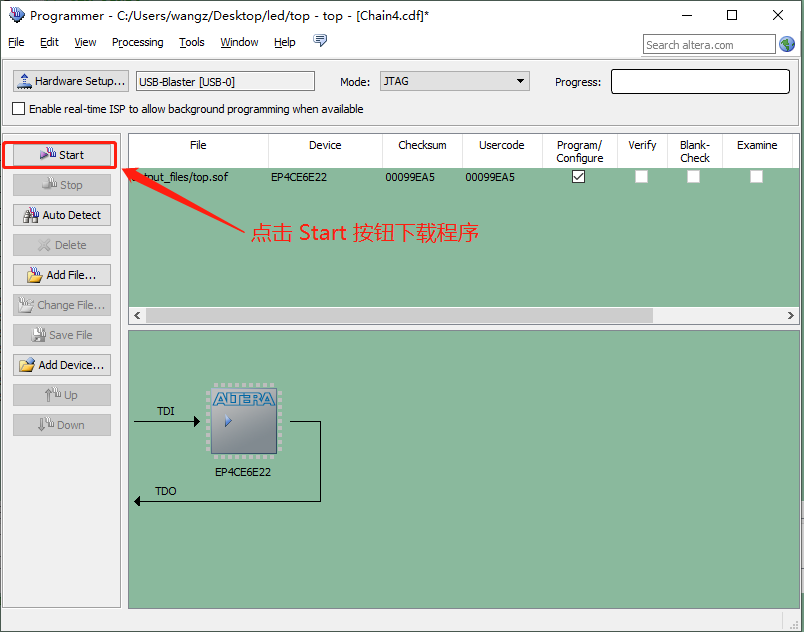

Quartus II 的第一个工程创建到此就结束了,最后烧写代码至开发板运行测试。下载后运行结果正常。

勤能补拙,遇到问题时,不要为了解决问题而解决问题,要找到问题产生的原因。

总结一句:不但要知其然,还要知其所以然。

FPGA —— LED控制的更多相关文章

- linux输入子系统(input subsystem)之按键输入和LED控制

实验现象:在控制台打印按键值,并且通过按键控制相应的LED亮灭. 1.代码 input_subsys_drv.c #include <linux/module.h> #include &l ...

- BeagleBone Black板第四课:简单LED控制实验

BBB板第四课:简单LED控制实验 学习BBB板的终于目的是想像单片机一样做控制,但控制思路全然不一样(Linux下控制硬件设备实质就是对相关设备虚拟文件的读写).研究了几天头都大了还是没有进展,网上 ...

- 电赛菜鸟营培训(一)——STM32F103CB之LED控制

一.STM32F103C8 引脚分布 二.LED的共阴.共阳接法 这里应该是七段数码管的接法. 限流电阻选择为470,在Multism中仿真,也需要接入,否则会出现闪烁情况.或者直接更改属性. 三.消 ...

- TI CC2541的LED控制

现在终于进入到蓝牙SPI的环节了, 下面还要研究I2C, 所以第一步, 先点灯, 就是GPIO控制吧. 参考一下LEd的初始化: void HalLedInit (void){#if (HAL_LED ...

- 树莓派linux驱动学习之LED控制

前面我们编写了hello world的程序,接下来继续研究GPIO功能,通过GPIO来控制LED的亮灭,这在单片机中应该算是十分简单的一个程序了,但是在Linux系统中控制GPIO没有那么简单,难点就 ...

- 基于Qt Gui的Led控制显示程序

基于arm + linux的嵌入式软件开发,基本上的内容主要是:u-boot的移植,kernel的裁剪和相关驱动程序的设计,root-fs的制作,应用程序的设计,其中,应用程序主要包含两方面的内容:G ...

- 在使用FPGA来控制DDR3/DDR2 IP 的时候两个错误的解决办法

对于熟悉Intel FPGA的老(gong)司(cheng)机(shi)来说,外部存储器的控制早已是轻车熟路,但是对于新手,DDR3/DDR2 的IP使用也许并没有那么简单,不过没关系,骏龙的培训网站 ...

- Android驱动入门-Led控制+app+ndk库+底层驱动

硬件平台: FriendlyARM Tiny4412 Cortex-A9 操作系统: UBUNTU 14.04 LTS 时间:2016-09-20 21:56:48 本次实验使用的是 安卓APP + ...

- zju(5)LED控制实验

1.实验目的 1.学习和掌握如何将一个驱动程序添加到Kconfig,编译到内核. 二.实验内容 1.编写EduKit-IV试验箱Linux操作系统下LED灯的驱动: 2.编写EduKit-IV试验箱L ...

随机推荐

- http学习--常用请求方法和响应状态码

常用的http请求方法: GET方法:请求服务器资源,并返回 POST方法:向指定资源提交数据进行处理请求(比如说表单,上传文件等).数据被包含在请求体中.POST请求可能会导致新的资源建立或已有资源 ...

- sublime text 编辑器的操作

我一直在用的代码编辑器是sublime text,然后总结了一些相关的操作方法. 一 环境操作 1.放大显示比例:Ctrl+ 2.缩小显示比例:Ctrl- 3.分屏:Alt+ Shift +数字 ...

- maven项目创建4 dao层整合

项目配置文件要放在打包成war包的web项目中 创建文件步骤 1 SqlMapConfig.xml <?xml version="1.0" encoding=" ...

- Acwing:137. 雪花雪花雪花(Hash表)

有N片雪花,每片雪花由六个角组成,每个角都有长度. 第i片雪花六个角的长度从某个角开始顺时针依次记为ai,1,ai,2,…,ai,6ai,1,ai,2,…,ai,6. 因为雪花的形状是封闭的环形,所以 ...

- 个推CTO深度解析数据智能之多维度分析系统的选型方法

引言 前文回顾:[<数据智能时代来临:本质及技术体系要求>][2]作为本系列的第一篇文章,概括性地阐述了对于数据智能的理解以及推出了对应的核心技术体系要求: 数据智能就是以数据作为生产资料 ...

- Java并发编程的艺术笔记(四)——ThreadLocal的使用

ThreadLocal,即线程变量,是一个以ThreadLocal对象为键.任意对象为值的存储结构.这个结构被附带在线程上,也就是说一个线程可以根据一个ThreadLocal对象查询到绑定在这个线程上 ...

- 前端开发——让算法"动"起来

正文 当然在我们不清楚具体操作细节前我们可以先假设一下,我们能够用什么来实现.按照以前看过的排序动画我将其分为 1.Js操作Dom,再搭配简单的css 2.Canvas动画 之后在查资料的时候发现还有 ...

- Django日志的配置

做开发离不开日志,以下是我在工作中写Django项目常用的logging配置. BASE_LOG_DIR = os.path.join(BASE_DIR, "log") LOG ...

- jpa repostiory

JpaRepository的查询 image.png image.png Spring Data JPA框架在进行方法名解析时,会先把方法名多余的前缀截取掉,比如 find.findBy.re ...

- 网络安全监控实战(一):Snort,Wazuh&VT

https://cloud.tencent.com/developer/news/222711