基于FPGA的数字钟设计---第三版

欢迎各位朋友关注“郝旭帅电子设计团队”,本篇为各位朋友介绍基于FPGA的数字钟设计---第三版。

功能说明:

1. 在数码管上面显示时分秒(共计六个数码管,前两个显示小时;中间两个显示分钟;最后两个显示秒)。

2. 利用按键可以切换24/12小时制(默认24小时制)。

3. led1的亮灭表示24小时制(亮)还是12小时制(灭)。

4. led2的亮灭表示上午(亮)还是下午(灭),24小时制时,一直灭。

5. 增加调整按键和加减按键。

6. 调整按键不按下时,正常显示时分秒。

按下第一次,进入调整状态,时间停止,并且小时开始闪烁,通过加减按键可以进行调整。

按下第二次,分钟开始闪烁,通过加减按键可以进行调整。

按下第三次,秒开始闪烁,通过加减按键可以进行调整。

按下第四次,进入正常运行状态。

后续再按下时,重复以上的过程

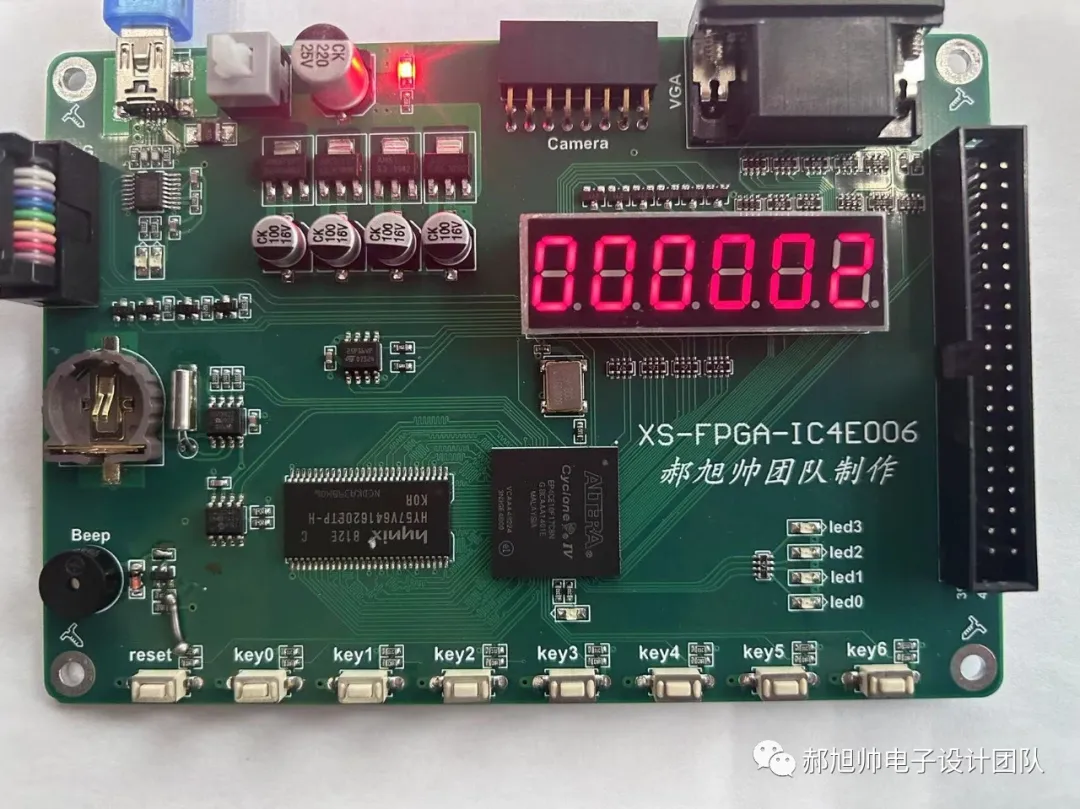

使用平台:本次设计应用Altera的平台设计(芯片:EP4CE10F17C8N)。

仿真平台:Modelsim。

作者QQ:746833924

说明:本篇设计中不涉及到IP和原语,代码在其他平台依然可以适用;当其他板卡电路不同时,会导致不同的现象出现,如有需要修改代码请联系作者;如需作者使用的板卡,请联系作者;

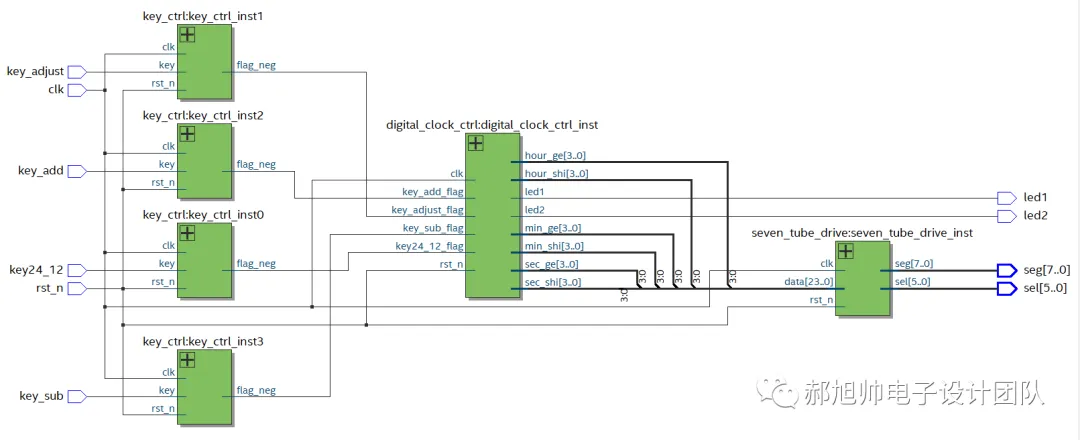

设计思想如下:

key_ctrl模块负责将外部的按键信号进行消抖,并且产生对应边沿变化时的脉冲;digital_clock_ctrl模块负责根据脉冲信号和设计逻辑产生对应数字逻辑和led的状态;seven_tube_drive(七段数码管驱动)模块负责将digital_clock_ctrl模块产生的数字逻辑显示到数码管上。

key_ctrl模块设计思想为:按键信号是由外部机械式按键产生,每次按下或者抬起时,会产生一定的抖动。如果直接对其进行边沿检测就会导致多次触发。故而需要设计按键消抖,进而对消抖之后的波形进行边沿检测。消抖原理为:外部按键信号发生改变后,如果能够持续20ms,没有新的改变,就认为此次改变不是抖动,而是真正的按下,然后进行采样即可。

// 记录任意边沿之后没有遇到新的边沿的时间长度是否达到20Ms

//---------------------------------------------------------------------------------------

always@(posedgeclk)begin

if(rst_n ==1'b0)

cnt_20ms <=20'd0;

else

if(pulse_key_negedge ==1'b1||pulse_key_posedge ==1'b1)

cnt_20ms <=20'd1;

else

if(cnt_20ms >20'd0&&cnt_20ms <T_20ms)

cnt_20ms <=cnt_20ms +1'b1;

else

cnt_20ms <=20'd0;

end

// ---------------------------------------------------------------------------------------

// 任意边沿之后没有遇到新的边沿的时间长度达到20Ms,认为按键稳定,此时采样

//--------------------------------------------------------------------------------------

always@(posedgeclk)begin

if(rst_n ==1'b0)

key_wave <=1'b1;

else

if(cnt_20ms ==T_20ms)

key_wave <=key_rr;

else

key_wave <=key_wave;

end

//--------------------------------------------------------------------------------------

// 对消抖之后的按键信号进行边沿检测

//---------------------------------------------------------------------------------------------

initialkey_wave_r =1'b1;

always@(posedgeclk)key_wave_r <=key_wave;

assignflag_neg =(key_wave_r ==1'b1&&key_wave ==1'b0)?1'b1:1'b0;

assignflag_pos =(key_wave_r ==1'b0&&key_wave ==1'b1)?1'b1:1'b0;

//--------------------------------------------------------------------------------------------

digital_clock_ctrl模块的设计思想:首先根据外部的调整脉冲,确定工作状态。

reg[1:0] state_adjust;// 0 : 正常模式 1:小时调整 2 :分钟调整 3 :秒调整

// 切换调整模式和正常模式

always@(posedgeclk)begin

if(rst_n ==1'b0)

state_adjust <=2'b00;

else

if(key_adjust_flag ==1'b1)

state_adjust <=state_adjust +1'b1; // 0-3无限循环

else

state_adjust <=state_adjust;

end

根据基本逻辑、工作状态和外部加减脉冲产生24小时进制的时分秒。

// 1秒钟计时 // 只有正常模式才开始计时

always@(posedgeclk)begin

if(rst_n ==1'b0)

cnt <=26'd0;

else

if(cnt <T_1s -1'b1 &&state_adjust ==2'd0)

cnt <=cnt +1'b1;

else

cnt <=26'd0;

end

// 秒计时

// 在秒调整模式中,加和减按键做对应的工作。

// 在正常模式,正常计时

always@(posedgeclk)begin

if(rst_n ==1'b0)

sec <=6'd50;

else

if(state_adjust ==2'd3)

if(key_add_flag ==1'b1)

if(sec <6'd59)

sec <=sec +1'b1;

else

sec <=6'd0;

else

if(key_sub_flag ==1'b1)

if(sec >6'd0)

sec <=sec -1'b1;

else

sec <=6'd59;

else

sec <=sec;

else

if(cnt ==T_1s -1'b1)

if(sec <6'd59)

sec <=sec +1'b1;

else

sec <=6'd0;

else

sec <=sec;

end

24小时进制和12小时进制在外部按键按下时切换;分和秒的显示没有改变,小时的显示需要调整。24小时制时,正常显示;12小时制时,时大于11时,需要减去12;并且利用led2进行表是为上午还是下午。

//根据显示模式,调整小时的显示

always@*begin

if(state ==1'b0)

hour_adjust =hour;

else

if(hour >6'd11)

hour_adjust =hour -6'd12;

else

hour_adjust =hour;

end

//根据显示模式和小时值,计算是上午还是下午

always@*begin

if(state ==1'b0)

led2 =1'b0;

else

if(hour >6'd11)

led2 =1'b0;

else

led2 =1'b1;

end

如果在调整模式中,启动一个一秒钟的计时器。

// 处于调整模式时,开始计时一秒钟

always@(posedgeclk)begin

if(rst_n ==1'b0)

flash_cnt <=26'd0;

else

if(state_adjust ==2'd0)

flash_cnt <=26'd0;

else

if(flash_cnt <T_1s -1'b1)

flash_cnt <=flash_cnt +1'b1;

else

flash_cnt <=26'd0;

end

分钟和小时类似,在这里不在赘述。

在正常模式下将需要显示的时、分、秒的十位和个位计算出来。在对应的调整模式下,需要前半秒输出对应的数字,后半秒输出全F。在数码管驱动中,当输入正常数字0~9显示数字,当输入F时数码管熄灭,此时数码管就闪烁起来了。

//计算得出小时、分钟、秒的个位和十位 always@(posedgeclk)hour_shi <=(state_adjust ==2'd1&&flash_cnt >T_1s/2)?4'hf:hour_adjust/10; always@(posedgeclk)hour_ge <=(state_adjust ==2'd1&&flash_cnt >T_1s/2)?4'hf:hour_adjust%10; always@(posedgeclk)min_shi <=(state_adjust ==2'd2&&flash_cnt >T_1s/2)?4'hf:min/10; always@(posedgeclk)min_ge <=(state_adjust ==2'd2&&flash_cnt >T_1s/2)?4'hf:min%10; always@(posedgeclk)sec_shi <=(state_adjust ==2'd3&&flash_cnt >T_1s/2)?4'hf:sec/10; always@(posedgeclk)sec_ge <=(state_adjust ==2'd3&&flash_cnt >T_1s/2)?4'hf:sec%10;

所有的逻辑在复位时,可以给予各种值,下板时,通过按下复位,可以让数字钟从自己想要的时间开始运行。

以上即为digital_clock_ctrl模块的设计思想;

七段数码管为普通六位一体的共阳极数码,采用动态驱动的方式,在此不再赘述。

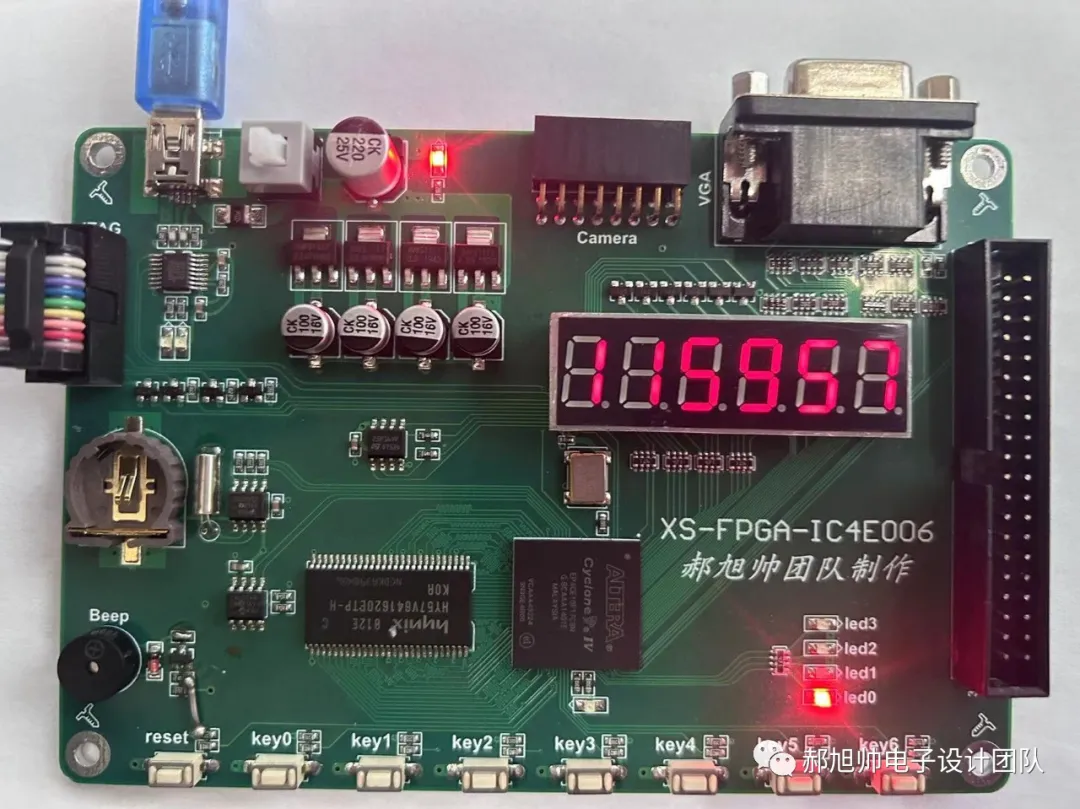

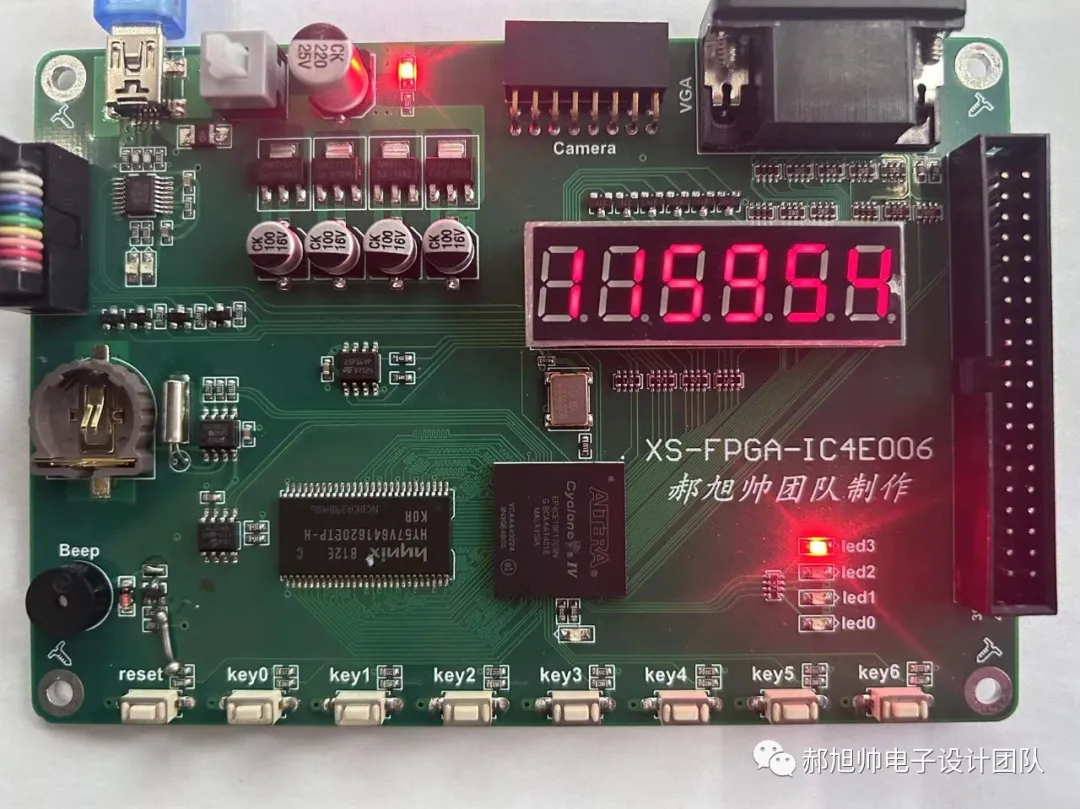

下板后(下板成功,按下复位并释放,复位的时间设置为上午11时59分50秒),我们就可以看到数字钟的运行情况。

当然我们也可以使用按键进行调节到我们想要的任何时间点。

下板后,led1点亮(24小时制),经过10秒后,可以看到12时0分0秒。

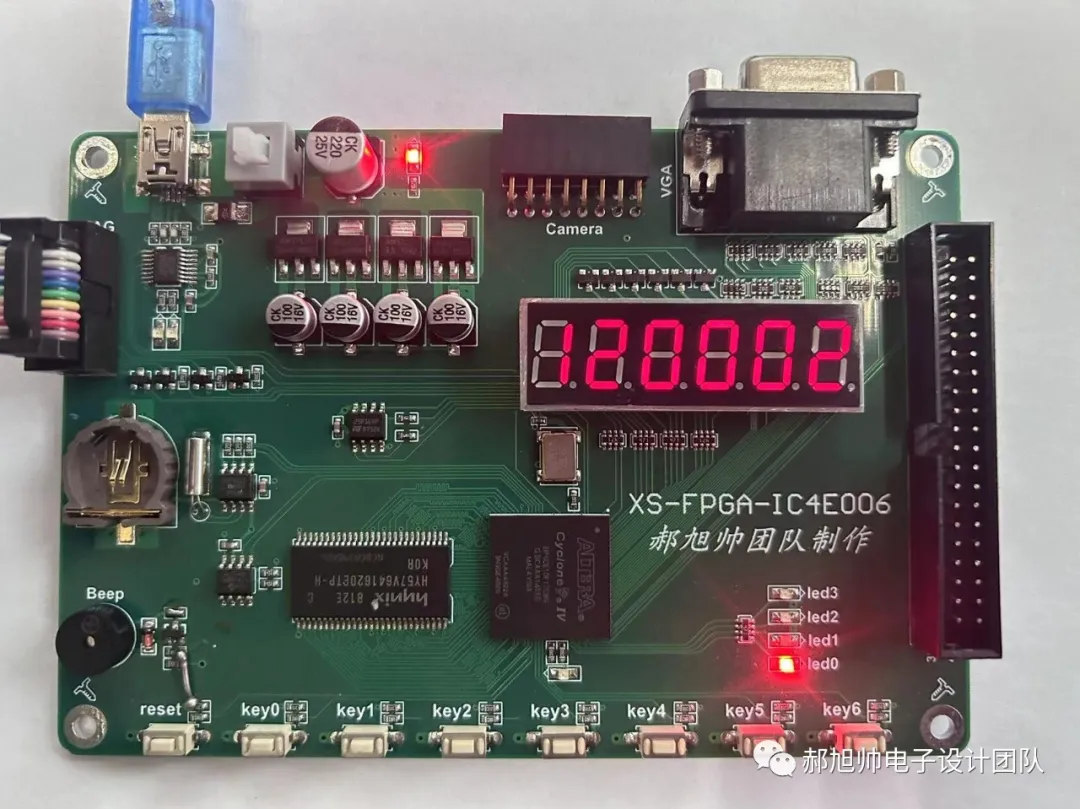

按下复位后,立刻按下切换显示模式。此时led1熄灭(12小时制),led2点亮(上午)。经过10秒后,可以看到0时0分0秒,led2熄灭(下午)。

下板后,演示视频(链接)如下:

https://www.bilibili.com/video/BV1FT4y1x7RQ/?vd_source=b5405faeab8632f02533bcbfc5e52e55

本设计所有内容(设计代码、设计工程)链接为:

链接:https://pan.baidu.com/s/1Bo6GK1bm1vDXfahwZusKVg

提取码:i9xj

本篇内容中有部分资源来源于网络,如有侵权,请联系作者。

如果您觉得本公众号还不错的话,可以推给身边的朋友们,感谢并祝好!

基于FPGA的数字钟设计---第三版的更多相关文章

- 基于FPGA的HDMI显示设计(三)

上一篇:基于FPGA的VGA显示设计(二) 10月10日 ~ 20日期间实习,令我万万没想到的是实习题目是 “便携式高清电视显示屏测试系统原型设计” 也就是 “基于FPGA的视频显示”. 实习要求用 ...

- 基于FPGA的数字识别的实现

欢迎大家关注我的微信公众号:FPGA开源工作室 基于FPGA的数字识别的实现二 作者:lee神 1 背景知识 1.1基于FPGA的数字识别的方法 通常,针对印刷体数字识别使用的算法有:基于模版 ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

- 基于python的接口测试框架设计(三)接口测试的框架

基于python的接口测试框架设计(三)接口测试的框架 其实我这里用到的是unittest单元测试框架,,这个框架好就好在比较清楚,,setup terdown都可以处理一些初始化及完成后的工作 主要 ...

- FPGA经典:Verilog传奇与基于FPGA的数字图像处理原理及应用

一 简述 最近恶补基础知识,借了<<Verilog传奇>>,<基于FPGA的嵌入式图像处理系统设计>和<<基千FPGA的数字图像处理原理及应用>& ...

- 基于串口校时的数字钟设计(verilog实现)

任务: 电路图设计: 设计: 模块1:1.先设计一个计数时钟,为了仿真方便,这里把1000ns当作1s. 创建一个计数器second_lim,当计数到1000/20时清零,即1s. 秒显示器secon ...

- 基于FPGA的数字秒表(数码管显示模块和按键消抖)实现

本文主要是学习按键消抖和数码管动态显示,秒表显示什么的,个人认为,拿FPGA做秒表真是嫌钱多. 感谢 感谢学校和至芯科技,笔者专业最近去北京至芯科技培训交流了一周.老师的经验还是可以的,优化了自己的代 ...

- 基于FPGA的VGA显示设计(一)

前言 FPGA主要运用于芯片验证.通信.图像处理.显示VGA接口的显示器是最基本的要求了. 原理 首先需要了解 : (1)VGA接口协议:VGA端子_维基百科 .VGA视频传输标准_百度 引脚1 RE ...

- 基于FPGA的异步FIFO设计

今天要介绍的异步FIFO,可以有不同的读写时钟,即不同的时钟域.由于异步FIFO没有外部地址端口,因此内部采用读写指针并顺序读写,即先写进FIFO的数据先读取(简称先进先出).这里的读写指针是异步的, ...

- c语言程序与设计第三版-苏小红--第一轮学习笔记、难点整理

---恢复内容开始--- 1> 编程:需求分析.设计.编写程序(编码.编辑.链接.运行).调试程序 2> 指数形式:e的左边是数值部分(有效数字),不能省略,但可以表示成 .e-4:等等: ...

随机推荐

- OpenHarmony持久化存储UI状态:PersistentStorage

前两个小节介绍的LocalStorage和AppStorage都是运行时的内存,但是在应用退出再次启动后,依然能保存选定的结果,是应用开发中十分常见的现象,这就需要用到PersistentStor ...

- OpenHarmony 3.2 Beta Audio——音频渲染

一.简介 Audio是多媒体子系统中的一个重要模块,其涉及的内容比较多,有音频的渲染.音频的采集.音频的策略管理等.本文主要针对音频渲染功能进行详细地分析,并通过源码中提供的例子,对音频渲染进行流程的 ...

- Seaborn结构化图形绘制(FacetGrid)

结构化图形绘制(FacetGrid) 可实现多行多列个性化绘制图形. sns.FacetGrid( data, row=None, col=None, hue=None, col_wrap=None, ...

- redis 简单整理——java 客户端jedis[十六]

前言 简单介绍一下java客户端jedis. 正文 Java有很多优秀的Redis客户端(详见:http://redis.io/clients#java),这 里介绍使用较为广泛的客户端Jedis,本 ...

- js 词法作用域

前言 什么是作用域? 作用域(scope),程序设计概念,通常来说,一段程序代码中所用到的名字并不总是有效/可用的,而限定这个名字的可用性的代码范围就是这个名字的作用域. 白话文:作用域就是变量在哪块 ...

- xilinx下载器,JTAG-HS3和Platform Cable USB II 速度对比

下面测试速度,以一个V7的配置文件为例子.文件大小如下,27MB.特别是对于有点规模的项目配置文件都是很大的.总不能是点灯项目. 选择普通的下载器,Platform Cable USB.这种下载器是基 ...

- 百度AIPNLP 文本相似度 文本审核

效果不如有监督的bert文本相似度好 from aip import AipNlp APP_ID = "22216281" APT_KEY = "foEeYauuvnqW ...

- 《Effective C#》系列之(六)——提高多线程的性能

一.综述 <Effective C#>中提高多线程性能的方法主要有以下几点: 避免锁竞争:锁的使用会导致线程阻塞,从而影响程序的性能.为了避免锁竞争,可以采用无锁编程技术,如CAS(Com ...

- 剑指offer39(Java)-数组中出现次数超过一半的数字(简单)

题目: 数组中有一个数字出现的次数超过数组长度的一半,请找出这个数字. 你可以假设数组是非空的,并且给定的数组总是存在多数元素. 示例 1: 输入: [1, 2, 3, 2, 2, 2, 5, 4, ...

- 2021云栖大会开源引力峰会重磅发布的战略合作,Grafana服务到底是什么?

简介: 这几天关注云栖大会的小伙伴一定会发现阿里巴巴合伙人.阿里云高级研究员蒋江伟(小邪)在云栖大会开源引力峰会的演讲中,特别提到了一个叫 Grafana 服务的产品,并特意花费一页 PPT 介绍了这 ...