USB中TOKEN的CRC5与CRC16校验(神奇的工具生成Verilog实现)

USB2.0IP设计

最近,在学习USB2.0IP的设计,其中包含了CRC校验码的内容,之前学习千兆以太网曾经用到过CRC32校验(https://www.cnblogs.com/Xwangzi66/p/14185143.html),CRC详细原理可见括号的链接,今天则从怎么用工具快速生成Verilog代码的角度介绍。

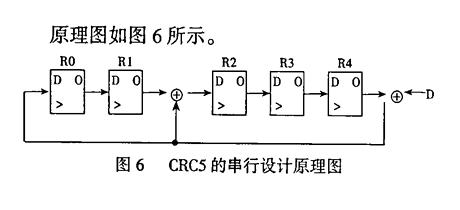

一 确定CRC5的多项式

G(X)= X^5 + X^2 + 1,输入数据的位宽为11bit,即CRC5中的输入信号[10:0]data_i.

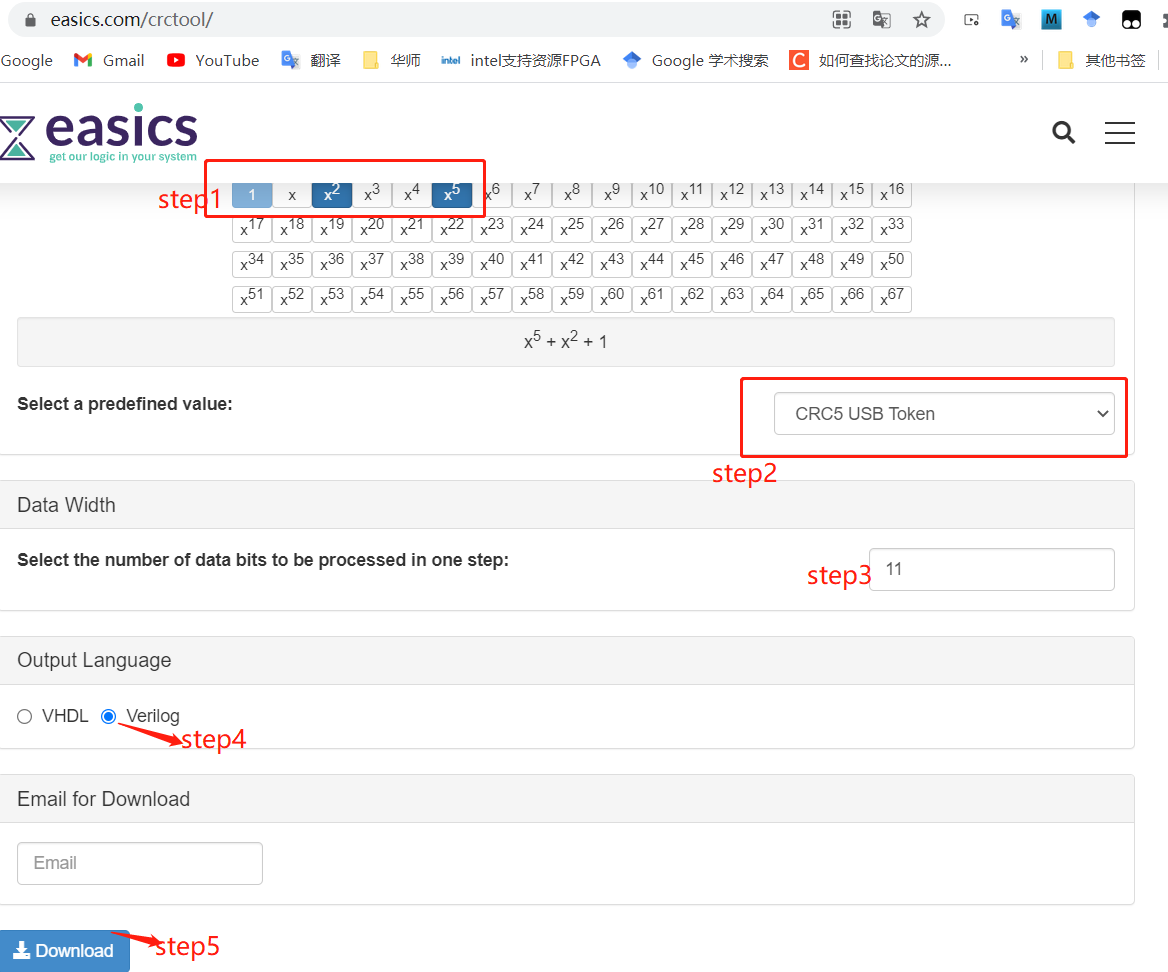

二 在线网页生成CRC5的Verilog代码

链接如下:https://www.easics.com/crctool/

在线生成CRC5校验代码如下图:第一步是确定多项式,此处是CRC5的多项式。第二步选择CRC的类别,如CRC16,CRC32等。第三步,选择待校验数据的位宽。第四步,选择输出的编程语言,用Verilog实现。第五步,下载打开就。注意填好邮箱,此处为了保护本人隐私则空着。

2.在线工具生成CRC5的Verilog代码

1 module CRC5_D11;

2

3 // polynomial: x^5 + x^2 + 1

4 // data width: 11

5 // convention: the first serial bit is D[10]

6 function [4:0] nextCRC5_D11;

7

8 input [10:0] Data;

9 input [4:0] crc;

10 reg [10:0] d;

11 reg [4:0] c;

12 reg [4:0] newcrc;

13 begin

14 d = Data;

15 c = crc;

16

17 newcrc[0] = d[10] ^ d[9] ^ d[6] ^ d[5] ^ d[3] ^ d[0] ^ c[0] ^ c[3] ^ c[4];

18 newcrc[1] = d[10] ^ d[7] ^ d[6] ^ d[4] ^ d[1] ^ c[0] ^ c[1] ^ c[4];

19 newcrc[2] = d[10] ^ d[9] ^ d[8] ^ d[7] ^ d[6] ^ d[3] ^ d[2] ^ d[0] ^ c[0] ^ c[1] ^ c[2] ^ c[3] ^ c[4];

20 newcrc[3] = d[10] ^ d[9] ^ d[8] ^ d[7] ^ d[4] ^ d[3] ^ d[1] ^ c[1] ^ c[2] ^ c[3] ^ c[4];

21 newcrc[4] = d[10] ^ d[9] ^ d[8] ^ d[5] ^ d[4] ^ d[2] ^ c[2] ^ c[3] ^ c[4];

22 nextCRC5_D11 = newcrc;

23 end

24 endfunction

25 endmodule

三 修改成自己USB的IP设计的CRC5校验模块

通过在线工具生成后,自己可以修改模块名,输入输出信号名,寄存器名,以更好地用在自己的FPGA项目中,本人CRC5修改如下:

1 module usbh_crc5

2 (

3 input [4:0] crc_i,

4 input [10:0] data_i,

5 output [4:0] crc_o

6 );

7

8 //-----------------------------------------------------------------

9 // Implementation

10 //-----------------------------------------------------------------

11 assign crc_o[0] = data_i[10] ^ data_i[9] ^ data_i[6] ^ data_i[5] ^ data_i[3] ^ data_i[0] ^

12 crc_i[0] ^ crc_i[3] ^ crc_i[4];

13

14 assign crc_o[1] = data_i[10] ^ data_i[7] ^ data_i[6] ^ data_i[4] ^ data_i[1] ^

15 crc_i[0] ^ crc_i[1] ^ crc_i[4];

16

17 assign crc_o[2] = data_i[10] ^ data_i[9] ^ data_i[8] ^ data_i[7] ^ data_i[6] ^ data_i[3] ^ data_i[2] ^ data_i[0] ^

18 crc_i[0] ^ crc_i[1] ^ crc_i[2] ^ crc_i[3] ^ crc_i[4];

19

20 assign crc_o[3] = data_i[10] ^ data_i[9] ^ data_i[8] ^ data_i[7] ^ data_i[4] ^ data_i[3] ^ data_i[1] ^

21 crc_i[1] ^ crc_i[2] ^ crc_i[3] ^ crc_i[4];

22

23 assign crc_o[4] = data_i[10] ^ data_i[9] ^ data_i[8] ^ data_i[5] ^ data_i[4] ^ data_i[2] ^

24 crc_i[2] ^ crc_i[3] ^ crc_i[4];

25

26 endmodule

通过修改后,代码更简洁高效,更方便调用,直接在USB中调用即可!

后续的CRC16的Verilog实现,同CRC5生成方法一样,先用在线工具生成,再修改一些模块名,输入输出信号即可。

CRC16代码如下:

1 module usbh_crc16

2 (

3 input [15:0] crc_i,

4 input [7:0] data_i,

5 output [15:0] crc_o

6 );

7

8 //-----------------------------------------------------------------

9 // Implementation

10 //-----------------------------------------------------------------

11 assign crc_o[15] = data_i[0] ^ data_i[1] ^ data_i[2] ^ data_i[3] ^ data_i[4] ^

12 data_i[5] ^ data_i[6] ^ data_i[7] ^ crc_i[7] ^ crc_i[6] ^

13 crc_i[5] ^ crc_i[4] ^ crc_i[3] ^ crc_i[2] ^

14 crc_i[1] ^ crc_i[0];

15 assign crc_o[14] = data_i[0] ^ data_i[1] ^ data_i[2] ^ data_i[3] ^ data_i[4] ^ data_i[5] ^

16 data_i[6] ^ crc_i[6] ^ crc_i[5] ^ crc_i[4] ^

17 crc_i[3] ^ crc_i[2] ^ crc_i[1] ^ crc_i[0];

18 assign crc_o[13] = data_i[6] ^ data_i[7] ^ crc_i[7] ^ crc_i[6];

19 assign crc_o[12] = data_i[5] ^ data_i[6] ^ crc_i[6] ^ crc_i[5];

20 assign crc_o[11] = data_i[4] ^ data_i[5] ^ crc_i[5] ^ crc_i[4];

21 assign crc_o[10] = data_i[3] ^ data_i[4] ^ crc_i[4] ^ crc_i[3];

22 assign crc_o[9] = data_i[2] ^ data_i[3] ^ crc_i[3] ^ crc_i[2];

23 assign crc_o[8] = data_i[1] ^ data_i[2] ^ crc_i[2] ^ crc_i[1];

24 assign crc_o[7] = data_i[0] ^ data_i[1] ^ crc_i[15] ^ crc_i[1] ^ crc_i[0];

25 assign crc_o[6] = data_i[0] ^ crc_i[14] ^ crc_i[0];

26 assign crc_o[5] = crc_i[13];

27 assign crc_o[4] = crc_i[12];

28 assign crc_o[3] = crc_i[11];

29 assign crc_o[2] = crc_i[10];

30 assign crc_o[1] = crc_i[9];

31 assign crc_o[0] = data_i[0] ^ data_i[1] ^ data_i[2] ^ data_i[3] ^ data_i[4] ^ data_i[5] ^

32 data_i[6] ^ data_i[7] ^ crc_i[8] ^ crc_i[7] ^ crc_i[6] ^

33 crc_i[5] ^ crc_i[4] ^ crc_i[3] ^ crc_i[2] ^

34 crc_i[1] ^ crc_i[0];

35

36 endmodule

Crc16 Code

总结,一直都是根据多项式,确定硬件电路的形式,然后查表,如V3学院千兆以太网的CRC32校验教程,很繁琐,得理解原理,今天意外知道一种新的方法,通过在线工具生成Verilog实现:

USB中TOKEN的CRC5与CRC16校验(神奇的工具生成Verilog实现)的更多相关文章

- 最详细易懂的CRC-16校验原理(附源程序)(转)

最详细易懂的CRC-16校验原理(附源程序) from:http://www.openhw.org/chudonganjin/blog/12-08/230184_515e6.html 最详细易懂的CR ...

- 最详细易懂的CRC-16校验原理(附源程序)

from:http://www.openhw.org/chudonganjin/blog/12-08/230184_515e6.html 最详细易懂的CRC-16校验原理(附源程序) 1.循环校验码( ...

- C# 实现CRC16校验

前言 本文将使用一个NuGet公开的组件技术来实现CRC16校验功能,提供了一些简单的API,来方便的实现. 在Visual Studio 中的NuGet管理器中可以下载安装,也可以直接在NuGet控 ...

- CRC-16校验原理

最详细易懂的CRC-16校验原理(附源程序) 1.循环校验码(CRC码): 是数据通信领域中最常用的一种差错校验码,其特征是信息字段和校验字段的长度可以任意选定. 2.生成CRC码的基本原理: 任意一 ...

- Delphi CRC16校验算法实现(转)

循环冗余码校验英文名称为Cyclical Redundancy Check,简称CRC.它是利用除法及余数的原理来作错误侦测(Error Detecting)的.实际应用时,发送装置计算出CRC值并随 ...

- 基于Modbus三种CRC16校验方法的性能对比

目录 1.背景介绍 2. CRC校验的三种方法 2.1. 直接计算CRC校验 2.2. 查短表法计算CRC16校验 2.3.查大表法计算CRC16校验 3.三种校验方式的测试方法 3.1.直接计算CR ...

- 讨论两种Redis中Token的存储方式

摘要:本文讨论一个问题:存储token时,token与对应用户id谁来作为key? 问题起源问题起源于要给公司的后台管理系统添加权限管理,选用的是开源框架shiro,而原本系统上是采用token做了登 ...

- usb中的传输模式

别人总结的一个usb传输模式,保存一下 usb中的endpoint(端点)和传输模式 端点: 端点位于USB 外设内部,所有通信数据的来源或目的都基于这些端点,是一个可寻址的FIFO. 每个USB 外 ...

- struts2中token防止重复提交表单

struts2中token防止重复提交表单 >>>>>>>>>>>>>>>>>>>&g ...

随机推荐

- 抛弃vuex ,拥抱ts,手撸泛型Store<T>!

前段时间学习了下vue3 和ts ,就尝试下做了个项目,结果发现vuex和ts几乎无法结合,越写越别扭,开始怀疑用ts就是自己给自己挖坑,然后加了几个vue相关的群,去抱怨了几句,得到大佬指点:你可以 ...

- 0-0 Linux安装在VMvare虚拟机上

一.安装VMware虚拟机: 双击, 上面一步会提示你输入密钥,你只要双击这个,复制里面的一串码粘贴进去就可以. 点击完成,至此VM虚拟机安装完成. 二.在VMvare虚拟机上安装centos. 1. ...

- 判断post,ajax,get请求的方法

判断post,ajax,get请求的方法 define('IS_GET',isset($_SERVER['REQUEST_METHOD']) ? $_SERVER['REQUEST_METHOD'] ...

- 从苏宁电器到卡巴斯基第26篇:难忘的三年硕士时光 IV

录课,录课,还是录课 开题结束以后,已经是三月的下旬,当时我在考虑要不要回家,毕竟学校这里也没什么事了,我待在学校还得付出一定的花销.后来我考虑到在家的话,只有晚上才能够录课,而在学校的话,整个白天都 ...

- Windows核心编程 第七章 线程的调度、优先级和亲缘性(上)

第7章 线程的调度.优先级和亲缘性 抢占式操作系统必须使用某种算法来确定哪些线程应该在何时调度和运行多长时间.本章将要介绍Microsoft Windows 98和Windows 2000使用的一些算 ...

- 汇编环境搭建(vs2010(2012)+masm32)

我本地使用的环境VS2012(2010)+MASM32,下面的图是在网上找的几个博客拼在一起的,用的是vs2010,但是并不影响.(所有文件我都打包好了,如果懒的话可以直接下载这个包)地址是:http ...

- (2) arm 指令条件码

条件码助记符 标志 含义 EQ Z=1 相等 NE Z=0 不相等 CS/HS C=1 无符号数大于或等于 CC/LO C=0 无符号数小于 MI N=1 负数 PL N=0 正数或0 VS V=1 ...

- SQL注入注释符(#、-- 、/**/)使用条件及其他注释方式的探索

以MySQL为例,首先我们知道mysql注释符有#.-- (后面有空格)./**/三种,在SQL注入中经常用到,但是不一定都适用.笔者在sqlilabs通关过程中就遇到不同场景用的注释符不同,这让我很 ...

- OpenStack+kvm虚拟机xml格式解析

配置说明 首先介绍一下配置结构: xml配置遵循<keyword> xxxxxx </keyword>的格式,即一个配置段以<keyword>开头,以</ke ...

- 【python】Leetcode每日一题-位1的个数

[python]Leetcode每日一题-位1的个数 [题目描述] 编写一个函数,输入是一个无符号整数(以二进制串的形式),返回其二进制表达式中数字位数为 '1' 的个数(也被称为汉明重量). 示例1 ...