FPGA控制RGMII接口PHY芯片基础

一、前言

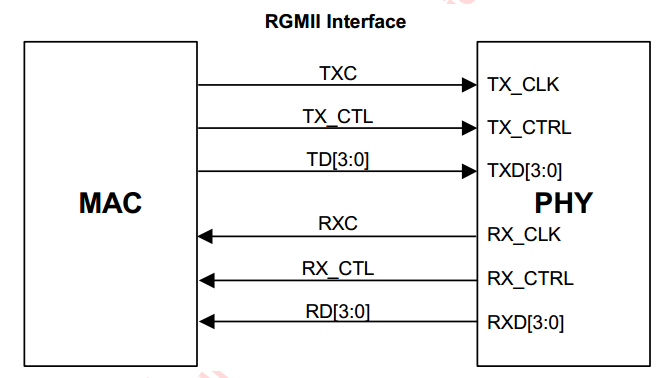

网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG。但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统。这类接口总线位宽小,可以降低电路成本,在实际项目中应用更广泛。

二、从GMII过度到RGMII

先看看GMII和RGMII主要的接口。

GMII:

发送 gmii_tx_clk gmii_tx_d[7:0] gmii_tx_en gmii_tx_er

接收 gmii_rx_clk gmii_rx_d[7:0] gmii_rx_dv gmii_rx_er

RGMII:

发送 tx_clk tx_d[3:0] tx_ctrl

接收 rx_clk rx_d[3:0] rx_ctrl

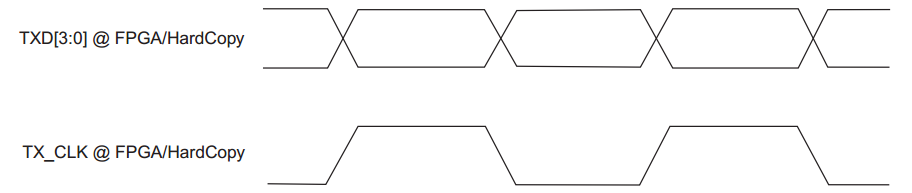

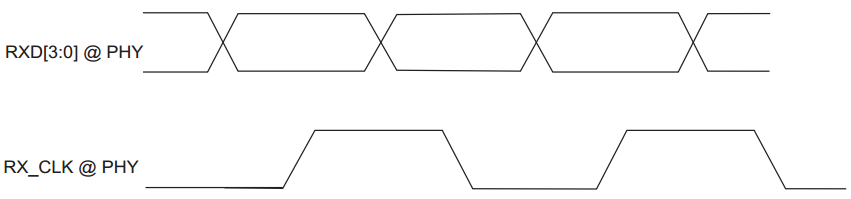

为什么接口变少了?首先数据总线从时钟单边沿采样8bit转变为了双边沿采样4bit,从88E1512 Datasheet中时序图可以直观看出这一点。

RGMII中上升沿发送一字节数据的低四位,下降沿发送剩余的高四位数据。接收端时钟双边沿采样,因此125MHZ*8bit = 125MHZ*4bit*2 = 1000Mbit/s。至于GMII中的数据有效和数据错误指示信号被ctrl信号复用:tx_ctrl在时钟tx_clk上升沿发送是tx_en,在下降沿发送是tx_en ^ tx_er。rx_ctrl在时钟rx_clk上升沿接收是rx_dv,在下降沿接收是rx_en ^ rx_er。综上,RGMII接口引脚数从25个降低到14个。

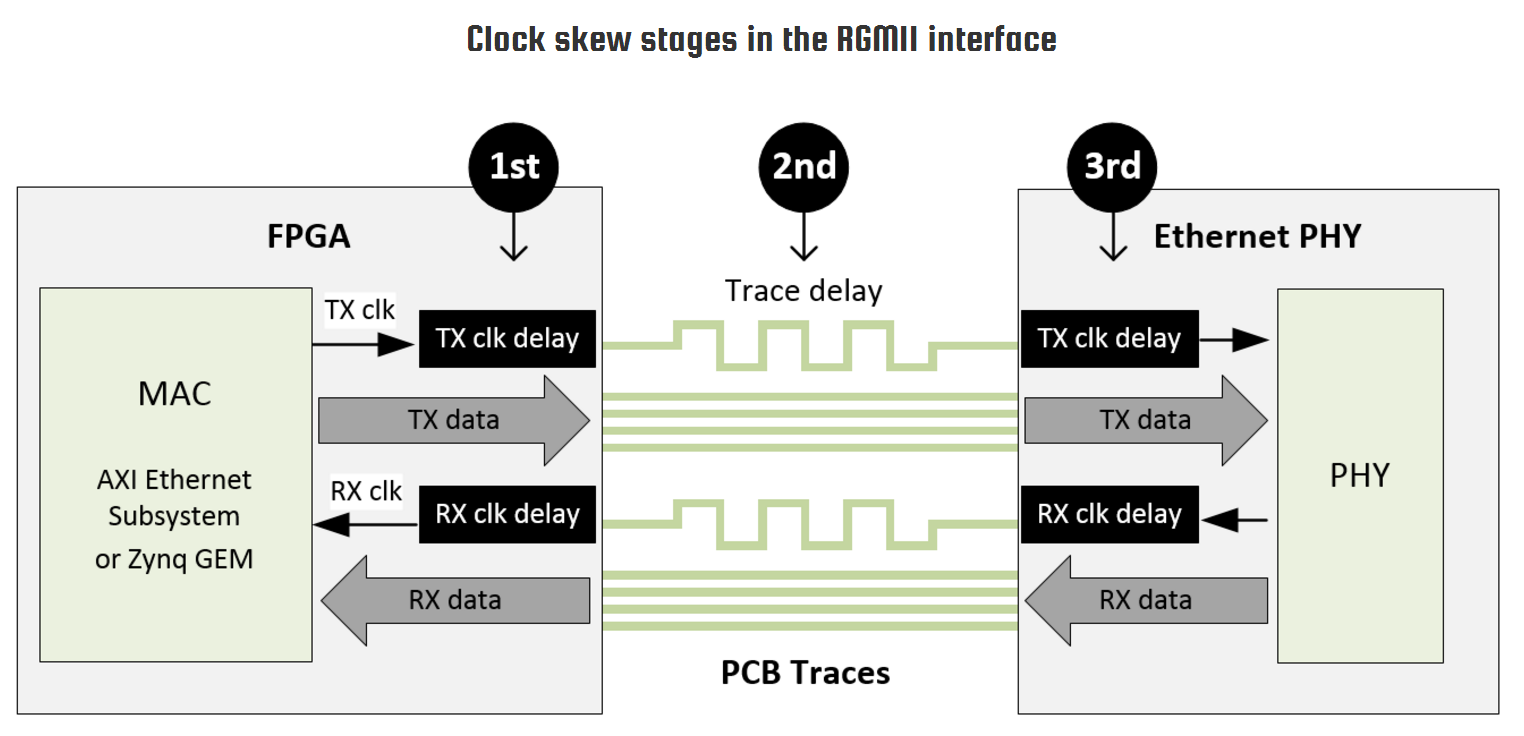

三、add clock skew

从上边的时序图分析,数据在时钟的边沿变化。因此如果不做额外处理,接收端无法稳定采样。为了解决这一问题,常见的做法是为时钟信号添加延时,使其边沿对准数据总线的稳定区间。可以在控制器端、PCB走线以及PHY芯片内部添加时钟偏移,本文使用最后一种方式实现。

在第三阶段中添加延迟。数据发送方向,FPGA侧的TX_CLK信号不需要额外处理,也就是说FPGA发送与数据边沿对齐的时钟信号。TXD和TX_CLK信号波形如图。

PHY内部会调整TX_CLK,使之能够稳定采样TXD。数据接收方向,由于RX_CLK由PHY提供,PHY芯片直接产生与数据中心对齐的时钟信号。RXD和RX_CLK信号波形如图。

可见,使PHY芯片工作在延迟模式下时,FPGA单不需要添加额外的逻辑来保证稳定采样。发送方向直接将数据驱动时钟作为TX_CLK信号发送,接收方向直接利用RX_CLK对RXD信号采样。

四、系统设计方案

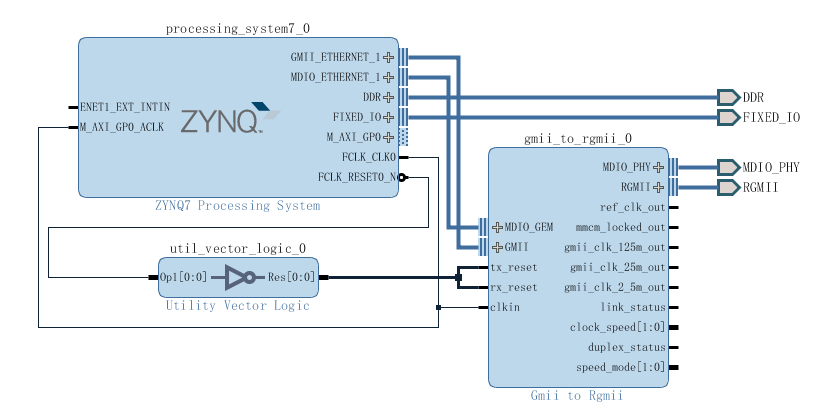

本文使用ZYNQ内部的MAC控制器实现数据链路层功能。但由于其接口为GMII,需要用到GMII_to_RGMII IP Core转换接口逻辑。上层网络协议则通过LWIP开源协议栈完成。首先配置ZYNQ IP,使能ENET1并以EMIO方式引出。

系统硬件结构如图:

五、I/O 时序约束

在较高速设计场合下,输入输出接口部分很容易出现数据采样不稳定的现象。这时候就要通过Input delay,output delay约束以及STA来分析设计是否满足稳定采样需求。input/output delay是指数据相对于时钟的延迟,只有设置好上述两个数值,综合工具才会往正确的方向优化并给出合理的时序报告。

FPGA与RGMII接口的PHY芯片之间的时序关系按照数据接口同步和数据采样方式属于源同步DDR采样。input delay约束对应接收方向,时序关系是中心对齐。output delay约束对应发送方向,时序关系是边沿对齐。前者由于很多时候不知道上游器件Tcko信息,会使用示波器测量有效数据窗口来计算。而后者因为是边沿对齐,通过示波器测量抖动窗口并使用skew based method计算。这部分笔者还没有亲身实践过,若有误欢迎指出。

参考文献

1 千兆以太网芯片88E1111 RGMII模式的驱动 - 我心狂野 - 博客园 http://www.cnblogs.com/shengansong/archive/2012/01/04/2311894.html

2 RGMII布线指导 RGMII Layout Guide | 无线时代 http://www.witimes.com/rgmii-layout-guide/

3 RGMII_PHY测试笔记1 基于开发板MiS603-X25-whilebreak-电子技术应用-AET-北大中文核心期刊-最丰富的电子设计资源平台 http://blog.chinaaet.com/whilebreak/p/46639

4 千兆以太网芯片88E1111 RGMII模式的驱动 - 百度文库 https://wenku.baidu.com/view/d2cc412fff00bed5b9f31d49.html

5 RGMII Interface Timing Considerations | Ethernet FMC http://ethernetfmc.com/rgmii-interface-timing-considerations/

6 ALTERA AN 477: Designing RGMII Interfaces with FPGAs and HardCopy ASICs

7 米联客 ESFP1512 以太网 SFP 光电卡教程

8 Vivado使用误区与进阶——XDC约束技巧之I/O篇 (上) - neufeifatonju的博客 - CSDN博客 https://blog.csdn.net/neufeifatonju/article/details/80653172

9 Vivado使用误区与进阶——XDC约束技巧之I/O篇 (下) - neufeifatonju的博客 - CSDN博客 https://blog.csdn.net/neufeifatonju/article/details/80450975

FPGA控制RGMII接口PHY芯片基础的更多相关文章

- 【重新发布,代码开源】FPGA设计千兆以太网MAC(1)——通过MDIO接口配置与检测PHY芯片

原创博客,转载请注明出处:[重新发布,代码开源]FPGA设计千兆以太网MAC(1)——通过MDIO接口配置与检测PHY芯片 - 没落骑士 - 博客园 https://www.cnblogs.com/m ...

- 以太网PHY 芯片之 MII/MDIO接口详解

本文主要分析MII/RMII/SMII,以及GMII/RGMII/SGMII接口的信号定义,及相关知识,同时本文也对RJ-45接口进行了总结,分析了在10/100模式下和1000M模式下的设计方法. ...

- 【RL-TCPnet网络教程】第5章 PHY芯片和STM32的MAC基础知识

第5章 PHY芯片和STM32的MAC基础知识 本章节为大家讲解STM32自带的MAC和PHY芯片的基础知识,为下一章底层驱动的讲解做一个铺垫. 5.1 初学者重要提示 5.2 ...

- 目标反射回波检测算法及其FPGA实现(准备篇): 用Verilog-HDL状态机控制硬件接口

基于FPGA的目标反射回波检测算法及其实现(准备篇) :用Verilog-HDL状态机控制硬件接口 前段时间,开发了一个简单的目标反射回波信号识别算法,我会分几篇文章分享这个基于FPGA的回波识别算法 ...

- 对于phy芯片的认识

一,关于phy芯片 以RTL8211E(G)为例 PHY是IEEE802.3中定义的一个标准模块,STA(station management entity,管理实体,一般为MAC或CPU) 通过SM ...

- 基于FPGA的PCIe接口实现(具体讲解了数据流向)

时间:2014-12-09 来源:西安电子科技大学电子工程学院 作者:姜 宁,陈建春,王 沛,石 婷 摘要 PCI Express是一种高性能互连协议,被广泛应用于网络适配.图形加速器.网络存储.大数 ...

- 88EE1111 PHY芯片设置

本次调试88EE1111 PHY芯片之主要目的主要对应为了将其默认的GMII接口通过配置成RGMII接口.因此,可能本文档涉及到的内容并没有涉及到PHY芯片的88EE1111所有内容. PHY芯片管理 ...

- mdio rgmii mac phy简单了解

MDIO(Management Data Input/Output),对G比特以太网而言,串行通信总线称为管理数据输入输出 (MDIO). 该总线由IEEE通过以太网标准IEEE 802.3的若干条款 ...

- 依赖注入(DI)与控制反转(IOC)基础知识

依赖注入(DI)与控制反转(IOC)基础知识 一.什么是依赖注入? 依赖注入英文是Dependcy Injection简写DI,依赖注入会将所依赖的对象自动交由目标对象使用,而不是让对象自己去获取. ...

随机推荐

- uni-app插件ColorUI步骤条

1. uni-app插件ColorUI步骤条 1.1. 前言 uni-app就不介绍了,前面几篇已经有所介绍,不知道的可以翻看我前面几篇博客 ColorUI-uniApp是uni-app的一款ui组件 ...

- Stage3D大冒险

摘自:http://dreamana.com/weblog/?p=92 摘自:http://baike.baidu.com/view/6794042.htm Stage3D的Flash Player和 ...

- Python基础(三)--流程控制之if、while、for,break与continue

一.流程控制之if……else…… if语句是指编程语言中用来判定所给定的条件是否满足,根据判定的结果(真或假)决定执行给出的两种操作之一 if 条件1: 缩进的代码块 elif 条件2: 缩进的代码 ...

- python调用函数设置超时机制

有时候需要给函数设置超时机制,以防止它卡住我们的程序,这里可以用python的signal模块,signal模块可以实现程序内部的信号处理. # coding:utf8 import time imp ...

- Colorimetry

[Colorimetry] 1.Example of Spectral Power Distribution Application An example of the spectral power ...

- 汉诺塔问题深度剖析(python实现)

当我们学习一门编程语言的时候,都会遇到递归函数这个问题.而学习递归的一个经典案例就是汉诺塔问题.通过这篇文章,观察移动三个盘子和四个盘子的详细过程,您不仅可以深刻的了解递归,也更加熟悉了汉诺塔的游戏的 ...

- DVWA的搭建

DVWA的搭建 一.DVWA是什么? 一款渗透测试演练系统,俗称靶机. 二.如何搭建? Linux有成套的靶机,直接打开使用就可以,下面开始介绍Windows 下DVWA的搭建. 运行phpstudy ...

- 搭建自己的docker镜像

手动构建 1.关键字查找镜像 sudo docker search centos 2.下载基本镜像 sudo docker pull centos 3.启动容器 sudo docker run -d ...

- 关于ID命名 一个页面唯一

1.一般ID在一个区域内必须是唯一的.这样是一个规范而且在IE中使用JS通过ID获取这个对象永远只能获取第一个. 2.js无法找到重复的ID,用js获取时,只能得到第一个ID元素,但,如果不同的区域范 ...

- Pandas | 02 Series 系列

系列(Series)是能够保存任何类型的数据(整数,字符串,浮点数,Python对象等)的一维标记数组.轴标签统称为索引. pandas.Series Pandas系列可以使用以下构造函数创建 - p ...