[原创][FPGA]时钟分频之奇分频(5分频)

0. 简介

有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录。

1. 奇分频

其实现很简单,主要为使用两个计数模块分别计数,得到两个波形进行基本与或操作完成。直接贴出代码部分如下。

module div_freq(

iCLK,

iRST_n,

oCLK

);

input wire iCLK;

input wire iRST_n;

output oCLK;

'd5;

reg clk_p;

:] cnt_p;

always @ (posedge iCLK or negedge iRST_n) begin

if (!iRST_n)

cnt_p <= 'd0;

)

cnt_p <= 'd0;

else

cnt_p <= cnt_p + 'b1;

end

always @ (posedge iCLK or negedge iRST_n) begin

if (!iRST_n)

clk_p <= 'b0;

) / )

clk_p <= ~clk_p;

)

clk_p <= ~clk_p;

else

clk_p <= clk_p;

end

reg clk_n;

:] cnt_n;

always @ (negedge iCLK or negedge iRST_n) begin

if (!iRST_n)

cnt_n <= 'd0;

)

cnt_n <= 'd0;

else

cnt_n <= cnt_n + 'b1;

end

always @ (negedge iCLK or negedge iRST_n) begin

if (!iRST_n)

clk_n <= 'b0;

) / )

clk_n <= ~clk_n;

)

clk_n <= ~clk_n;

else

clk_n <= clk_n;

end

assign oCLK = clk_p | clk_n;

endmodule

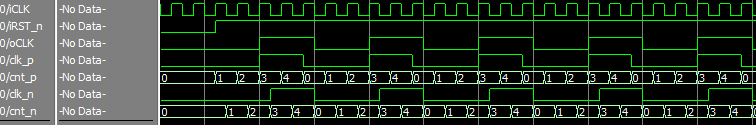

modelsim仿真结果如下图

[原创][FPGA]时钟分频之奇分频(5分频)的更多相关文章

- FPGA时钟分频(转)

http://www.cnblogs.com/fpga/archive/2009/10/24/1589318.html 占空比为50%的分频 偶数分频比较简单 比如N分频,那么计数到N/2-1,然后时 ...

- 一站式入口服务|爱奇艺微服务平台 API 网关实战 原创 弹性计算团队 爱奇艺技术产品团队

一站式入口服务|爱奇艺微服务平台 API 网关实战 原创 弹性计算团队 爱奇艺技术产品团队

- [原创][FPGA][IP-Core]altlvds_tx & altlvds_rx

1. 概述 Alter公司的QuartusII软件提供了LVDS发送和接收的IP核供我们使用,其在本质上可以理解为并行-串行数据的转换器.其在官方文档(见附件)上也这样说过.其中的应用场景有告诉AD/ ...

- [原创][FPGA]有限状态机FSM学习笔记(一)

1. 概述--何为有限状态机FSM? 有限状态机-Finite State Machine,简写为FSM,是表示有限个状态及在这些状态之间的转移和动作等行为的数学模型,在计算机领域有着广泛的应用.通常 ...

- [原创]FPGA JTAG工具设计(二)

经过前期打样 基于FT2232H的JTAG &UART板级已经初步形成 在Viado环境和ISE(13.2+)环境可以使用 速度支持10MHz/15MHz/30MHz 在ISE iMpact下 ...

- [原创]FPGA JTAG工具设计(一)

先来看不同JTAG方案,下载配置QSPI Flash所耗时间 基于FTDI方案,JTAG下载时间为494sec JTAG chain configuration ------------------- ...

- [原创][FPGA]Quartus实用小技巧(长期更新)

0. 简介 在使用Quartus软件时,经常会时不时的发现一些小技巧,本文的目的是总结所查阅或者发现到的小技巧,本文长期更新. 1. Quartus中的模板功能 最近在Quartus II的菜单里找到 ...

- [原创][FPGA]Quartus中调用Modelsim波形仿真步骤说明

0. 简介 在使用QuartusII软件的过程中,经常地需要跑仿真,那么说到仿真就不得不说Modelsim这个仿真软件了,我们这里介绍下该软件在QuartusII中的使用方法. 1. 建立Quartu ...

- FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

原理介绍 1.分频 FPGA设计中时钟分频是重要的基础知识,对于分频通常是利用计数器来实现想要的时钟频率,由此可知分频后的频率周期更大.一般而言实现偶数系数的分频在程序设计上较为容易,而奇数分频则相对 ...

随机推荐

- VNC远程登录端使用经验之一

1.vnc/xmanager都是经常用的远程登录软件.vnc有个缺点就是他的进程不会自动退出比如如果开了PID1再去开PID2...PIDn.那么前面的PIDn-1个进程就会一直运行如果不手动kill ...

- Python入门学习笔记2:刷题

1) LeetCode 强的面试题和算法题,要求也比较高,很多国内外的码农在上面刷题.难度从easy到hard都有,而且覆盖面极广,需要你的综合实力去答题. 最简单的题比如字符串的处理有的时候也要用到 ...

- exp分析

1 from pwn import* 2 3 local =1 4 debug = 1 5 6 if local: 7 p = process('./pwn1') 8 else: 9 p = remo ...

- LeetCode(23)Merge k Sorted Lists

题目 Merge k sorted linked lists and return it as one sorted list. Analyze and describe its complexity ...

- CodeForce:16C-Monitor

传送门:http://codeforces.com/problemset/problem/16/C Monitor time limit per test0.5 second memory limit ...

- install redis and used in golang on ubuntu 14.04

$ wget http://download.redis.io/releases/redis-3.0.3.tar.gz$ tar xzf redis-3.0.3.tar.gz$ cd redis-3. ...

- UVa 12299 线段树 单点更新 RMQ with Shifts

因为shift操作中的数不多,所以直接用单点更新模拟一下就好了. 太久不写线段树,手好生啊,不是这错一下就是那错一下. PS:输入写的我有点蛋疼,不知道谁有没有更好的写法. #include < ...

- monkey测试工具与常用的linux命令

Monkey测试工具 说明:monkey是一个安卓自带的命令行工具,可以模拟用户向应用发起一定的伪随机事件.主要用于对app进行稳定性测试与压力测试. 实现:首先需要安装一个ADB工具,安装完之后,需 ...

- [python工具][2]sublime的快捷键

十.Sublime Text 快捷键列表 快捷键按类型分列如下: 1.通用 ↑↓← → 上下左右移动光标 Alt 调出菜单 Ctrl + Shift + P 调出命令板(Comma ...

- pl/sql 函数及与存储过程的区别

函数用于返回特定的数据,当建立函数时,在函数头部必须包含return子句.而在函数体内必须包含return语句返回的数据.我们可以使用create function来建立函数. 1).接下来通过一个案 ...