UltraFast设计法实践(1) -- 初始设计检查

平台:Vivado16.4

芯片:xc7a200

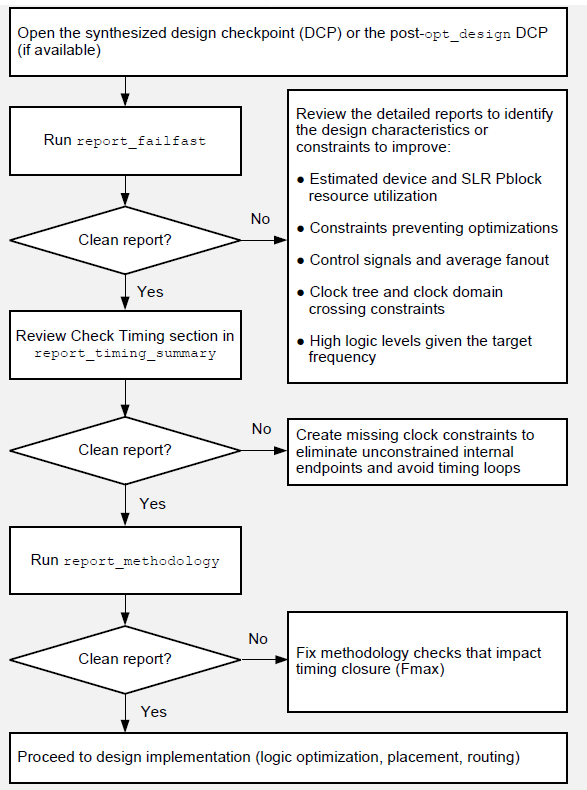

《UltraFast Design Methodology Timing Closure Quick Reference Guide 》(UG1292)第一页的主题是初始设计检查,这一步是针对综合后或者opt_design阶段生成的dcp,该阶段主要要读懂三个操作生成的报告,这三个操作是:

- report_failfast

- report_timing_summary

- report_methodology

1. report_failfast

1.1 命令使用

有的平台一开始并不能直接使用report_failfast命令,需要安装Xilinx Tcl Store,安装方法见:干掉Vivado幺蛾子(1)-- Xilinx Tcl Store。

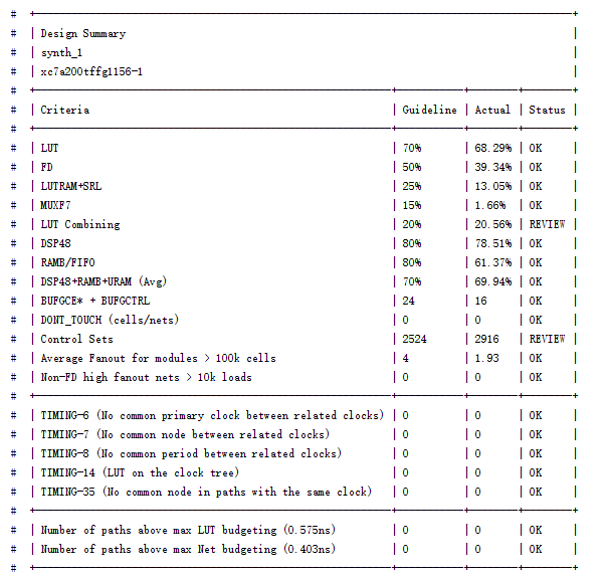

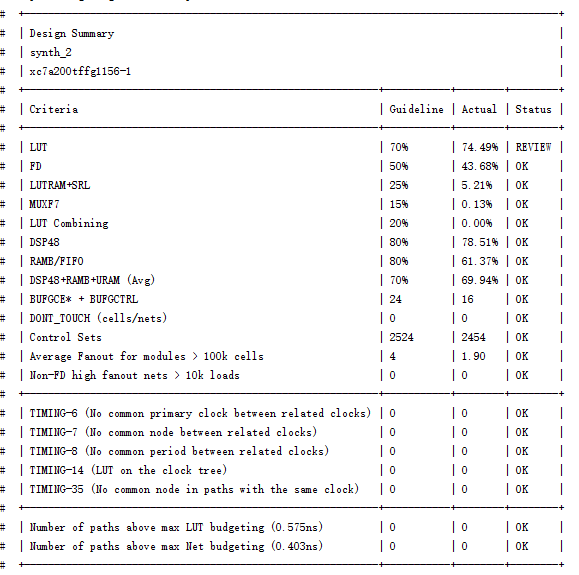

在工程综合完成之后,需要打开synthesized design(open synthesized design),使用Tcl命令:xilinx::designutils::report_failfast ,会在Tcl Console窗口得到一张图表,如下图所示:

这张表反映的是工程对资源的使用情况,包括参考(推荐)比例、实际比例和状态。当各项实际使用率都符合参考的话,工程进行后续的过程才会相对可靠。我们尤其要关注状态为“REVIEW”的项,它表示超过的参考推荐值,可能存在风险。

我的报告中状态为“review”的有两项:LUT Combining和Control Sets。

1.2 优化

1. 2.1 LUT Combining

先看LUT Combining,查阅《UltraFast Design Methodology Guide for the Vivado Design Suite》(UG949)中关于它的含义。文中对其的描述如下:

LUT combining reduces logic utilization by combining LUT pairs with shared inputs into single dual-output LUTs that use both O5 and O6 outputs. However, LUT combining can potentially increase congestion because it tends to increase the input/output connectivity for the slices. If LUT combining is high in the congested area (> 40%), you can try using a synthesis strategy that eliminates LUT combining to help alleviate congestion. The Flow_AlternateRoutability synthesis strategy and directive instructs the synthesis tool to not generate any additional LUT combining.

大意是有的LUT pairs共用一些LUT的输入,从而把O5和O6都用上,然后导致线路拥堵。

随后看到这样一个tip:

意思是让我执行report_qor_suggestions,试试看,反馈了一些结果,建议opt_design -remap,完成之后再report_failfast,结果反而恶化,但LUT使用减少,如下图

随后,UG949中建议尝试方法:

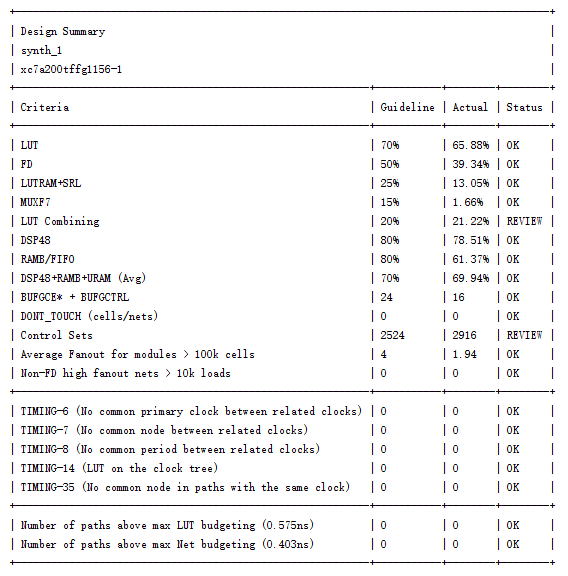

- synthesis setting -- strategy -- Flow_AlternateRoutability

说可以采取修改综合策略的方式来优化,将策略改为Flow_AlternateRoutability可以减少LUT combining,从而可以优化拥堵的情况。改后综合,report_failfast报告如下,LUT combining确实减少了,但LUT增加了,这是可以理解的,因为LUT Combining就是复用一些LUT的结果,现在不复用了,所以LUT的使用率增加了。

1.2.2 control_sets

先不管LUT,因为这个可以后期优化掉或者精简代码实现。现在只剩control_sets了,查UG949中对control_sets的描述,如下:

Often not much consideration is given to control signals such as resets or clock enables. Many designers start HDL coding with "if reset" statements without deciding whether the reset is needed or not. While all registers support resets and clock enables, their use can significantly affect the end implementation in terms of performance, utilization, and power.

大致理解是跟一些使能或者复位信号的不合理使用相关。使用report_control_sets -verbose 获取control_sets的详细情况,貌似是导致control_sets的一些设计,然后发现我的模块中大量的跟以下这样一个信号有关,而这个信号大量的作为使能信号。

assign w_divisor_valid = (mult_cnt == 6'd39); // control set 过高可能有这个原因

这样设计是有问题的,故改为时序设计:

always@(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0) begin

w_divisor_valid <= 1'b0;

end

else if(mult_cnt == 6'd38) begin

w_divisor_valid <= 1'b1;

end

else begin

w_divisor_valid <= 1'b0;

end

end

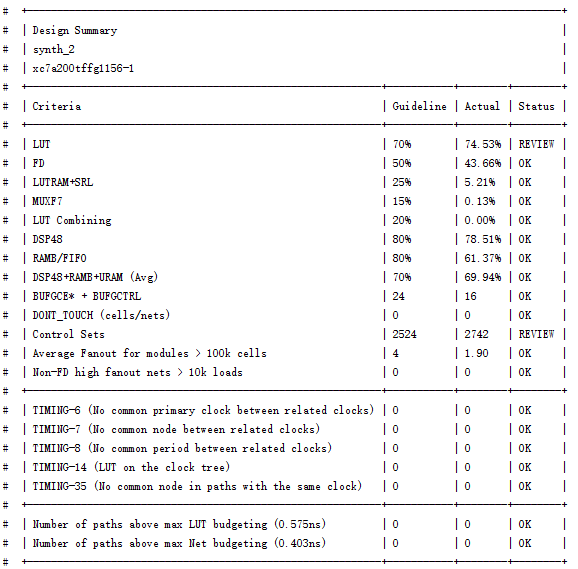

之后,再综合--report_failfast,满足要求了!!

1.3.总结

report_failfast生成的项目报告,查看哪些项是REVIEW,然后针对每项内容是什么含义,导致的可能原因,建议的优化方法等都可以从UG949中查看,不断反复尝试,直至可以接受的结果为止。

2.report_timing_summary

report_timing_summary可以生成时序报告,除了查看时序违例路径之外,该报告还可显示时序约束是否存在潜在问题。注意:此阶段主要关注的是主要的时钟约束有没有加上?有没有loop? 即基本的时序设计有没有问题,至于一些时序裕量不足的情况,个人认为,此阶段要完全解决是不太现实的。毕竟这是设计初期,想要解决所有问题是不可能的,后面还有很多优化过程要完成。

3. report_methodology

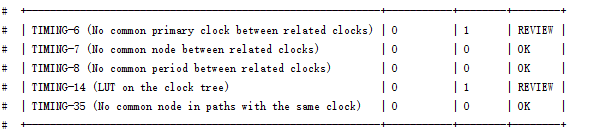

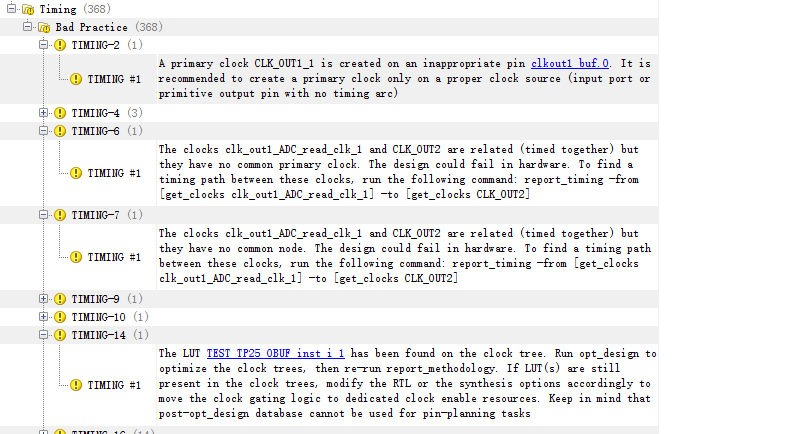

在有个工程的report_failfast报告中,有几项有关TIMING的项报REVIEW,看不出哪个条线路或者环节出了问题,从UG949中并不能找到详细的答案,这个时候就需要用到report_methodology。

执行该命令,主要检查的是涉及到时钟的RTL代码设计,尤其需要关注Bad Practice,这就会详细的风险问题出在哪个环节。

4. 总结

第一阶段的初始设计检查主要根据report_failfast报告的内容逐一优化REVIEW项,结合report_timing_summary和report_methodology 生成的报告,看看RTL和时序层面有没有设计问题,反复迭代,尽可能使三个报告“干净”。再次强调(当然是个人拙见),初期解决所谓时序问题是不太现实的,后面还有很长的优化过程,也许还有不断反复迭代,

5.遗留问题

- 实际上在report_failfast报告中有关TIMING的几项,并没有很好的理解其中的含义,换言之,为什么会出这些问题,时钟之间到底存在哪些关系。

参考文献:

- UG949

- UG1292

- 深度解析ug1292(1)

UltraFast设计法实践(1) -- 初始设计检查的更多相关文章

- 《UltraFast设计法实践》系列目录

最近准备开始潜心学习快速和高效的时序收敛设计了,突然想就把整个学习过程做成一个博客系列吧,虽然想想就很激动(技术狗就这么点出息--),但希望坚持下来. 这篇做个目录或者索引,不断向其中添加学习内容. ...

- 来自Google资深工程师的API设计最佳实践

来自Google资深工程师Joshua Bloch的分享:API设计最佳实践 为什么API设计如此重要?API是一个公司最重要的资产. 为什么API的设计对程序员如此重要? API一旦发布,出于兼容性 ...

- Apache Beam实战指南 | 大数据管道(pipeline)设计及实践

Apache Beam实战指南 | 大数据管道(pipeline)设计及实践 mp.weixin.qq.com 策划 & 审校 | Natalie作者 | 张海涛编辑 | LindaAI 前 ...

- RESTful API 设计最佳实践

背景 目前互联网上充斥着大量的关于RESTful API(为了方便,以后API和RESTful API 一个意思)如何设计的文章,然而却没有一个"万能"的设计标准:如何鉴权?API ...

- atitit.基于http json api 接口设计 最佳实践 总结o7

atitit.基于http json api 接口设计 最佳实践 总结o7 1. 需求:::服务器and android 端接口通讯 2 2. 接口开发的要点 2 2.1. 普通参数 meth,p ...

- ****RESTful API 设计最佳实践(APP后端API设计参考典范)

http://blog.jobbole.com/41233/ 背景 目前互联网上充斥着大量的关于RESTful API(为方便,下文中“RESTful API ”简写为“API”)如何设计的文章,然而 ...

- RESTful API 设计最佳实践(转)

摘要:目前互联网上充斥着大量的关于RESTful API(为了方便,以后API和RESTful API 一个意思)如何设计的文章,然而却没有一个”万能“的设计标准:如何鉴权?API格式如何?你的API ...

- RESTful API 设计最佳实践(转)

背景 目前互联网上充斥着大量的关于RESTful API(为方便,下文中“RESTful API ”简写为“API”)如何设计的文章,然而却没有一个”万能“的设计标准:如何鉴权?API 格式如何?你的 ...

- RESTful API 设计最佳实践【转】

背景 目前互联网上充斥着大量的关于RESTful API(为了方便,后面API和RESTful API 一个意思)如何设计的文章,然而却没有一个“万能”的设计标准:如何鉴权?API格式如何?你的API ...

随机推荐

- mybatis思维导图(一)

写在前面 与hibernate相比,我无疑更喜欢mybatis,就因为我觉得它真的好用,哈哈.它简单上手和掌握:sql语句和代码分开,方便统一管理和优化:当然缺点也有:sql工作量很大,尤其是字段多. ...

- React相关知识和经验的碎片化记录

React相关知识和经验的碎片化记录 1.Warning: validateDOMNesting(...): Whitespace text nodes cannot appear as a chil ...

- 下拉菜单--JavaScript触发方法

1. $(function(){ $(".dropdown-toggle").one("click",function(){ $(this).dropdown( ...

- mac安装mysql及终端操作mysql与pycharm的数据库可视化

一.Mac安装mysql 首先下载mysql,地址:https://dev.mysql.com/downloads/mysql/ 然后已知安装就好了,会出现让你记住密码的提示,然后就安装好了.... ...

- win7下cygwin命令行颜色和中文乱码解决

在cygwin虚拟机中可以使用ls命令等Linux下的一些命令,如果在win下将环境变量path中添加x:\cygwin\bin(x:指的是cygwin所在的盘符),可以在cmd环境中使用这些命令,而 ...

- Materialize——扁平化卡片式网页模板

Materialize 官网:http://www.materialscss.com/ 下载 http://pan.baidu.com/s/1kUUX2Vt CSS 颜色 背景色 <div cl ...

- centos 7 Hadoop2.7.4完全分布式搭建(一)

(一)系统准备与安装 1.准备下载centos7 (百度自行下载)可以到开源镜像站下载,速度比较快,比如清华的或者阿里的 在vmware上安装 这里我用的是vmware12 打开Vmware 选择文件 ...

- DLL的概念、dll导出类(转贴)

1. DLL的概念DLL(Dynamic Linkable Library),动态链接库,可以向程序提供一些函数.变量或类.这些可以直接拿来使用.静态链接库与动态链接库的区别:(1)静态链接库与动态链 ...

- C++ 调用C++写的类库的2种方法之一(隐式链接)

一:创建C++ DLL类库,名称:Dll1 1.Dll1.h /*#ifndef Dll_API #else #define Dll_API _declspec(dllimport) #endif * ...

- Partition--分区总结

1. 在SQL SERVER 2008 R2 SP2之前版本,对分区只支持到1000个分区,之后版本支持到15000个分区.2. 分区索引对齐并不要求索引和表使用同一分区方案,但要求两者使用的分区方案 ...