xilinx fpga中块ram的使用——简单双端口ram的使用

在简单双端口ram中最简单有9个端口:分别是

clka 为输入端口的时钟

wea 读写控制端,高为写,低为读

addra 写地址

dina 待写入的数据

clkb 为输出端口的时钟的

addrb 读地址

doutb 读出的数据

在ip核中还可以加入ena/enb端口,这两个端口的作用是控制相应写入和读出端口的数据,为高是正常写入或读出,为低时写入为0,读出为0。

也可以加入复位端口rst,不过复位有两种优先级CE和SR,选择CE时,rst的优先级低于ENA的优先级;选择SR时,rst的优先级高于ENA的优先级。

还可以选择复位的方式,同步还是异步,一般选择同步。

端口介绍完后,就开始使用双端口ram,工作方式是:可以写入也可以预先用coe文件存入数据,写入数据后就可以读取数据了 ,这里的读取数据和rom的相同,写入地址是多少,就去读取相应地址的数据。

双端口ram和单端口的ram不同,单端口的ram读取数据方式是,写入数据的下一个时钟自动输出数据,仅可用于流水线式数据处理。

这里写了一个简单双端口的ram测试代码

`timescale 1ns / 1ps

`define clk_period

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 11:39:21 06/04/2018

// Design Name: ram

// Module Name: E:/digital image processing/finial_code/ram_test/testbench/ram_tb.v

// Project Name: ram_test

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: ram

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////// module ram_tb; // Inputs

reg clka;

reg ena;

reg [:] wea;

reg [:] addra;

reg [:] dina;

reg clkb;

reg enb;

reg [:] addrb;

reg clk; // Outputs

wire [:] doutb; // Instantiate the Unit Under Test (UUT)

ram uut (

.clka(clk),

.ena(ena),

.wea(wea),

.addra(addra),

.dina(dina),

.clkb(clk),

.enb(enb),

.addrb(addrb),

.doutb(doutb)

);

integer i;

initial clk = ;

always #(`clk_period/)clk = ~clk;

initial begin

// Initialize Inputs

ena = ;

enb = ;

wea = ;

dina = ;

addra = ;

addrb = ;

#(`clk_period* + );

for (i=;i<=;i=i+)begin

wea = ;

dina = - i;

addra = i;

#`clk_period;

end

wea = ;

#(`clk_period*);

/*for (i=0;i<=15;i=i+1)begin

addrb = i;

#`clk_period;

end */

addrb = ;

#`clk_period;

addrb = ;

#`clk_period;

addrb = ;

#`clk_period; // Wait 100 ns for global reset to finish

#; // Add stimulus here end endmodule

testbench

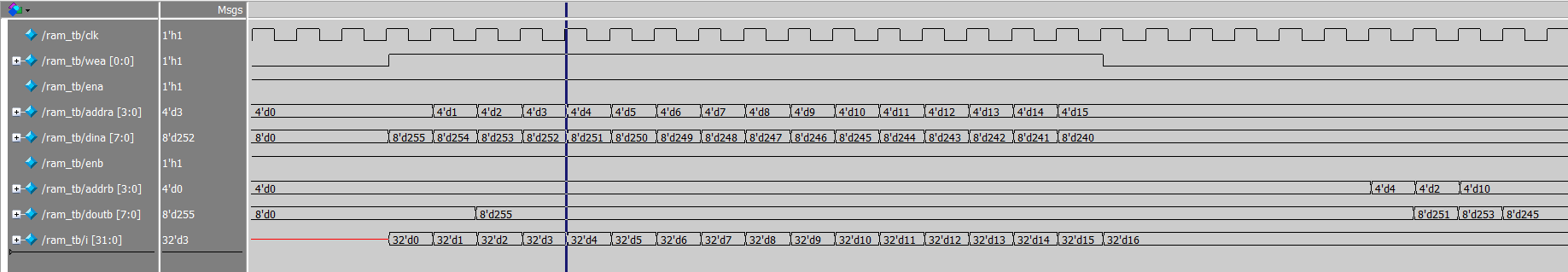

modelsim的仿真结果为:

xilinx fpga中块ram的使用——简单双端口ram的使用的更多相关文章

- (Xilinx)FPGA中LVDS差分高速传输的实现

https://wenku.baidu.com/view/24e8bad86f1aff00bed51ef8.html

- 你真的会Xilinx FPGA的复位吗?

Get Smart About Reset: Think Local, Not Global. 对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间内都是将复位信号作为一个I/O口, ...

- 巧用FPGA中资源

随着FPGA的广泛应用,所含的资源也越来越丰富,从基本的逻辑单元.DSP资源和RAM块,甚至CPU硬核都能集成在一块芯片中.在做FPGA设计时,如果针对FPGA中资源进行HDL代码编写,对设计的资源利 ...

- Xilinx FPGA结构

FPGA是什么?FPGA是现场可编程逻辑阵列,由可编程逻辑资源(LUT和 REG),可编程连线,可编程I/O构成.Xilinx的FPGA的基本结构是一样的,但随着半导体工艺的发展,FPGA的逻辑容量越 ...

- Xilinx FPGA LVDS应用

最近项目需要用到差分信号传输,于是看了一下FPGA上差分信号的使用.Xilinx FPGA中,主要通过原语实现差分信号的收发:OBUFDS(差分输出BUF),IBUFDS(差分输入BUF). 注意在分 ...

- FPGA中RAM使用探索

FPGA中RAM的使用探索.以4bitX4为例,数据位宽为4为,深度为4. 第一种方式,直接调用4bitX4的RAM.编写控制逻辑对齐进行读写. quartus ii 下的编译,资源消耗情况. 85C ...

- 理解FPGA中的RAM、ROM和CAM;ROM、RAM、DRAM、SRAM、FLASH

目前大多数FPGA都有内嵌的块RAM(Block RAM),可以将其灵活地配置成单端口RAM(DPRAM,Single Port RAM).双端口RAM(DPRAM,Double Ports RAM) ...

- Xilinx FPGA引脚txt文件导入excel中

需求 为了把xilinx FPGA的官方引脚文件txt转成excel文件(实际官网中有对应的csv文件就是excel文件了...) xilinx FPGA引脚地址:https://china.xili ...

- 关于Xilinx FPGA JTAG下载时菊花链路中的芯片数量

关于Xilinx FPGA JTAG下载时菊花链路中的芯片数量 emesjx | 2014-08-13 13:13:30 阅读:1793 发布文章 当一个系统中含有多片(2片以上)Xil ...

随机推荐

- synchronized与锁升级

1 为什么需要synchronized? 当一个共享资源有可能被多个线程同时访问并修改的时候,需要用锁来保证数据的正确性.请看下图: 线程A和线程B分别往同一个银行账户里面添加货币,A线程从内存中读取 ...

- EJB JMS javax.naming.NameNotFoundException: XXX not bound

练习EJB MessageDrivenBean时部署不成功,一直报错 09:57:29,017 WARN [JmsActivation] Failure in jms activation org.j ...

- JavaWeb网上图书商城完整项目-数据库操作工具类

1.首先安装数据库,在windows上安装和在unix上面安装环境不一样,我在自己的本地电脑上安装,安装成功之后,如果使用navicat远程工具访问,需要允许mysql远程能被访问 方法二.直接授权( ...

- C# 9.0 终于来了, Top-level programs 和 Partial Methods 两大新特性探究

一:背景 1. 讲故事 .NET 5 终于在 6月25日 发布了第六个预览版,随之而来的是更多的新特性加入到了 C# 9 Preview 中,这个系列也可以继续往下写了,废话不多说,今天来看一下 To ...

- 平时自己常用的git指令

增删改查 创建标签 $ git tag -a v1.4 -m 'my version 1.4' 用 -a (译注:取 annotated 的首字母)指定标签名字即可 -m 选项则指定了对应的标签说明 ...

- CImage显示位图与CDC双缓冲冲突,使用路径层解决.

2010年04月29日 星期四 20:35 位图闪的问题困扰我很久了,因为程序的需要,我显示位图的方式是CImage类. 如果从CImage转到CBitmap,之后使用Attach到是可以,但我发现这 ...

- BootstrapDialog.show - 提示信息对话框

外文资料:http://nakupanda.github.io/bootstrap3-dialog/ (1)最简单的实现方式: BootstrapDialog.show({ message: 'Hi ...

- Python3笔记014 - 3.5 跳转语句

第3章 流程控制语句 3.5 跳转语句 1.break 语句 while 条件表达式1: 语句块1 if 条件表达式2: break for 迭代变量 in 对象: 语句块1 if 条件表达式: br ...

- (私人收藏)商务工作学习万能简约大气PPT模板

商务工作学习万能简约大气PPT模板 https://pan.baidu.com/s/1aPnPZ285N5VSSErro1cPngehoa

- 虚拟机 - NAT模式下设置静态 IP 地址

背景 如果不给虚拟机设置静态 IP 地址的话,每次重启机器都会自动分配一个新的 IP 如果有多台虚拟机的话,也会动态获取 IP 动态IP的话,每次 设置静态 IP 的步骤 查看本机 IP 和网关 cm ...