FPGA 流水灯

VerilogHDL那些事儿_建模篇(黑金FPGA开发板配套教程)

作者:akuei2

说明:参照该书将部分程序验证学习一遍

学习时间:2014年5月2号

主要收获:

1. 对FPGA有初步了解;

2. 功能模块和控制模块;

3. 并行操作的思维;

4. 使用"并行操作"进行流水灯实验。

FPGA是什么?

1. 一个很好的比喻是:FPGA是"一堆乐高积木",而Verilog是"搭积木的手"。FPGA并没有实际的形状,要通过Verilog描述出形状来。

2. 新手们常常忽略了,FPGA其实是并存着"顺序操作"和"并行操作"的操作概念。如果打从一开始就忽略了它们,往后的日子很难避免遇见瓶颈。

过程赋值和assign连续赋值:

1. 过程赋值改变一个寄存器的状态,是时序逻辑,用在initial和always里面;

2. 连续赋值是组合逻辑,驱动线型变量(wire)。

流水灯实验:

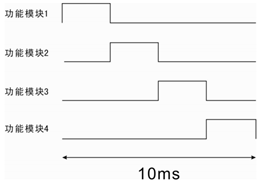

1. 系统整体模块以及每个功能模块示意图:

2. RTL原理图

RTL(寄存器传输级):描述数据在寄存器之间怎么流动和如何处理这些数据的模型。

3. 控制模块为top_module,功能模块有led1_module~led4_module。

module top_module(CLK, RSTn, LED_Out);

input CLK;

input RSTn;

output [3:0]LED_Out;

wire LED1_Out;

led1_module U1

(

.CLK(CLK),

.RSTn(RSTn),

.LED_Out(LED1_Out)

);

wire LED2_Out;

led2_module U2

(

.CLK(CLK),

.RSTn(RSTn),

.LED_Out(LED2_Out)

);

wire LED3_Out;

led3_module U3

(

.CLK(CLK),

.RSTn(RSTn),

.LED_Out(LED3_Out)

);

wire LED4_Out;

led4_module U4

(

.CLK(CLK),

.RSTn(RSTn),

.LED_Out(LED4_Out)

);

assign LED_Out = {LED4_Out, LED3_Out, LED2_Out, LED1_Out};

endmodule

module led1_module(CLK, RSTn, LED_Out);

input CLK;

input RSTn;

output LED_Out;

parameter T10MS = 2'd3;

reg[1:0]Count1;

always@(posedge CLK or negedge RSTn)

if(!RSTn)

Count1 <= 2'd0;

else if(Count1 == T10MS)

Count1 <= 2'd0;

else

Count1 <= Count1 + 1'b1;

reg rLED_Out;

always@(posedge CLK or negedge RSTn)

if(!RSTn)

rLED_Out <= 1'b0;

else if(Count1 == 2'd0)

rLED_Out <= 1'b1;

else

rLED_Out <= 1'b0;

assign LED_Out = rLED_Out;

endmodule

4. 仿真如下:

知识点~~~

1. 硬件描述语言 Hardware Description Language;

2. HDL采用自顶向下的电路设计方法,主要可以分为五个抽象层次:

3. HDL语言是有时序概念的,这和平常的编程语言不一样。

FPGA 流水灯的更多相关文章

- FPGA——流水灯(一)

对于FPGA的结构原理,先不进行全面的了解,先能根据教程程序看得懂,写得出来跑起来.慢慢的了解程序运行的原理,各种语法的使用. 今天对流水的程序有一个认识,熟悉软件的使用,语法规则,原理.以正点原子的 ...

- 第一个FPGA工程—LED流水灯

这一章我们来实现第一个FPGA工程-LED流水灯.我们将通过流水灯例程向大家介绍一次完整的FPGA开发流程,从新建工程,代码设计,综合实现,管脚约束,下载FPGA程序.掌握本章内容,大家就算正式的开始 ...

- 【黑金原创教程】【FPGA那些事儿-驱动篇I 】【实验一】流水灯模块

实验一:流水灯模块 对于发展商而言,动土仪式无疑是最重要的任务.为此,流水灯实验作为低级建模II的动土仪式再适合不过了.废话少说,我们还是开始实验吧. 图1.1 实验一建模图. 如图1.1 所示,实验 ...

- NIOS ii 流水灯

为了做项目的前期验证工作,实验室购买了某开发板,下面是基于该板子的实现过程.作为笔记记录,供入门者参考. 1:创建一个Quartus II的工程 next选择器件,然后finish.我的器件是cycl ...

- Xilinx Vivado的使用详细介绍(4):Zedboard+vivado之流水灯(加SDK)

Vivado+zedboard之初学流水灯 Author:zhangxianhe 环境:vivado 2016.3(已验证适用于2015.4) 开发板:Zedboard version xc7z020 ...

- 【接口时序】2、Verilog实现流水灯及与C语言的对比

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1.FPGA型号:XC6SLX45 ...

- Zedboard学习(三):PL下流水灯实验 标签: fpgazynqPL 2017-07-05 11:09 21人阅读 评论(0)

zynq系列FPGA分为PS部分和PL部分. PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分. PS: 处理系统 (Processing System) , 就是与F ...

- S5PV210_流水灯

1.整体思路:把相应的配置数据写入相应的寄存器,控制GPIO电平(Led.s)——运用工程管理Makefile编译.链接文件(由Led.s编译得到led.bin,该文件用于USB启动方式点亮LED,若 ...

- (一)GPIO 编程实验 LED 流水灯控制

7个寄存器 是R1-R16.(当然,里面有很多是分几个模式的,所以总共有37个)类似于单片机的R0-R7. GPXCON,GPXDAT等等是另外的寄存器,应该叫,特殊功能寄存器,类似于单片机的P0,P ...

随机推荐

- 企业级docker-registry原生镜像仓库高可用部署

简介: 私有镜像仓库可以方便企业,或个人开发者共享内部镜像而不会泄漏私有代码,而且可以加速镜像的拉取.能更加方便得集成到容器化的 CI/CD 中去.也可建立自己的公共镜像仓库. 优势: Docker ...

- python使用pandas进行数据处理

pandas数据处理 关注公众号"轻松学编程"了解更多. 以下命令都是在浏览器中输入. cmd命令窗口输入:jupyter notebook 打开浏览器输入网址http://loc ...

- Java安全之RMI反序列化

Java安全之RMI反序列化 0x00 前言 在分析Fastjson漏洞前,需要了解RMI机制和JNDI注入等知识点,所以本篇文来分析一下RMI机制. 在Java里面简单来说使用Java调用远程Jav ...

- Git撤销文件修改

在旧版本中,git的撤销工作区的文件修改是用git checkout -- <file>命令,由于容易漏了--导致和切换分支混肴,所以新版本中: - 使用git restore (--wo ...

- 对比JAVA、Python、C、Go运行时间,我惊呆了!!!

对比JAVA.Python.C.Go运行时间,我惊呆了!!! 周末在寝室刷完算法,想放松一下,于是做了一个实验:用现在主流的几种编程语言对0 - (10000000 - 1)求和,结果我惊呆了,话不多 ...

- OJ-1:时钟问题【九度1553】

题目描述: 如图,给定任意时刻,求时针和分针的夹角(劣弧所对应的角). 输入: 输入包含多组测试数据,每组测试数据由一个按hh:mm表示的时刻组成. 输出: 对于每组测试数据,输出一个浮点数,代表时针 ...

- 对List对象里的其中两个属性配套去重

List<User> disList= list.stream().collect(Collectors.collectingAndThen(Collectors.toCollection ...

- Linux系统下用户如何膝盖FTP用户密码

其实修改ftp用户密码与修改普通用户的密码的过程是一眼高的其具体步骤如下 1.用root账户登录系统 2.使用passwd命令修改密码: 第一次输入密码后提示:The password fails t ...

- 数据采集与融合第四次作业:多线程以及scrapy框架的使用

数据采集第四次作业:多线程以及scrapy框架的使用 任务一:单多线程的使用 单线程代码: from bs4 import BeautifulSoup from bs4 import UnicodeD ...

- ubuntu13.04修改默认启动内核

ubuntu下面的启动内核选项跟其他操作系统不一样,有个子菜单,比如我在默认的ubuntu13.04上安装了一个新的内核3.14.5,那么默认的第一项是3.14.5内核,第二项是一个子菜单,第二项里面 ...