8421BCD转余3码Verilog HDL的设计(1)

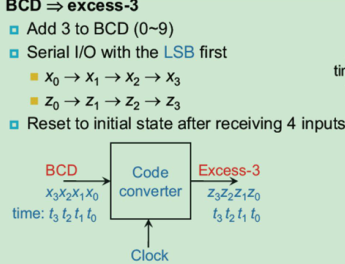

近期阅读Verilog HDL高级数字设计(第二版)中,遇到了串行比特流BCD码转余3码转换器的设计,比较独特的是:

(1)该转换器的输入为1位串行比特流,输出也为1位串行比特流。

BCD码与余三码的转换关系如下:

8421BCD码=余3码+0011

| 10进制 | 8421BCD码 | 余3码 | 10进制 | 8421BCD码 | 余3码 |

| 0 | 0000 | 0011 | 8 | 1000 | 1011 |

| 1 | 0001 | 0100 | 9 | 1001 | 1100 |

| 2 | 0010 | 0101 | 10 | 1010 | 1101 |

| 3 | 0011 | 0110 | 11 | 1011 | 1110 |

| 4 | 0100 | 0111 | 12 | 1100 | 1111 |

| 5 | 0101 | 1000 | 13 | 1101 | 10000 |

| 6 | 0110 | 1001 | 14 | 1110 | 10001 |

| 7 | 0111 | 1010 | 15 | 1111 | 10010 |

由表1可知,当8421BCD码为13、14、15时候,余三码已经超出了4位二进制能表示的范围(无符号数0~15),因此本次中暂不考虑。

转换器的输入为1位串行比特流,输出为1位相应余三码的串行比特流,设计思路如下:

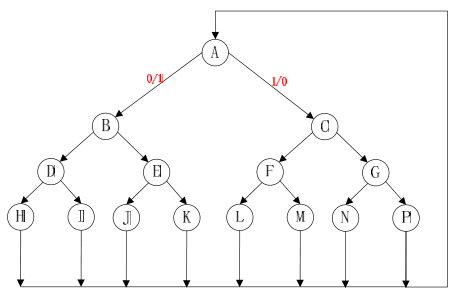

图1 状态转换示意图

设BCD码输入比特流Bin在t0,t1,t2,t3的输入分别为t0t1t2t3,设余三码输出比特流Bout在t0,t1,t2,t3时刻的输出分别为T0T1T2T3

假设转换器的初始状态为状态A:

(1)在状态A下,t0时刻Bin输入的值可能为0或者1:当bin输入0时,进入B状态;当bin输入1时,进入C状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

A状态(t0时刻,Bin=0),Bout=1 |

A状态(t0时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:B | t3t2t1t0 | T3T2T1T0 | 下一个状态:C |

| 0000 | 0011 | 0001 | 0010 | ||

| 0010 | 0101 | 0011 | 0110 | ||

| 0100 | 0111 | 0101 | 1000 | ||

| 0110 | 1001 | 0111 | 1010 | ||

| 1000 | 1011 | 1001 | 1100 | ||

| 1010 | 1101 | 1011 | 1110 | ||

| 1100 | 1111 | 1101 | (1)0000 | ||

(2)在B状态,t1时刻Bin输入的值可能为0或者1:当bin输入0时,进入D状态;当bin输入1时,进入E状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

B状态(t1时刻,Bin=0),Bout=1 |

B状态(t1时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:D | t3t2t1t0 | T3T2T1T0 | 下一个状态:E |

| 0000 | 0011 | 0010 | 0101 | ||

| 0100 | 0111 | 0110 | 1001 | ||

| 1000 | 1011 | 1010 | 1101 | ||

| 1100 | 1111 | 1110 | (1)0001 | ||

(3)在D状态,t2时刻Bin输入的值可能为0或者1:当bin输入0时,进入H状态;当bin输入1时,进入I状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

D状态(t2时刻,Bin=0),Bout=0 |

E状态(t2时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:H | t3t2t1t0 | T3T2T1T0 | 下一个状态:I |

| 0000 | 0011 | 0100 | 0111 | ||

| 1000 | 1011 | 1100 | 1111 | ||

(4)在H状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

H状态(t3时刻,Bin=0),Bout=0 |

H状态(t3时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:A | t3t2t1t0 | T3T2T1T0 | 下一个状态:A |

| 0000 | 0011 | 1000 | 1011 | ||

(5)在I状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

I状态(t3时刻,Bin=0),Bout=0 |

I状态(t3时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:A | t3t2t1t0 | T3T2T1T0 | 下一个状态:A |

| 0100 | 0111 | 1100 | 1111 | ||

(6)在E状态,t2时刻Bin输入的值可能为0或者1:当bin输入0时,进入J状态;当bin输入1时,进入K状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

E状态(t2时刻,Bin=0),Bout=1 |

E状态(t2时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:J | t3t2t1t0 | T3T2T1T0 | 下一个状态:K |

| 0010 | 0101 | 0110 | 1001 | ||

| 1010 | 1101 | 1110 | (1)0001 | ||

(7)在J状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

J状态(t3时刻,Bin=0),Bout=0 |

J状态(t3时刻,Bin=1),Bout=1 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:A | t3t2t1t0 | T3T2T1T0 | 下一个状态:A |

| 0010 | 0101 | 1010 | 1101 | ||

(8)在K状态,t3时刻Bin输入的值可能为0或者1:当bin输入0时,进入A状态;当bin输入1时,进入A状态

比特流Bin二进制为t3t2t1t0的可能性如下:

|

K状态(t3时刻,Bin=0),Bout=1 |

K状态(t3时刻,Bin=1),Bout=0 |

||||

|

t3t2t1t0 |

T3T2T1T0 | 下一个状态:A | t3t2t1t0 | T3T2T1T0 | 下一个状态:A |

| 0110 | 1001 | 1110 | (1)0001 | ||

未完待续。。。

8421BCD转余3码Verilog HDL的设计(1)的更多相关文章

- 基于Verilog HDL 的数字电压表设计

本次实验是在“基于Verilog HDL的ADC0809CCN数据采样”实验上进一步改进,利用ADC0809采集到的8位数据,进行BCD编码,以供查表方式相加进行显示,本次实验用三位数码管. ADC0 ...

- 浅谈Verilog HDL代码编写风格

消失了好久,没有写文章,也没有做笔记,因为最近再赶一个比赛,时间很紧,昨天周六终于结束了,所以趁着周末这会儿有时间,写点东西,记录下来.首先我学习FPGA才一年多,我知道自己没有资格谈论一些比较深层次 ...

- 如何高效的编写Verilog HDL——进阶版

博主之前写过一篇文章来谈论如何高效的编写Verlog HDL——菜鸟版,在其中主要强调了使用Notepad++来编写Verilog HDL语言的便捷性,为什么说是菜鸟版呢,因为对于新手来说,在还没有熟 ...

- 你知道Verilog HDL程序是如何构成的吗

本节通过硬件描述语言Verilog HDL对二十进制编码器的描述,介绍Verilog HDL程序的基本结构及特点. 二十进制编码器及Verilog HDL描述 二十进制编码器是数字电路中常用的电路单元 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 关于初次使用Verilog HDL语言需要懂的基本语法

关于初次使用Verilog HDL语言需要懂的基本语法 1.常量 数字表达式全面的描述方式为:<位宽><进制><数字> 8’b10101100,表示位宽为8的二进制 ...

- FPGA Verilog HDL 系列实例--------步进电机驱动控制

[连载] FPGA Verilog HDL 系列实例 Verilog HDL 之 步进电机驱动控制 步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心.那么,下面我 ...

- Verilog HDL基础语法讲解之模块代码基本结构

Verilog HDL基础语法讲解之模块代码基本结构 本章主要讲解Verilog基础语法的内容,文章以一个最简单的例子"二选一多路器"来引入一个最简单的Verilog设计文件的 ...

- Verilog HDL模块的结构

一个设计是由一个个模块(module)构成的.一个模块的设计如下: 1.模块内容是嵌在module 和endmodule两个语句之间.每个模块实现特定的功能,模块可进行层次的嵌套,因此可以将大型的数字 ...

随机推荐

- 华为鸿蒙系统pk安卓系统

Harmony OS Vs Android Comparison It isn’t based on Linux kernel The key difference between HarmonyOS ...

- html5 一些好用的原生事件

计算机技术发展这么多年, 有些方面太老了,不适合新时代的发展, 使用新的规范,更方便开发和使用, 提高各方使用人的工作效率, 何乐而不为 drag drop html5新增属性 某些操作使用拖拽比较方 ...

- 吴裕雄--天生自然C语言开发:数组

] = {1000.0, 2.0, 3.4, 7.0, 50.0}; ]; #include <stdio.h> int main () { ]; /* n 是一个包含 10 个整数的数组 ...

- 一:MYsql登录,服务开启和停止

字段的属性: 1:名称 2:数据类型 3:长度 4:约束 SQL的分类:(结构化查询语言) 1:数据查询语言DQL select 2:数据操纵语言DML insert delete u ...

- C#结构体的使用

C#结构体的使用 结构体:相当于是我们自己定义的一种复杂的类型. 常见简单类型:int... double float bool char string 常见复杂类型:DateTime 数组类型 生活 ...

- 系统学习javaweb1----HTML语言1

自我感受:HTML语言没想到也有这么大的学问,竟然能通过超链接标签直接访问百度,这可让我大吃一惊,我也得反思一下自己,上学期的java纯是混过来的,没有系统的学习过,感觉能通过期末考试都是侥幸,接下来 ...

- Java 的 LinkedList 的底层数据结构

1. 数据结构--LinkedList源码摘要 public class LinkedList<E> extends AbstractSequentialList<E> imp ...

- take office|boast|think twice|dispose of|level|stuff|'s mature for|a green hand|'s a slave to|

One reporter wrote that Dewey was acting like a man who had already been elected and was only passin ...

- 用磁盘工具刻录MACOSX系统启动盘方法

些系统盘用Toast 刻录后无法引导,建议使用磁盘工具刻录系统盘 老手可能早知道这了,仅供新手参考 在应用程序-->实用工具里找到磁盘工具,打开. 将DMG文件拖放到磁盘工具窗口,双击DMG文件 ...

- Pycharm 2019 破解激活方法

转载:https://blog.csdn.net/guofang110/article/details/87793264 使用破解补丁方法虽然麻烦,但是可用激活到2099年,基本上是永久激活了,毕竟在 ...