Artix-7 50T FPGA试用笔记之Create a simple MicroBlaze System

前言:之前笔者的试用博文提到安富利这块板子非常适合MicroBlaze开发,同时网上关于MicroBlaze的资料非常少(或含糊不清),没有一篇能完整介绍VIVADO SDK的设计流程,所以笔者带来这篇博文以供参考。

实验平台:Avnet-Artix-7 50T 开发套件/其它硬件也可以

EDK:Vivado 2015.2

SDK:Xilinx SDK 2015.2

实验内容:创建一个简单的MicroBlaze,实现板上LED流水灯和串口功能。

实验步骤:

(一) EDK部分

1. VIVADO下创建一个空工程。

2. IP Integrater -> Create Block Design

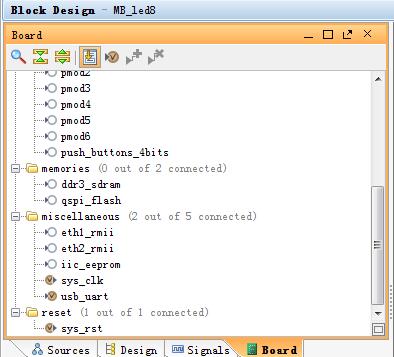

3. 框图内添加IP,such as MicroBlaze IP。使用Avnet-Artix-7 50T 开发套件双击Board

中器件即可。非该套件使用者,需要右击Diagram->ADD IP ->AXI Uartlite |AXI GPIO。需要双击IP设置对应波特率和GPIO_LED的位数。

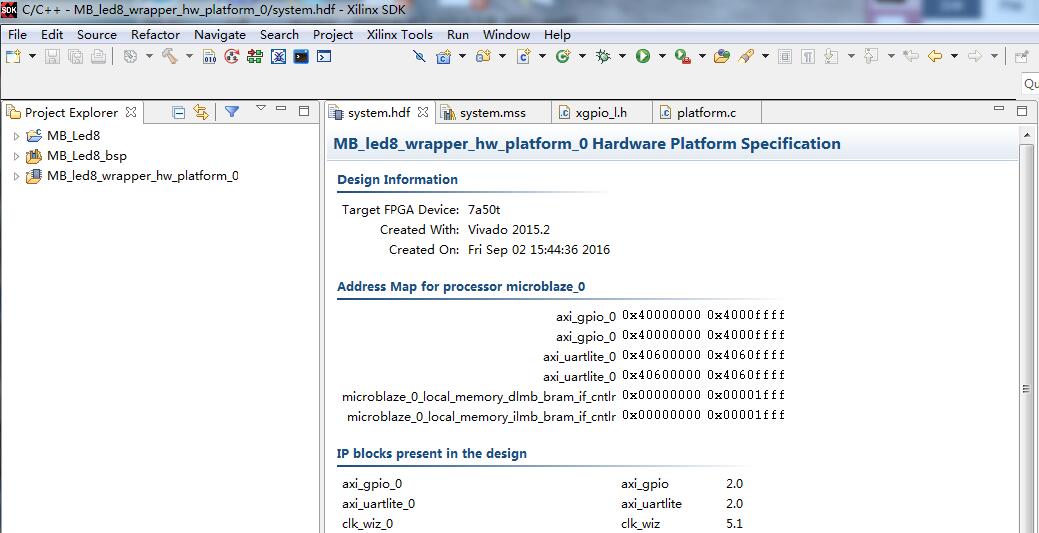

4. 点击 Run Block Automation

5. 点击 Run Connection Automation

——将剩下的线连上,时钟都接100MHz,非开发板用户功能都设置为custom。

注意:rst复位信号,Active High or Low根据自己开发板来定。

最终的Diagram如下图所示:

6. 点击VIVADO工具栏 Validate Design按钮(或按F6),编译设计时候正确。

7. 右击Design Sources栏中 .bd文件,Generate Output Product。

8. Creator HDL wrapper。//Let Vivado auto……

9. Synthesis -> Implementation -> Generate Bitsteam

10. File -> Export Hardware //include bitstream 勾打上,location 随意。

至此,FPGA软核系统包括所需外设电路驱动都搭好了,EDK部分至此结束。

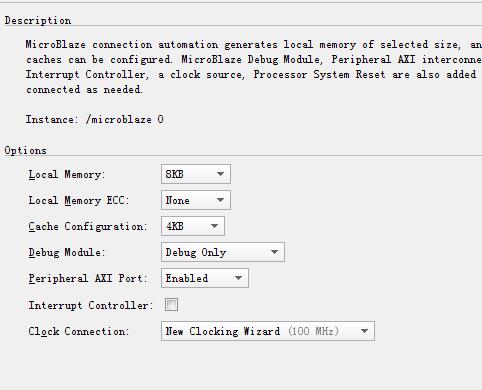

(二) SDK部分

1. File -> Launch SDK。

SDK界面如上图所示,这是笔者SDK Application建立好之后界面,不过也差不多。

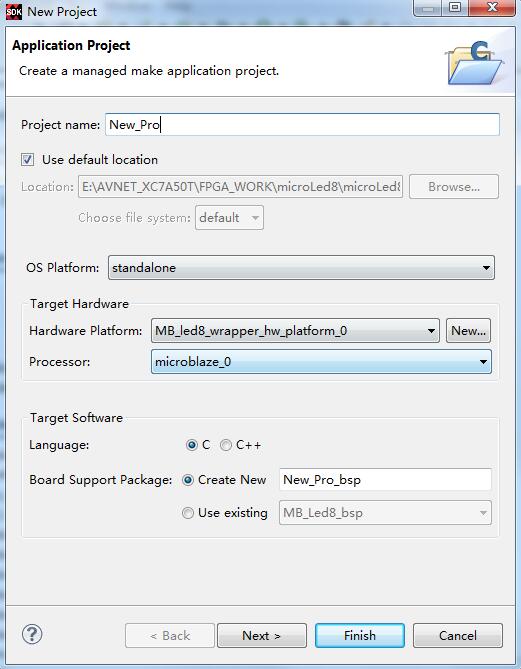

2. File -> New

Project Name 随意起个,点击next,选择Hello World模板,Finish。

这里模板已经写好了串口的初始化和打印部分,我们在添加上流水灯部分就OK了。

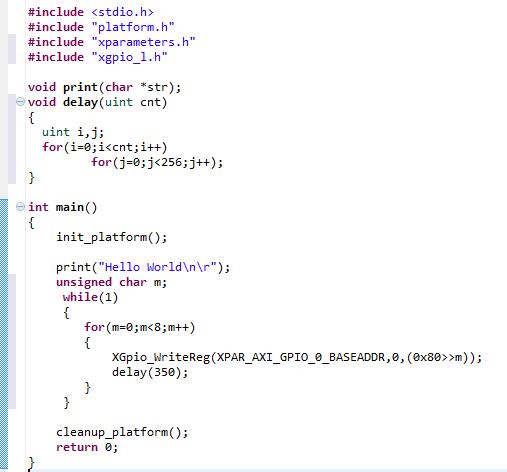

完整程序如上图所示,需要添加两个头文件,分别包含了外设器件的地址和操作GPIO的库函数。有Keil或其他编程经验的都可以看懂。

3. 工具栏 Xilinx Tools –> Program FPGA

4. 右击 左侧New_Pro选择RUN As -> 1….. //笔者这里选择的是第一个

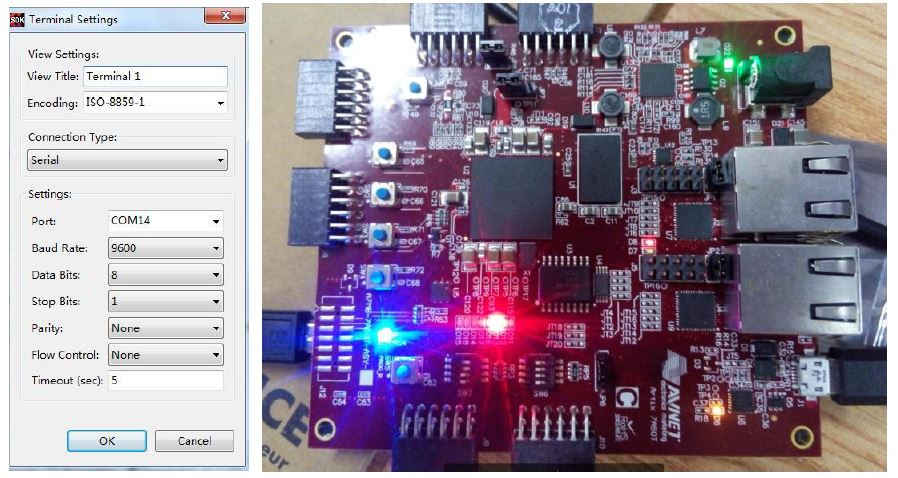

实验结果如下图所示: //注意的是串口的设置不要错

总结:本文实现的功能是很简单的,主要是让大家体会MicroBlaze设计的流程。笔者没有介绍每一步的详细过程,旨在提供一个框架的搭建流程。

转载:http://www.openhw.org/module/forum/thread-644629-1-1.html

Artix-7 50T FPGA试用笔记之Create a simple MicroBlaze System的更多相关文章

- kbmMW 5.07.00试用笔记

在kbmMW 5.06.20试用笔记中遇到的问题,在这个版本中,基本都解决了.但还是发现修正后存在的小问题及新问题: 1.Resolve返回值错误 当提交的ClientQuery是执行一条sql语句, ...

- kbmMW 5.06.20试用笔记

1.kbmMWConfiguration自动备份配置文件的问题还没有修正. 下面是以前写过的内容,再一次在新闻组中提出这个问题: kbmMW提供一个强大的配置信息管理对象,前期译过这个对象的介绍,在使 ...

- CentOS 7 mini 试用笔记

CentOS 7 mini 试用笔记 安装过程中,网卡是默认关闭的,要手动打开. 安装好以后,查看IP地址:# ip addr----------------------1: lo: 本地回环2: e ...

- Create a simple REST web service with Python--转载

今日尝试用python建立一个restful服务. 原文地址:http://www.dreamsyssoft.com/python-scripting-tutorial/create-simple-r ...

- CREATE FILE encountered operating system error 5(Access is denied.)

这篇博文主要演示"CREATE FILE encountered operating system error 5(Access is denied.)"错误如出现的原因(当然只是 ...

- FPGA Timing笔记

很多FPGA工程师都会遇到timing的问题,如何让FPGA跑到更快的处理频率是永久话题.决定FPGA的timing关键是什么?如何才能跑到更快的频率呢? A. 第一步需要了解FPGA的timing路 ...

- Xilinx FPGA 学习笔记

一.时序设计 方法1.通过状态机来实现,通过verilog控制FPGA,让它该快的时候快,该慢的时候慢. 方法2.FPGA中运行CPU 把逻辑控制顺序复杂的事情用C代码来实现,而实时处理部分用veri ...

- FPGA学习笔记(六)—— 时序逻辑电路设计

用always@(posedge clk)描述 时序逻辑电路的基础——计数器(在每个时钟的上升沿递增1) 例1.四位计数器(同步使能.异步复位) // Module Name: coun ...

- uniGUI试用笔记(十三)调用WebService

今天尝试用uniGUI做Web服务器,调用应用服务器的WebService,遇到些问题记录下来备忘. 1.对WebService的调用同一般App程序,只是注意如果WebService的执行时间较长, ...

随机推荐

- python采用pika库使用rabbitmq总结,多篇笔记和示例(转)

add by zhj:作者的几篇文章参考了Rabbitmq的Tutorials中的几篇文章. 原文:http://www.01happy.com/python-pika-rabbitmq-summar ...

- go-004-数据结构

在 Go 编程语言中,数据类型用于声明函数和变量. 数据类型的出现是为了把数据分成所需内存大小不同的数据,编程的时候需要用大数据的时候才需要申请大内存,就可以充分利用内存. Go 语言按类别有以下几种 ...

- spring 返回xml数据

要将对象以xml数据形式返回:参考:https://blog.csdn.net/Pnoter/article/details/52218363 1:创建对象时应该填上xml注解,这样才能将对象转换为x ...

- python 2.7中文字符串的匹配(参考)

#!/bin/env python #-*- coding:utf-8 -*- import urllib import os,sys,json import ssl context = ssl._c ...

- SpringData_JpaRepository接口

该接口提供了JPA的相关功能 List<T> findAll(); //查找所有实体 List<T> findAll(Sort sort); //排序.查找所有实体 List& ...

- swoole gets

控制器调用: function gets() { $model = Model('ap_pic'); $model->select = ' id, size_type '; $gets['pag ...

- 在Mybatis中使用连表查询的一次实际应用

以前在工作中很少使用多表关联查询,对连表查询的具体作用和使用场景也没有很直观的认识,通过这次在项目中的实际应用,对此有了一定的认识,特记录如下. 关联表介绍: 分别是属性表attr_info.属性值表 ...

- SQL substring()函数

①substring()函数是个截取函数,不同的数据库语法有区别 MySQL: SUBSTR( ), SUBSTRING( ) Oracle: SUBSTR( ) SQL Server: SUBSTR ...

- FCKeditor配置与使用

fckeditor - (1)资料介绍与安装 fckeditor介绍 FCKeditor是一个专门使用在网页上属于开放源代码的所见即所得文字编辑器. 1.fckeditor官网:http://ww ...

- 分布式session的管理

在分布式架构或微服务架构下,必须保证一个应用服务器上保存Session后,其它应用服务器可以同步或共享这个Session,可能会出现在A1系统登录后创建并保存Session,再次发起请求,请求被转发到 ...