verilog实现毫秒计时器

verilog实现毫秒计时器

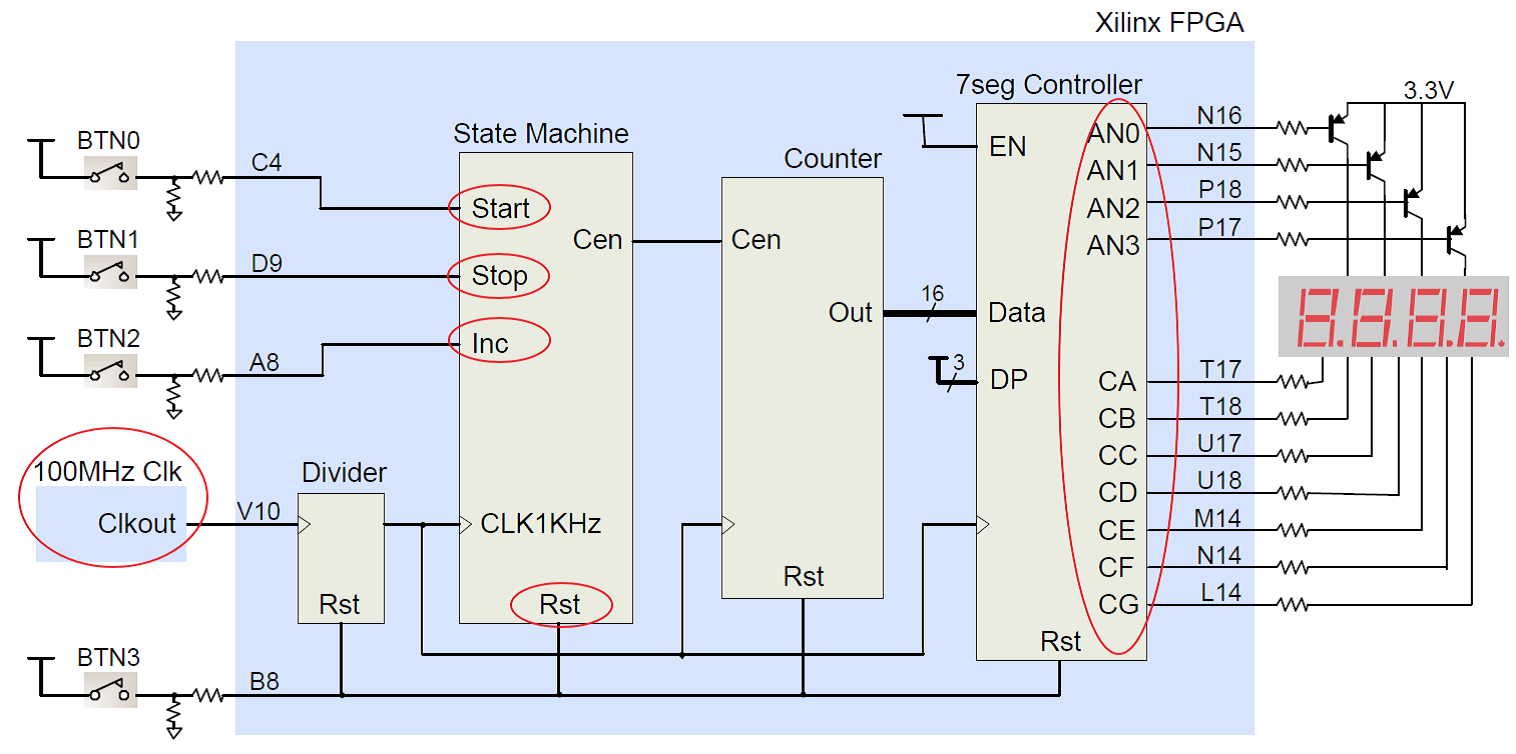

整体电路图

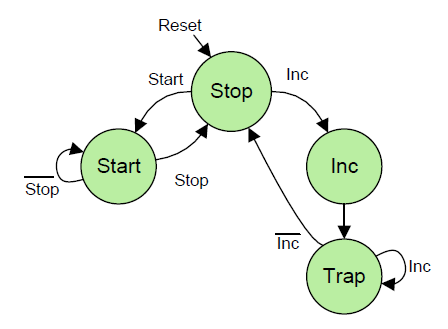

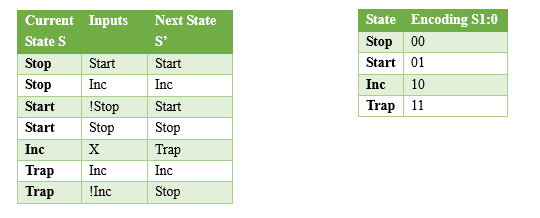

实验状态图

Stop代表没有计时,Start代表开始计时,Inc代表计时器加1,Trap代表inc按钮按下去时候的消抖状态。

状态编码表

实验设计思路

- 时钟分频:用一个diver=49999来让count从0根据100MHz的内部时钟变化到diver让myclk取反一次,以达到myclk的频率为1KHz的时钟。

- 计时器:以myclk来触发,从小数点后第三位开始计数,每次+1,用往前面进位的方法,从而不需要分成四个自定义时钟。

- 显示器:定义好七段译码器的数字显示,然后每次挑选一位数字,分频每次显示一位,小数点同最高位同时显示消失。分频足够低的时候,肉眼的视觉暂留效果,看起来就是同时显示。

- 亮点:代码全程用模块实现,简单易读易维护。

完整代码

//counter.v

`timescale 1ns / 1ps

module counter(

input myclk,

input reset,

input cen,

output [15:0] number

);

wire up0, up1, up2;

counter4bit c1(

.myclk(myclk),

.reset(reset),

.cen(cen),

.four(number[3:0]),

.up(up0)

);

counter4bit c2(

.myclk(myclk),

.reset(reset),

.cen(cen & up0),

.four(number[7:4]),

.up(up1)

);

counter4bit c3(

.myclk(myclk),

.reset(reset),

.cen(cen & up0 & up1),

.four(number[11:8]),

.up(up2)

);

counter4bit c4(

.myclk(myclk),

.reset(reset),

.cen(cen & up0 & up1 & up2),

.four(number[15:12]),

.up()

);

endmodule

//clk_div.v

`timescale 1ns / 1ps

module clk_div(

input clk_in,

input reset,

output reg clk_out

);

parameter diver = 49999;//for FPGA

//parameter diver = 4;//for test

reg [15:0] count;//just for 49999 or warning

always@(posedge clk_in or posedge reset)

begin

if(reset)

begin

count <= 0;

clk_out <= 1'b0;

end

else if(count == diver)

begin

clk_out <= ~clk_out;

count <= 0;

end

else

begin

count <= count + 1'b1;

end

end

endmodule

//MillisecondCounter.v

`timescale 1ns / 1ps

module MillisecondCounter(

input start,

input stop,

input inc,

input clk,

input reset,

output [3:0] en,

output [6:0] light,

output dot

);

wire myclk;

wire cen;

wire [15:0] number;

clk_div d(

.clk_in(clk),

.reset(reset),

.clk_out(myclk)

);

state_transform st(

.start(start),

.stop(stop),

.inc(inc),

.myclk(myclk),

.reset(reset),

.cen(cen)

);

counter ct(

.myclk(myclk),

.reset(reset),

.cen(cen),

.number(number[15:0])

);

show_number sn(

.myclk(myclk),

.reset(reset),

.number(number[15:0]),

.en(en[3:0]),

.light(light[6:0]),

.dot(dot)

);

endmodule

//counter4bit.v

`timescale 1ns / 1ps

module counter4bit(

input myclk,

input reset,

input cen,

output reg [3:0] four,

output up

);

assign up = (four == 4'b1001) ? 1'b1 : 1'b0;

always@(posedge myclk or posedge reset)

begin

if(reset)

four <= 0;

else if(cen)

begin

if(four == 4'b1001)

four <= 0;

else

four <= four + 1'b1;

end

end

endmodule

//state_transform.v

`timescale 1ns / 1ps

module state_transform(

input start,

input stop,

input inc,

input myclk,

input reset,

output reg cen

);

parameter STOP = 2'b00, START = 2'B01, INC = 2'b10, TRAP = 2'b11;

reg [1:0] state, nextstate;

always@(posedge myclk or posedge reset)

begin

if(reset)

state <= STOP;

else

state <= nextstate;

end

always@(*)

begin

case(state)

STOP:

if(stop) nextstate <= STOP;

else if(start) nextstate <= START;

else if(inc) nextstate <= INC;

else nextstate <= STOP;

START:

if(start) nextstate <= START;

else if(stop) nextstate <= STOP;

else nextstate <= START;

INC:

nextstate <= TRAP;

TRAP:

if(inc) nextstate <= TRAP;

else nextstate <= STOP;

default:

nextstate <= STOP;

endcase

end

always@(*)

begin

case(state)

STOP: cen <= 1'b0;

START: cen <= 1'b1;

INC: cen <= 1'b1;

TRAP: cen <= 1'b0;

default: cen <= 1'b0;

endcase

end

endmodule

//show_number.v

`timescale 1ns / 1ps

module show_number(

input myclk,

input reset,

input [15:0] number,

output reg [3:0] en,

output reg [6:0] light,

output dot

);

reg [1:0] index;

reg [3:0] num_index;

assign dot = (index == 2'b11) ? 1'b0 : 1'b1;

always@(posedge myclk or posedge reset)

begin

if(reset)

index <= 0;

else

index <= index + 1'b1;

end

always@(*)

begin

case(index)

2'b00: en <= 4'b1110;

2'b01: en <= 4'b1101;

2'b10: en <= 4'b1011;

2'b11: en <= 4'b0111;

default: en <= 4'b1111;

endcase

end

always@(*)

begin

case(index)

2'b00: num_index <= number[3:0];

2'b01: num_index <= number[7:4];

2'b10: num_index <= number[11:8];

2'b11: num_index <= number[15:12];

default: num_index <= 4'b0000;

endcase

end

always@(*)

begin

case(num_index)

4'b0000: light <= 7'b0000001;

4'b0001: light <= 7'b1001111;

4'b0010: light <= 7'b0010010;

4'b0011: light <= 7'b0000110;

4'b0100: light <= 7'b1001100;

4'b0101: light <= 7'b0100100;

4'b0110: light <= 7'b0100000;

4'b0111: light <= 7'b0001111;

4'b1000: light <= 7'b0000000;

4'b1001: light <= 7'b0000100;

default: light <= 7'b1111111;

endcase

end

endmodule

仿真测试文件

//VTF_Millisecond.v

`timescale 1ns / 1ps

module VTF_Millisecond;

// Inputs

reg start;

reg stop;

reg inc;

reg clk;

reg reset;

// Outputs

wire [3:0] en;

wire [6:0] light;

wire dot;

// Instantiate the Unit Under Test (UUT)

MillisecondCounter uut (

.start(start),

.stop(stop),

.inc(inc),

.clk(clk),

.reset(reset),

.en(en),

.light(light),

.dot(dot)

);

initial begin

// Initialize Inputs

start = 0;

stop = 0;

inc = 0;

clk = 0;

reset = 1;

// Wait 100 ns for global reset to finish

#100;

reset = 0;

// Add stimulus here

start = 1;

#1200;

start = 0;

stop = 1;

#200;

inc = 1;

#200;

stop = 1;

#200;

start = 1;

#200;

inc = 0;

#200;

reset = 1;

#200;

reset = 0;

end

always #2 clk = ~clk;

endmodule

verilog实现毫秒计时器的更多相关文章

- [FPGA]Verilog 60s秒表计时器(最大可计时间长达9min)

[FPGA]Verilog 60s秒表计时器 1.引述 这次的实验来自于本人本科课程数电结课时的自选题目.由于这次上传是后知后觉,学校已将小脚丫板子回收,所以在这篇文章中没法贴出代码结果的效果图了,但 ...

- js实现时分秒毫秒计时器

<!DOCTYPE html> <html lang="en"> <head> <meta charset="UTF-8&quo ...

- [FPGA]Verilog实现可自定义的倒计时器(24秒为例)

目录 想说的话... 样例_边沿检测计数器 代码讲解 仿真演示 拓展_自定义倒计时数和倒计时间隔 代码讲解 仿真演示 总结 实例_24秒倒计时器 想说的话... 本次实现的是一个24秒倒计时器,功能顾 ...

- Android线程计时器实现

cocos2dx的计时器很好用,但当app进入后台,其计时器会pause掉,如果想要一个稳恒计时器就得自己去实现完成了,在Cocos2d-x for ios中我们可以利用NSTimer类并结合objc ...

- LabVIEW串口通信

Instrument I/O 利用LabVIEW内置的驱动程序库和具有工业标准的设备驱动软件,可对 GPIB(通用接口总线).Ethernet(以太网)接口.RS-232(标准串行接口总线)/RS-4 ...

- Labview中定时函数之间的区别

第一个定时函数(时间延迟):在VI中插入时间延迟,指定在运行调用VI之前延时的秒数.默认值为1.000. 第一个定时函数(等待(ms)):等待指定长度的毫秒数,并返回毫秒计时器的值.该函数进行异步系统 ...

- 微信小程序倒计时组件开发

今天给大家带来微信小程序倒计时组件具体开发步骤: 先来看下最终效果: git源:http://git.oschina.net/dotton/CountDown 分步骤-性子急的朋友,可以直接看最后那段 ...

- 【system.date】使用说明

对象:system.date 说明:提供一系列针对日期类型的操作 目录: 方法 返回 说明 system.date.isDate( date_string ) [True | False] 判断 ...

- 浅谈labviEW定时器

Labview提供了五种定时器:普通定时器3种: Tick Count (ms). Wait(ms).Wait Until Next ms Multipule(等待下一个毫秒的整数倍) API函数定 ...

随机推荐

- js遇到的问题

一些开发前台时遇到的小问题: ----------------------------------------- 一眼看出页面使用html还是html5: html有三种声明方式:<!DOCTY ...

- CSS垂直翻转/水平翻转提高web页面资源重用性——张鑫旭

一.CSS下兼容性的元素水平/垂直翻转实现 随着现代浏览器对CSS3的支持愈发完善,对于实现各个浏览器兼容的元素的水平翻转或是垂直翻转效果也就成为了可能.相关的CSS代码如下: /*水平翻转*/ .f ...

- 【代码笔记】iOS-单击手势的添加

一,效果图. 二,工程图. 三,代码. RootViewController.h #import <UIKit/UIKit.h> @interface RootViewController ...

- 解决ie6、ie7下float为right换行的情况

IE6下有不少奇怪的Bug,今天就碰到一个,float:right换行bug,情况是并列的几个块级元素如div和span,一些设置了左浮动一些设置右浮动,一行的宽度足够放下所有的块级元素,但此时ie6 ...

- 【Python】Java程序员学习Python(十一)— IO

一.前言 io的内容其实还是有很多的,现在我也只是了解初步用法,当然详细内容还是应该参照官方api的: 官方api:https://docs.python.org/3/library/os.html. ...

- webpack的require是如何工作的?

https://stackoverflow.com/questions/35625593/how-does-webpacks-require-work wepback的require函数调用类似于no ...

- d3js layout 深入理解

D3 layouts help you create more advanced visualisations such as treemaps: D3 layouts帮助您创造更加高级复杂的可视化图 ...

- 【转】数据分析与处理之二(Leveldb 实现原理)

郑重声明:本篇博客是自己学习 Leveldb 实现原理时参考了郎格科技系列博客整理的,原文地址:http://www.samecity.com/blog/Index.asp?SortID=12,只是为 ...

- python入门の缩进魔术

idx=1 sum=0 while idx<=100: sum=idx+sum idx=idx+1 print('sum 100 =', sum) ======================= ...

- MySQL慢日志简介及Anemometer工具介绍

作者:王航威 - fordba.com 来源:http://fordba.com/box-anemometer-visual-mysql-slow.html,叶师傅对原文内容略有调整 备注:王航威是知 ...