计算机组成原理 — CPU 中央处理器

目录

文章目录

前文列表

《计算机组成原理 — 冯诺依曼体系结构》

《计算机组成的基本硬件设备》

逻辑电路部件

组合逻辑电路

- 三态电路

- 异或门

- 加法器

- 译码器

- 数据选择器

时序逻辑电路

- 触发器

- 寄存器和移位寄存器

- 计数器

阵列逻辑电路

阵列 指的是逻辑元件在硅芯片上以阵列的形式排列。

- 只读存储器(ROM)

- 可编程序逻辑阵列(PLA)

- 可编程序阵列逻辑(PAL)

- 通用阵列逻辑(GAL)

- 门阵列(GA)、宏单元阵列(MCA)、标准单元阵列(SCA)

- 现场可编程序门阵列(FPGA)

中央处理器(CPU)

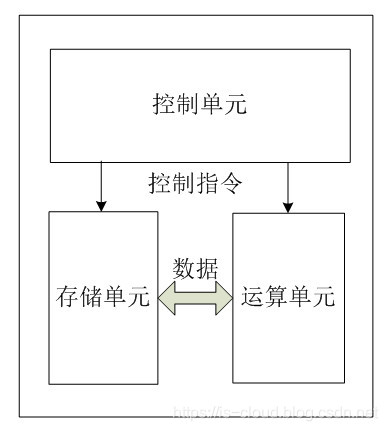

微处理器的出现得益于集成电路的发展,将控制器和运算器集成在一个芯片上,称为中央处理器(CPU)。CPU 从逻辑上可以分为 3 个模块:控制单元、运算单元和存储单元,这三部分由 CPU 的片内总线连接起来。

注:片内总线,指计算机各芯片内部传送信息的通道。

控制单元(控制器)

控制单元是 CPU 的指挥控制中心,主要由 PC 程序计数器、指令寄存器 IR(Instruction Register)、指令译码器 ID(Instruction Decoder)和操作控制器 OC(Operation Controller)组成。控制单元工作时,PC 根据程序依次从存储器中取出一条条指令并暂存在 IR 中,通过 ID 分析指令的内容,以确定应该进行什么操作,然后通过 OC 按照确定的时序,向相应的部件发出微操作控制信号。OC 中主要包括节拍脉冲发生器、控制矩阵、时钟脉冲发生器、复位电路和启停电路等控制逻辑。

PC 程序计数器:又叫 PC 寄存器(Program Counter Register),本质是指令地址寄存器(Instruction Address Register)。存放当前正在执行的指令的地址或即将要执行的下一条指令的地址。有两种方式形成指令地址:一是顺序执行通过程序计数器 +1 得到下一条指令的地址;二是跳跃执行通过跳转类指令得到下一条指令的地址。

IR 指令寄存器(Instruction Register):区别于指令地址寄存器,是存放当前正在执行的指令。以便在指令执行的过程中控制完成一条指令的全部功能。

ID 指令译码器:对指令的操作码(OPCODE)进行解析,并产生相应的控制型号。

脉冲源及启停线路:脉冲源产生一定频率的脉冲作为 CPU 的时钟脉冲,是 CPU 工作周期的基准信号。而启停线路则保证了可靠地送出或封锁完整的时钟脉冲。

时序控制信号形成部件:在 CLK 时钟的作用下,根据当前正在执行的指令的需要,产生对应的时间控制信号,并根据被控功能部件的反馈信号调整时序控制信号。

运算单元(运算器)

运算单元是可以执行算术运算(e.g. 加减乘除)和逻辑运算(e.g. 与或非、位移、比较)。运算单元所进行的全部操作都由控制单元发出的控制信号指挥,运算单元是单纯的执行部件。

定点运算部件:由逻辑运算部件(ALU)、若干个寄存器、移位电路、计数器和门电路组成。其中 ALU 主要完成加减法算术运算及逻辑运算。

浮点运算部件:由阶码运算部件和尾数运算部件组成。阶码部分仅执行加减法运算,尾数部分则可执行加减乘除运算。

存储单元(寄存器组和片内缓存)

存储单元是 CPU 暂存数据的地方,保存着等待处理的数据,或是已经处理过的数据。CPU 访问寄存器的速度比访问主存储器的速度更快,采用寄存器,可以减少 CPU 访问内存的次数,从而提高工作速度。但因为受到芯片面积和集成度的限制,寄存器组的容量不会很大。寄存器组可分为专用寄存器和通用寄存器。专用寄存器的作用是固定的,寄存相应的数据。而通用寄存器的用途则更加广泛,并可由程序员规定其用途。

寄存器由多个触发器(Flip-Flop)或锁存器(Latches)组成的简单电路,触发器和锁存器是两种原理不同的数字电路组成的逻辑门,属于数字电路领域。N 个触发器或锁存器就可以组成一个 N Bit 的寄存器,能够保存 N 为数据。我们常说的 64 位 Intel CPU,其寄存器就是 64 位的,所以其最大的直接寻址空间就为 264 bit。需要注意的是,并不是说寄存器是 64 位的,那么该 CPU 只支持使用 264 bit 的存储器空间,因为 CPU 除了支持直接寻址方式之外,还支持基址寄存器寻址方式,实现了基于内存分页的地址寻址方式,寻址空间得到了巨大的提升。

CPU 的工作原理

控制单元在时序脉冲的作用下,从程序入口将第一条指令的地址写入 PC 程序计数器(本质是寄存器),控制单元将 PC 程序计数器的指令地址送到地址总线上,CPU 就将这个地址指向的指令读到 IR 指令寄存器,再通过 ID 指令译码器进行译码,了解指令的操作内容和操作数。对于执行指令过程中所需要用到的操作数,会将操作数的地址码也送到地址总线上,CPU 就将这个地址指向的数据读取到寄存器组中暂存起来,最后 OC 操作控制器发出控制型号到运算单元,由运算单元完成对数据的加工处理。然后 PC 程序计数器自增,周而复始,一条一条指令执行下去,直到停电为止。

将过程简化为下述步骤:

- 取指令

- 分析指令

- 执行指令

- 修改指令计数器

上述步骤的执行期间还可能会穿插着:

- 控制程序和数据的输入与结果输出:根据程序的内容或人工干预,控制单元在适当的时候向输入/输出设备发出相应的指令来完成 I/O 功能。

- 对异常情况和某些请求的处理:在特定的时刻(异常中断、输入/输出中断),由相应的部件或设备向 CPU 发出中断请求信号或 DMA 请求信号。

- 中断请求信号:待 CPU 执行完当前指令后,响应该中断请求,中止当前执行的程序,转而执行中断程序。待中断程序执行完后,再回到原程序继续执行下去。

- DMA 请求信号:待 CPU 完成当前机器周期的操作后,暂停工作,让出总线给 I/O 设备。待完成 I/O 设备和存储器之间的数据传输之后,CPU 从暂时中止的机器周期开始继续执行原程序的指令。

时钟周期、机器周期、指令周期和总线周期

时钟脉冲:指脉冲信号,是一个由 CPU 控制单元按一定电压幅度、一定时间间隔连续发出的电子脉冲信号,是计算机的基本工作脉冲,控制着计算机的工作节奏。时钟频率越高,时钟周期就越短,工作速度也就越快。

时钟频率(Clock Speed):指同步电路中时钟脉冲的基础频率,是单位时间(1s)内所产生的时钟脉冲的个数。时钟频率是描述周期性循环信号在单位时间内所出现的次数,标准计量单位是 Hz(赫兹)。

CPU 主频:即 CPU 内部工作的时钟频率,是评定 CPU 性能的重要指标,一般来说主频数值越大越好。需要注意的是,主频仅是 CPU 性能表现的一个方面,而不代表 CPU 的整体性能,CPU 的运算速度还考虑流水线的各方面的性能指标(缓存、指令集、CPU 的位数等)。

外频:是 CPU 外部的工作频率,是由主板提供的基准时钟频率。CPU 主频和外频的关系:主频=外频×倍频。

FSB 频:是连接 CPU 和主板芯片组中的北桥芯片的前端总线(Front Side Bus)上的数据传输频率。

时钟周期:也称为振荡周期、P 周期或节拍脉冲,定义为时钟频率的倒数,即 (1/时钟频率)s,比如:8086/8088 系统的时钟频率为 4.77MHz,那么每个时钟周期约为 200ns。时钟周期在 CPU 的描述里也叫节拍,是 CPU 中最基本的、最小的时间单位,在一个时钟周期内,CPU 仅完成一个最基本的动作。时钟周期表示了 S/DRAM 所能运行的最高频率,更小的时钟周期就意味着更高的工作频率。

状态周期:也称为 S 周期,把时钟脉冲的周期定义为节拍(用 P 表示)。时钟脉冲经过二分频后定义为状态,即一个状态包含两个节拍,称为状态周期(用 S 表示)。

机器周期:在计算机中,为了便于管理,常把一条指令的执行过程划分为若干个阶段,每一阶段完成一项工作。例如:取指令、分析指令、执行指令、存储器读、存储器写等,此类每项工作称为一个基本操作。完成一个基本操作所需要的时间称为机器周期。一般情况下,一个机器周期由若干个状态周期组成。机器周期一般由 12 个时钟周期组成,也是由 6 个状态周期组成。

指令周期:指令周期是取出一条指令并执行这条指令的时间。一般由若干个机器周期组成,是从取指令、分析指令到执行完所需的全部时间。指令周期类型有非访内指令的指令周期、取数指令的指令周期、存数指令的指令周期、空操作指令和转移指令的指令周期。

注:图源自 https://blog.csdn.net/u012076669/article/details/84452264

总线周期:指 CPU 完成一次访问主存储器或 I/O 端口所需要的时间,一个总线周期由几个时钟周期组成。由于主存储器和 I/O 端口是挂接在总线上的,CPU 对主存储器和 I/O 接口的访问,是通过总线实现的。通常把CPU通过总线对微处理器外部(存储器或I/O接口)进行一次访问所需时间称为一个总线周期。

CPU 流水线

我们知道 CPU 执行一条指令时可以分为取指令、分析指令、执行指令、存结果等若干个步骤,不同的步骤可能由 CPU 内部的不同部件(指令部件、执行部件)来完成。在这样的前提下,如果 CPU 单纯的顺序执行这些步骤的话,势必会在某一时刻令一些部件空闲。可想而知,如果 CPU 控制单元调度恰当,让不同部件可以并行工作的话,是可以提高各个部件的工作效率和计算机运算速度的,这就是流水线调度方式。

CPU 流水线(Pipeline),亦称管线,是现代计算机处理器中必不可少的部分,是指将计算机指令处理过程拆分为多个步骤,并通过多个硬件处理单元并行执行来加快指令执行速度。其具体执行过程类似工厂中的流水线,并因此得名。流水线主要分为 指令执行流水线 和 运算操作流水线(如:浮点加法运算)两类。

流水线的好处:

- 提高 CPU 主频:流水线将组合逻辑分割成多个小块,因为每段的关键路径变短了,所以能提高系统主频。

- 提高系统吞吐量:因为流水线让任务以类似并行方式处理,提高硬件模块的利用率,所以能提高吞吐量(Throughput)。

流水线的缺点:由于流水线让许多指令被同时执行,假如分支预测错误的话整个流水线上所有的指令全部要被取消,流水线要被重新充满,就需要从存储器或者 CPU 缓存中调用指令,导致延迟时间,在这段时间里 CPU 是没有任何工作的。NetBurst 架构管线一开始有 20 级、而后增加至 31 级,放大其缺点。其后继者 Intel Core 微处理器架构就减少管线级数。

主流 CPU 指令集架构

CISC(复杂指令集计算机)

CISC(Complex Instruction Set Computer,复杂指令集计算机)是一种计算机语言指令集,每个指令可执行若干个低级操作,诸如:存储器数据存取和计算操作,全都集于一条指令之中。复杂指令集的特点是指令数目多而复杂,每条指令的字长并不相等,计算机处理器必须加以判读,并为此付出了性能的代价。而 CISC 的好处在于其更趋近于跨越了与高级编程语言的 “语义鸿沟”,提供了更 “高端” 的指令以支持高级编程语言的语义,例如:判断、循环、函数调用、返回等高级指令。

x86 系列处理器

从 1978 年 6 月 8 日,Intel 公司发布新款 16 位微处理器 8086,开创 x86 架构时代算起,Intel x86(The X86 architecture)架构已经四十多年了,是世界上设计、生产、制造最多的 CPU 体系之一。Intel 从 8086 开始,到 286、386、486、586、P1、P2、P3、P4、i3、i5、i7、i9 都使用了 x86 架构。所谓 x86 指的是一个 Intel 通用计算机系列的标准编号缩写,也标识一套通用的计算机语言指令集合,定义了芯片的基本使用规则。

RISC(精简指令集计算机)

RISC 是一种执行较少类型计算机指令的微处理器,起源于 80 年代的 MIPS 主机(即 RISC 机),RISC 机中采用的微处理器统称 RISC 处理器。这样一来,它能够以更快的速度执行操作(每秒执行更多百万条指令,即 MIPS)。因为计算机执行每个指令类型都需要额外的晶体管和电路元件,计算机指令集越大就会使微处理器更复杂,执行操作也会更慢。

性能特性:

- 由于指令集简化后,流水线以及常用指令均可用硬件执行;

- 采用大量的寄存器,使大部分指令操作都在寄存器之间进行,提高了处理速度;

- 采用 “缓存-主存-外存” 三级存储结构,取数与存数指令分开执行,使处理器可以完成尽可能多的工作,且不因从存储器存取信息而放慢处理速度。

ARM 系列处理器

ARM(Advanced RISC Machine,进阶精简指令集机器,更早称作:Acorn RISC Machine)架构,是一个 32 位精简指令集(RISC)处理器架构,其广泛地使用在许多嵌入式系统设计。由于节能的特点,ARM 处理器非常适用于行动通讯领域,符合其主要设计目标为低耗电的特性。

在今日,ARM 家族占了所有 32 位嵌入式处理器 75% 的比例。可以在很多消费性电子产品上看到,从可携式装置(PDA、移动电话、多媒体播放器、掌上型电子游戏,和计算机)到电脑外设(硬盘、桌上型路由器)甚至在导弹的弹载计算机等军用设施中都有 ARM 的存在。

- 优势:价格低、能耗低;

- ARM 的商业授权模式:ARM 公司本身并不靠自有的设计来制造或出售计算机处理器 ,而是将 ARM 架构授权给有兴趣的厂家。

- 生产厂商:TI (德州仪器)、Samsung(三星)、Freescale(飞思卡尔)、Marvell(马维尔)、Nvidia(英伟达)

PowerPC 系列处理器

PowerPC 是一种精简指令集(RISC)架构的中央处理器,其基本的设计源自 IBM 的 IBM PowerPC 601 微处理器 POWER(Performance Optimized With Enhanced RISC,增强 RISC 性能优化)架构。二十世纪九十年代,IBM、Apple 和 Motorola 公司成功开发出 PowerPC 芯片,并制造出基于 PowerPC 的多处理器计算机。PowerPC 架构的特点是可伸缩性好、方便灵活。

PowerPC 处理器有广泛的实现范围,包括从诸如 Power4 那样的高端服务器 CPU 到嵌入式 CPU 市场(任天堂 Gamecube 使用了 PowerPC)。PowerPC 处理器有非常强的嵌入式表现,因为它具有优异的性能、较低的能量损耗以及较低的散热量。除了象串行和以太网控制器那样的集成 I/O,该嵌入式处理器与 PC(Personal Computer)级 CPU 存在非常显著的区别。

MIPS 架构

MIPS(Microprocessor without interlocked piped stages,无内部互锁流水级的微处理器)是世界上很流行的一种 RISC 处理器,其机制是尽量利用软件办法避免流水线中的数据相关问题。它最早是在 80 年代初期由斯坦福大学 Hennessy 教授领导的研究小组研制出来的。MIPS 公司的 R 系列就是在此基础上开发的 RISC 工业产品的微处理器。这些系列产品为很多计算机公司采用构成各种工作站和计算机系统。

MIPS 技术公司是美国著名的芯片设计公司,它采用精简指令系统计算结构(RISC)来设计芯片。和英特尔采用的复杂指令系统计算结构(CISC)相比,RISC 具有设计更简单、设计周期更短等优点,并可以应用更多先进的技术,开发更快的下一代处理器。MIPS 是出现最早的商业 RISC 架构芯片之一,新的架构集成了所有原来 MIPS 指令集,并增加了许多更强大的功能。MIPS 自己只进行 CPU 的设计,之后把设计方案授权给客户,使得客户能够制造出高性能的 CPU。

Wave Computing 公司在 2018 年 12 月 17 日宣布开源 MIPS,MIPS 指令集架构(ISA)和 MIPS 的最新核心 R6 将于 2019 年第一季度公开发布。在国内,龙芯很长一段时间都在用 MIPS,直到 RISC-V 出现并得到广泛关注,今年 MIPS 也开源了,但对标 RISC-V 慢了一步。虽说,MIPS 仍有竞争力,只是如果它早几年开源的话,RISC-V 或许不会出现。

RISC-V 架构

RISC-V(读作 “RISC-FIVE”)是一个基于精简指令集(RISC)原则的开源指令集架构(ISA),V 表示为第五代 RISC。与大多数指令集相比,RISC-V 指令集可以自由地用于任何目的,允许任何人设计、制造和销售 RISC-V 芯片和软件。虽然这不是第一个开源指令集,但它具有重要意义,因为其设计使其适用于现代计算设备(如:仓库规模云计算机、高端移动电话和微小嵌入式系统)。设计者考虑到了这些用途中的性能与功率效率。该指令集还具有众多支持的软件,这解决了新指令集通常的弱点。

RISC-V 项目在 2010 年始于加州大学柏克莱分校,但许多贡献者是该大学以外的志愿者和行业工作者。RISC-V 指令集的设计考虑了小型、快速、低功耗的现实情况来实做,但并没有对特定的微架构做过度的设计。截至 2017 年 5 月,RISC-V 已经确立了版本 2.22 的用户空间的指令集(User Space ISA),而特权指令集(Privileged ISA)也处在草案版本 1.10。

计算机组成原理 — CPU 中央处理器的更多相关文章

- 【计算机组成原理】中央处理器CPU

一.CPU的功能和基本结构 1.功能 当用计算机解决某个问题是,我们首先必须为他编写程序,程序是一个指令序列,这个序列明确告诉计算机应该执行什么操作,在什么地方找到用来操作的数据,一旦把程序装入内存器 ...

- 【软测试】(两)计算机组成原理-cpu

cpu,中文名称中央处理单元,central processing unit.系统的核心,用于数据的处理,算术以及逻辑运算和控制程序的运行. 组成 运算器 从字面上就能够理解到.运算器主要用来对于逻辑 ...

- 计算机组成原理——中央处理器(CPU)考研题

(一) CPU的功能和基本结构 (二) 指令执行过程 (三) 数据通路的功能和基本结构 (四) 控制器的功能和工作原理 1. 硬布线控制器2. 微程序控制器微程序.微指 ...

- 计算机组成原理实验之CPU组成与指令周期实验

(实验五 CPU组成与指令周期实验) 课程 计算机组成原理实验 实验日期 2015 年 12 月 8 日 一.实验目的 1.将微程序控制器同执行部件(整个数据通路)联机,组成一台模型计算机. 2. ...

- 编程必备基础知识|计算机组成原理篇(09):CPU的控制器和运算器

计算机基础方面的知识,对于一些非科班出身的同学来讲,一直是他们心中的痛,而对于科班出身的同学,很多同学在工作之后,也意识到自身所学知识的不足与欠缺,想回头补补基础知识.关于计算机基础的课程很多,内容繁 ...

- 计算机组成原理--64位CPU装载32位操作系统,它的寻址能力还是4GB吗?

借由这个问题,今天我们就把 32 位 CPU.64 位 CPU.32 位操作系统.64 位操作系统之间的区别与联系彻底搞清楚.对于这个问题,博主也是一知半解了好长时间啊~ 基本概念 32位的CPU与6 ...

- day01-编程与计算机组成原理

什么是编程 编程语言:是人与计算机沟通交流的介质,通过标准化的规则传递信息 编程:就是为了使计算机能够理解人的意图,通过编程语言写出一个个文件,这堆文件完成相应的目的 编程的目的:用计算机取代人完成工 ...

- 重学计算机组成原理(五)- "旋转跳跃"的指令实现

CPU执行的也不只是一条指令,一般一个程序包含很多条指令 因为有if-else.for这样的条件和循环存在,这些指令也不会一路平直执行下去. 一个计算机程序是怎么被分解成一条条指令来执行的呢 1 CP ...

- 计算机组成原理(电脑硬件&语言分类)

计算机组成原理 一.电脑硬件配置 CPU :中央处理器(人类的大脑) -飞机 内存:存放一些临时数据(人类的短暂记忆-右脑) -高铁 硬盘:存储永久数据(左脑-长期记忆) - 汽车 输入输出:键盘鼠标 ...

随机推荐

- View相关面试问题-View绘制面试问题详解

View树的绘制流程: measure() --> layout() --> onDraw(),具体使用这个可以参考之前实现的自定义的博客:[http://www.cnblogs.co ...

- 生成静态libevent

INCLUDE C:\Program Files (x86)\Microsoft SDKs\Windows\v7.1A\Include D:\vs2013\VC\include LIB C:\Prog ...

- java WebSocket HTML页面

<!DOCTYPE html> <html lang="en"> <head> <meta charset="UTF-8&quo ...

- router-link to 动态赋值

路由定义: 动态赋值: <router-link :to="{path:'/old_data_details/params/'+item.id}" > </rou ...

- CodeForces 778B - Bitwise Formula

题意: 选择一个 m 位的二进制数字,总分为 n 个算式的答案之和.问得到最低分和最高分分别应该取哪个二进制数字 分析: 因为所有数字都是m位的,高位的权重大于低位 ,我们就从高到低考虑 ans 的每 ...

- isset和empty以及is_null区别

2.empty,isset首先都会检查变量是否存在,然后对变量值进行检测.而is_null 和 “参数本身”只是直接检查变量值,是否为null,因此如果变量未定义就会出现错误! 3.isset():仅 ...

- 《剑指offer》算法题第八天

今日题目(对应书上第39~42题): 数组中出现次数超过一半的数字 最小的k个数(top k,重点!) 数据流中的中位数 连续子数组的最大和 今天的题目都比较经典,特别是第2题. 1. 数组中出现次数 ...

- 51 Nod 1072 威佐夫游戏

https://baike.baidu.com/item/%E5%A8%81%E4%BD%90%E5%A4%AB%E5%8D%9A%E5%BC%88/19858256?fr=aladdin&f ...

- Gym 100971A Treasure Island BFS 思维题

A - Treasure Island Time Limit:2000MS Memory Limit:262144KB 64bit IO Format:%I64d & %I64 ...

- 『HGOI 20190917』Lefkaritika 题解 (DP)

题目概述 一个$n \times m$的整点集.其中$q$个点被m被设置为不能访问. 问这个点集中含有多少个不同的正方形,满足不包含任何一个不能访问的点. 对于$50\%$的数据满足$1 \leq n ...