Vivado Logic Analyzer的使用(二)

本文基于Vivado 2014.2,阅读前请参考前文http://blog.chinaaet.com/detail/37264

之前的设计都是出发后直接捕获数据。其实,与chipscope类似,可以设置捕获数据的条件。

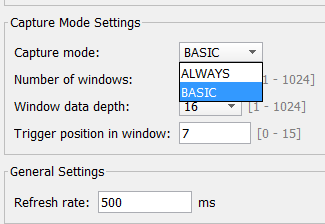

1. 将Capture mode设置为BASIC。

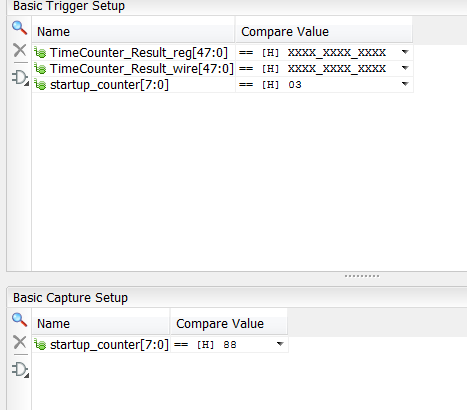

2. 在Basic Trigger Setup下面可以看到Basic Capture Setup的界面。

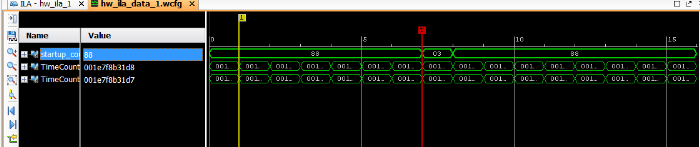

3. 从上两张图可以看到,触发信号为starup_counter,触发条件为03,捕获条件为88,触发位置为7。

4. 从捕获结果图来看,一共捕获了16个数据,触发条件处在第7个数据的位置上,该触发条件会被捕获。另外,在触发条件前后的数据,只有数据位88时才会被捕获。

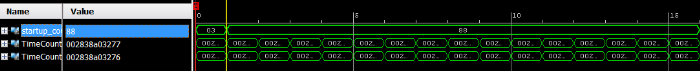

5. 将触发位置设为0后重新捕获,可以看到第一个数据是触发条件,随后的数据只有为88才会被捕获。

6. 这里,对ChipScope和Vivado Logic Analyzer的功能进行一个初步的比较。

|

ChipScope |

Vivado Logic Analyzer Basic |

|

|

多种触发值 |

支持 |

支持 |

|

触发条件组合 |

支持 |

支持 |

|

触发位置选择 |

支持 |

支持 |

|

多窗口触发 |

支持 |

支持 |

|

重复触发 |

支持 |

支持 |

|

条件捕获 |

支持 |

支持 |

|

状态机触发 |

16状态 |

不支持 |

|

计数器辅助 |

支持 |

不支持 |

|

标志位显示 |

不支持 |

不支持 |

重复触发功能在文章中没有涉及。

从该表可以看到,ChipScope的功能似乎较为强大。虽然在设置捕获信号时Vivado较为便捷(请参考http://blog.chinaaet.com/detail/37242与http://blog.chinaaet.com/detail/37239),但是在调试时似乎不如ChipScope的方便。

需要注意的是,Vivado并没有确实这些功能,而是没有提供在Basic功能中,关于Advancedd用法,会在后续博文中描述。

转载:http://blog.chinaaet.com/luozhongpin1989/p/37269

Vivado Logic Analyzer的使用(二)的更多相关文章

- Vivado Logic Analyzer的使用

chipscope中,通常有两种方法设置需要捕获的信号.1.添加cdc文件,然后在网表中寻找并添加信号2.添加ICON.ILA和VIO的IP Core 第一种方法,代码的修改量小,适当的保留设计的层级 ...

- Vivado Logic Analyzer的使用(一)

本文基于Vivado 2014.2,通过一个简单的设计来讨论Vivado Logic Analyzer的功能. 在上一篇http://blog.chinaaet.com/detail/37242中,设 ...

- Vivado Logic Analyzer的进一步探讨

本文基于Vivado 2014.2,代码基于文章http://blog.chinaaet.com/detail/37239中使用的代码. 这一篇仅讨论在综合后的Netlist中选择信号进行捕获的方法. ...

- 孕龙逻辑分析仪 ZeroPlus Logic Analyzer

Voltage Translation for Analog to Digital Interface ADC http://openschemes.com/2010/03/23/zeroplus-l ...

- spi signal analyze using logic analyzer

logic analyzer device: Saleae Logic 16 Pc software gui: capture signal picture: send command 0x55 ...

- Xilinx FGPA 上板调试 集成逻辑分析工具 Integrated Logic Analyzer(ILA) 简单配置 chipscope

Xilinx Vivado 提供了上板后的FPGA逻辑分析,信号视图显示等功能. 需要注意,上板后查看信号需要重新综合,并且需要耗费一定的片上布局布线资源. 1. 添加debug信号 可以对模块端口或 ...

- SignalTap II Logic Analyzer 无法观测到信号?

在Quartus SignalTap 工具中加入信号,发现加入的信号变成红色,如图所示的data_slave[7..0]: 这样的信号是没有办法观测的,不会根据SignalTap 的Clock和Tri ...

- Vivado 设计套件

疑惑 有一天我在上网,逛着逛着看到一个叫https://pan.baidu.com/s/16Nu03YJLuz_aYuGQMm_8oQ的链接,那个网页的标题好像叫"Vivado 2017.4 ...

- vivado2015.4保存ila波形数据

reference: https://www.cnblogs.com/pejoicen/p/d8b3c4f3aa29b8de7963893d4b99d361.html Vivado2015.4下,il ...

随机推荐

- Nand Flash与Nor

转:http://www.360doc.com/content/11/1215/15/1299815_172458274.shtml Flash经常在一些地方被提到,一直没认真去理解它们的区别,因此, ...

- Tesseract训练中文字体识别

注:目前仅说明windows下的情况 前言 网上已经有大量的tesseract的识别教程,但是主要有两个缺点: 大多数比较老,有部分内容已经不适用. 大部分只是就英文的训练进行探索,很少针对中文的训练 ...

- Android内存优化11 内存泄漏常见情况2 内部类泄漏

线程持久化 Java中的Thread有一个特点就是她们都是直接被GC Root所引用,也就是说Dalvik虚拟机对所有被激活状态的线程都是持有强引用,导致GC永远都无法回收掉这些线程对象,除非线程被手 ...

- [转]ASP.NET Core 1.0: Using Entity Framework Core 1.0 - Transaction

本文转自:http://blog.csdn.net/alvachien/article/details/51576961 跟Entity Framework之前的版本不同,Class DbContex ...

- android 启动socket 失败:socket(af_inet sock_stream 0) 返回-1

Android 启动socket 失败:socket(af_inet sock_stream 0) 返回-1 原因权限问题, 应该添加如下权限: <uses-permission android ...

- iconv的安装和使用

一.Linux下iconv的安装包的下载页面http://www.gnu.org/software/libiconv/ $ ./configure --prefix=/usr/local$ make$ ...

- 一步一步学RenderMonkey(3)——改良Phong光照模型 【转】

转载请注明出处: http://blog.csdn.net/tianhai110 改良后的Phong光照模型: 上一节实现的phong镜面光照模型,如果固定光源,移动视点(及matView 关联为ma ...

- thinkphp3.2中在模板页面使用运算符

首先要明确的是,ThinkPHP 内置模板引擎支持在模板中使用算术运算符(+.-.*./ 和 %),例子: public function index(){ $x = 1; $y = 2; $z = ...

- Maven Web项目配置Mybatis出现SqlSessionFactory错误的解决方案

一.错误现象 严重: Context initialization failed org.springframework.beans.factory.BeanCreationException: Er ...

- 一个tomcat中部署多个项目

在各自的项目web.xml中添加 <context-param> <param-name>webAppRootKey</param-name> <param- ...