Xilinx RocketIO模块的介绍

摘要: 在高速电路系统设计中,差分串行通信方式正在取代并行总线方式,以满足系统对高带宽数据通信的需求。RocketIO是Virtex2 Pro以上系列FPGA中集成的专用高速串行数据收发模块,可用于实现吉比特的数据传输,适用于多种高速数据传输协议。依据实际工程应用需求,提出了基于RocketIO的高速串行数据传输系统解决方案,实现了每通道2.5 Gb/s的传输速度。最后介绍了RocketIO在Aurora和PCI Express协议实现中的应用,并总结了高速通信系统的共性特征。

引言

随着电子系统对速度以及精度要求的提高,高速串行数据通信模式正在逐步取代传统的并行总线式结构。并行总线结构由于其固有的缺点,在速度上的提升空间已经很小。

① 并行总线在印制电路板上要占用大量的空间,在电路系统日益小型化的今天给系统的设计带来很大困难。如PATA66以上的PATA排线数量达到了80根,使得电路板的布线极为困难。

② 并行总线由于在布线时很难保证每条线路长度与电气特征一致,导致信号到达时间不同,在较高的工作频率下很难实现完全同步,以致出现信号偏移。这使接收器难以确定采样时间,容易造成数据错误。

③ 由于寄生电容的影响,在并行的两条数据线中容易产生串扰,甚至改变信号原有真实电平。采用地线进行屏蔽可以在一定程度上消除串扰,但同时也造成总线线路数目的急剧增加。

④ 并行总线参考电平为地电平,容易受噪声干扰。同时由于在总线上“0”、“1”分布不均匀,在信号收发器之间易造成直流偏置,造成信号噪声容限降低。

相比而言,高速串行总线采用差分对的形式,并且在发送端与接收端之间采用点对点的连接结构。差分信号经过编码,消除信号序列中直流分量,从而可以提高噪声容限。同时,在信号序列中插入时钟信息,信号中携带时钟,解决了信号偏移问题。

在嵌入式应用方面,主流的FPGA中都已对差分信号提供了硬件支持,如Xilinx公司推出的Virtex系列FPGA中,相邻的两个I/O口都以差分信号对形式出现。从Virtex2 Pro系列开始,更是在片上集成了固化的RocketIO模块,以提供高超高速的串行通信支持。本文将从工程应用的角度出发介绍RocketIO的相关特征,并探讨其在高速数据传输中的应用。

1 RocketIO

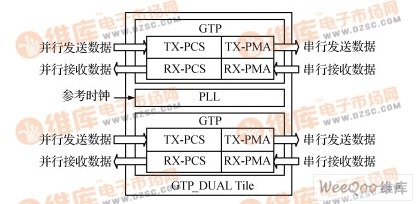

RocketIO收发器是在Virtex2 Pro以上系列FPGA中集成的专用串行通信模块,在使用时不占用FPGA其他逻辑与片上存储资源。在Virtex5 LXT和SXT系列FPGA中,RocketIO称为GTP,每两个GTP共用一个PLL,组成一个GTP_Dual。其结构框图如图1所示。

图1 GTP_Dual Tile结构框图

每一个RocketIO收发器均具有如下特征:

◆ 具有可配置终端、电压摆幅与耦合的电流模逻辑串行驱动或缓冲器。

◆ 可编程发送预加重和接收均衡,以实现最优信号完整性。

◆ 100 Mb/s~3 Gb/s的线速范围,线速在100 Mb/s~500 Mb/s区间时具有可选的5倍过采样功能。

◆ 可选的嵌入式PCS功能,例如8位/10位编码、逗号对齐、通道绑定以及时钟校正。

◆ 最小化的确定性数据通道延迟。

◆ 对PCI Express、SATA、光纤传输等协议的支持。

从应用上讲,RocketIO处于数据传输协议的物理层,用以实现最基本的数据通信环境。其主要功能可以概括为:将输入的并行数据经过编码,转化为高速的差分串行信号。在实际应用中,输入时钟、PLL参数设置以及PCB线路的设计与布局是影响数据传输效果的最重要因素。

1.1 输入时钟

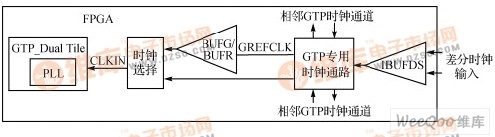

RocketIO有三种时钟输入方式:专用差分时钟、共享邻近GTP_Dual的时钟、以及使用FPGA内部时钟。Rocket I/O GTP时钟输入方式如图2 所示。

图2 Rocket I/O GTP时钟输入方式

使用专用差分时钟时,差分的时钟信号通过输入差分缓冲器变为单端时钟,输入到GTP_Dual Tile中的PLL,当使用的时钟源精度满足要求时具有最优的时钟稳定性。

从相邻GTP_Dual Tile获得时钟时需要使用GTP专用的时钟通路,但此时GTP_Dual与提供时钟的GTP_Dual Tile间隔的GTP_Dual Tile个数不能超过两个,即每对差分输入时钟最多可驱动7个GTP_Dual Tile。

相比于上述两种时钟输入方式,从FPGA内部获得时钟时钟精度最差。这是因为,FPGA内部使用的时钟经过逻辑电路以及BUFG或BUFR缓冲后,会引入较大的时间抖动。但由于在FPGA内部可以灵活变换参考时钟频率,因此在速度与精度要求不太高的场合可采用FPGA内部时钟。经实验验证,对于误码率要求在1‰以下的应用,从FPGA内部获得的时钟信号可以满足要求。

1.2 PLL参数设置

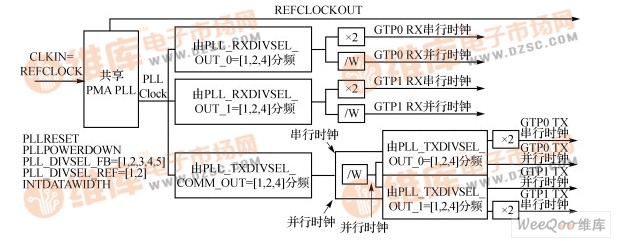

时钟信号输入到GTP_Dual Tile内部后还需要经过PLL的进一步处理才能使用。PLL可向两个RocketIO提供相互独立的各种时钟信号。PLL内部时钟变换结构如图3所示。

图3 PLL内部时钟变换结构

需要注意的是,由于此PLL可用参数(PLL_DIVSEL_FB = [1,2,3,4,5], PLL_DIVSEL_REF = [1,2])有限,为获得高速串行通信所需频率,输入参考时钟CLKIN仅可在有限范围内选择。因此,参考时钟需通过专用的具有相应频率的晶振提供或在FPGA内部经DCM或PLL变换获得。

1.3 PCB设计

RocketIO产生的高速串行信号速度在1 GHz以上时,已经进入微波范围。因此在使用时,其PCB电路的制作也是影响信号传输效果的重要因素。

RocketIO的供电必须由专用的电源管理模块提供,不能与其他模块电源共享,以减少噪声引入。即使GTP中同一种电源的不同引脚之间也需要通过滤波电路进行隔离,以减少相互之间的影响。为平衡GTP_Dual Tile的负载,只使用其中的一个GTP时,两个GTP的供电应以同样策略进行处理。

在布线时,高速差分对走线应当有最高的优先级,以保证其电气特性满足微带线或带状线的要求。走线应当尽量直、短并具有最少的信号层变化。为减少干扰信号的影响,高速线应尽量远离其他有可能会带来噪声的信号线,同时信号线拐角采用45°而避免使用直角。为保证信号的完整性,高速差分信号线的参考平面须保持连续,并尽量以地平面为参考,否则其阻抗特性会发生急剧变化,导致信号的反射增强。

2 RocketIO在高速信号传输中的应用

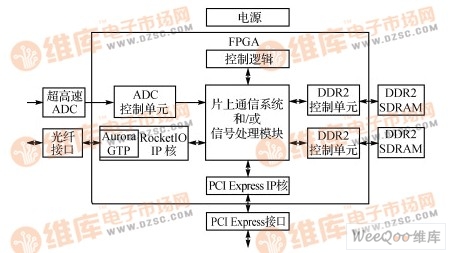

在多种高速数据处理场合都需要对数据进行高速收发。以超高速信号采集系统为例,当采用ADC08D1500采集芯片时,最高可以实现单通道3 Gsps的超高速采样率,数据精度为8位。这时就需要具有足够高传输速率的信号传输机制对信号进行转发。若实现机内通信,可采用PCI Express传输协议;若实现系统间通信,则可使用光纤通信协议或千兆以太网协议。在工程中,上述协议都可通过专用的芯片来实现,但也使得系统变得复杂,同时使电路板的设计空间紧张。而RocketIO对多种高速传输协议的支持,可以使得PCI Express协议、光纤传输协议或千兆以太网协议在同一片FPGA内实现,提高了系统的集成度,并使得信号的处理机制更加灵活。在本文的设计中,采用了PCI Express传输协议来实现机内通信,采用Aurora光纤传输协议来实现系统间通信。系统结构如图4所示。

图4 超高速采集系统框图

2.1 Aurora协议

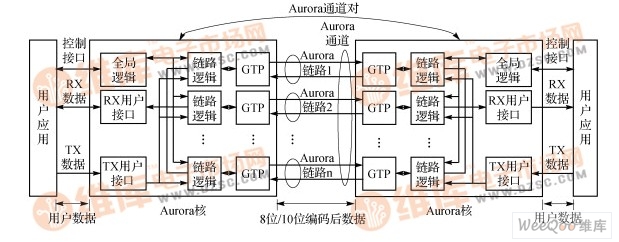

Aurora协议是一种可配置的、简便的数据链路层协议,可以通过使用一条或多条高速串行通道实现点对点的数据传输。Aurora协议可为私有上层协议或标准上层协议提供透明接口的串行互联协议,允许任何数据分组通过Aurora协议封装,并在芯片间、电路板间甚至机箱之间传输。Xilinx还开发了实现该协议的Aurora IP核,当使用Virtex5 FPGA提供的RocketIO时,Aurora可实现每个物理通道500 Mb/s到3.75 Mb/s的传输速率。Aurora可将1~16个物理通道绑定在一起,形成一个由16个通道绑定而成的虚拟链路,提供最高60 Gb/s的传输波特率[1]。其结构如图5所示。

图5 Aurora核结构

Aurora核可以帧模式或流模式传输数据[4]。Aurora的帧可以是任意大小,并可以在任意时刻被中断。有效数据之间被自动以空闲(idles)序列信号填充,以维持通道的锁定。帧模式下有可选的数据流控制信号,以降低接收数据速率,或传送简短而优先级高的信息。流模式在Aurora核中以一个无结尾的帧方式实现。在数据传输的间隙补以空闲序列信号。

2.2 PCI Express协议

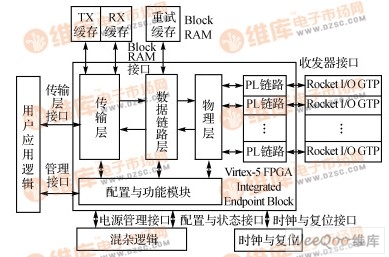

PCI Express是PCI、PCIX协议的下一代协议,是一种广泛适用于计算和通信平台的高性能通用互联结构。同Aurora协议相似,PCI Express协议采用点到点的串行链接,单通道可实现2.5 Gb/s的传输速率,最高可使用16个通道实现40 Gb/s的高速通信。Xilinx公司开发的集成的PCIE IP核(Integrated Endpoint Block)可实现最高8个RocketIO通道的绑定,以此为物理层基础实现20 Gb/s的传输速率。PCI Express协议包含传输层、数据链路层和物理层,其在FPGA上基于RocketIO实现的结构框架如图6所示。

图6 Xilinx PCIE IP核结构框图

2.3 高速信号传输系统的共性

RocketIO可应用于多种高速数据处理应用的场合,这是由于高速信号传输系统结构都可以概括为三个组成部分,并且传输协议分层实现的方式使得系统协议与硬件系统之间具有一定的独立性。

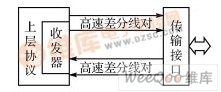

图7 高速信号传输系统框架图

高速信号传输系统的实现方式多种多样,但一般均由上层协议、高速收发器以及传输接口组成。其结构框架如图7所示。

上层协议:根据不同的任务需要,为实现高速信号传输制定的传输协议多种多样,包含的层数也不同。如PCI Express协议具有物理层、数据链路层以及传输层,Aurora协议具有物理层和数据链路层,10 Gb/s以太网协议(XAUI)包含物理层和数据链路层。用户程序可使用这些传输协议实现数据的收发。

高速收发器:高速收发器是所有传输协议都必须具备的物理层,是实现高速信号传输的基础。一般实现串并转换、时钟数据恢复、线路编码、线路绑定等功能,可为多种上层协议提供硬件支持。Xilinx公司推出的RocketIO与Altera公司推出的Rapid IO等都可看作高速收发器。

传输接口:在高速的信号传输系统中传输接口与高速收发器之间通过差分线连接,可实现全双工的双向传输。接口形式与具体应用相关,如实现PCI Express传输协议的PCIE接口、实现光线传输协议的光线接口以及实现高速以太网通信的网络接口等。

其中相同的高速收发器可以应用于使用不同传输协议的系统中,所连接的接口根据不同应用而有不同形式。如RocketIO既可用于Aurora光纤通信协议,也可用于PCI Express协议。而在Aurora协议中,RocketIO与光纤接口相连,在PCI Express协议中,RocketIO与PCIE接口相连。

结语

综上所述,RocketIO通过提供高速的串并转换、时钟与复位管理、线路编解码等功能,为实现高速的串行数据传输提供了良好的物理层基础。RocketIO对多种高速传输协议的支持使得其在嵌入式系统中得到了广泛的应用,也使得用户在选择使用成熟的IP核之外,可以根据实际需要利用RocketIO开发专用模块,实现高效、稳定的数据传输。

转载:http://blog.csdn.net/wordwarwordwar/article/details/52939948

Xilinx RocketIO模块的介绍的更多相关文章

- 基于Metronic的Bootstrap开发框架--工作流模块功能介绍(2)

本篇继续<基于Metronic的Bootstrap开发框架--工作流模块功能介绍>,继续介绍基于Metronic的Bootstrap开发框架的工作模块功能,介绍工作流模块中相关业务表单的界 ...

- Winform开发框架中的内容及文档管理模块功能介绍

在开发项目的时候,我们有一些场景需要编辑一些HTML文档,作为内容发布系统的一部分,有时候也需要对一些文档如WORD文档进行编辑管理,这样需要我们对这些内容及文档进行合适的管理.本文主要介绍在WInf ...

- Xilinx 常用模块汇总(verilog)【04】

作者:桂. 时间:2018-05-15 13:07:02 链接:http://www.cnblogs.com/xingshansi/p/9040472.html 前言 Xilinx 常用模块汇总(v ...

- Xilinx 常用模块汇总(verilog)【03】

作者:桂. 时间:2018-05-10 2018-05-10 21:03:44 链接:http://www.cnblogs.com/xingshansi/p/9021919.html 前言 主要记 ...

- python shutil模块简单介绍

python shutil模块简单介绍 简介 shutil模块提供了大量的文件的高级操作.特别针对文件拷贝和删除,主要功能为目录和文件操作以及压缩操作. shutil 模块方法: copy(src, ...

- request 模块详细介绍

request 模块详细介绍 request Requests 是使用 Apache2 Licensed 许可证的 基于Python开发的HTTP 库,其在Python内置模块的基础上进行了高度的封装 ...

- tensorflow中slim模块api介绍

tensorflow中slim模块api介绍 翻译 2017年08月29日 20:13:35 http://blog.csdn.net/guvcolie/article/details/77686 ...

- 【MM系列】SAP MM模块-组织结构介绍

公众号:SAP Technical 本文作者:matinal 原文出处:http://www.cnblogs.com/SAPmatinal/ 原文链接:[MM系列]SAP MM模块-组织结构介绍 ...

- 日志模块详细介绍 hashlib模块 动态加盐

目录 一:hashlib模块 二:logging 一:hashlib模块 加密: 将明文数据通过一系列算法变成密文数据(目的就是为了数据的安全) 能够做文件一系列校验 python的hashlib提供 ...

随机推荐

- 分享Kali Linux 2017年第29周镜像文件

分享Kali Linux 2017年第29周镜像文件 Kali Linux官方于7月16日发布2017年的第29周镜像.这次维持了11个镜像文件的规模.默认的Gnome桌面的4个镜像,E17.KDE ...

- c++基础学习之函数与参数

1.传值参数 //传值参数 int Abc(int a,int b,int c) { ; } a,b和c是函数Abc 的形式参数formal parameter,类型均为整型.如果在如下语句中调用函数 ...

- POJ 3494 Largest Submatrix of All 1’s(最大子图形)

[题目链接] http://poj.org/problem?id=3494 [题目大意] 在01矩阵中求最大全1子矩形 [题解] 在处理每个点的时候,继承上一个点等高度下的左右最大扩展, 计算在该层的 ...

- 详细User-Agent大全

目录: Android: Android 0.* Android 1.* Android 2.* Android 3.* Android 4.* Windows Phone OS BlackBerry ...

- 5.6(java学习笔记) queue

一.queue接口 queue的中文意思是队列,是一种以先进先出方式处理数据的集合. 队列还提供额外的插入.提取和检查操作.这些方法都以两种形式存在:一种在操作失败时抛出异常,另一种返回特殊值(根据操 ...

- hadoop LineRecordReader

/** * * @param job 配置信息 * @param split split * @param recordDelimiter 分列的字符 * @throws IOException */ ...

- UITextField的returnkey点击事件

关于隐藏软键盘,网上的办法良莠不齐,大多是通过实现UITextFieldDelegate来隐藏软键盘,该方法代码较多,且在文本框很多的时不好处理.我经过搜索与摸索,找到了最佳的处理办法.(引用的)一. ...

- t-sql 笔记(1)

Toad-for-SQL-Server-Freeware 1.查询哪些数据库对象使用了某个表 SELECT b.[name], a.[definition] FROM sys.all_sql_modu ...

- 设置html属性为disabled时flask后台获取数据失败

标签input的值如果不需要用户修改,则设置属性为 readonly,不要设置为 disabled.因为设置disabled会导致flask后端获取不到这个input得value rule_maker ...

- Maven 使用 二——nexus

上篇博客介绍了创建maven项目的两种方式,当中一种是使用命令行的方式来创建,这种情况非常少,一般我们都有IDE开发环境.所以接下来,我们还是在一个详细的IDE中来说,我使用的是Eclipse. 一. ...