FFT HDL Optimized模块HDL综合代码生成及与Xilinx xfft IP MEX接口精度详细比较

Parameters:

具体步骤:

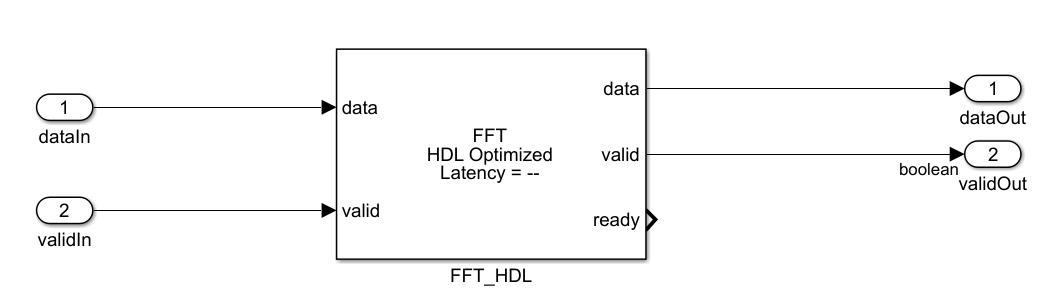

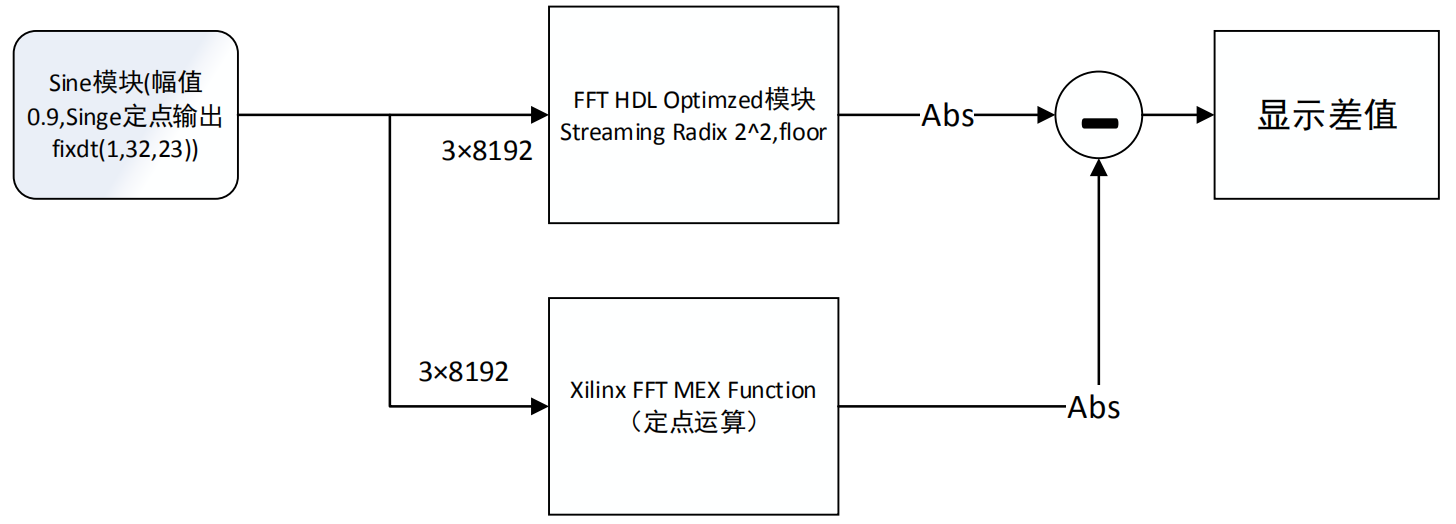

Simulink 整体框图例如图所示:(for example)

subsys 子系统框图如图所示:

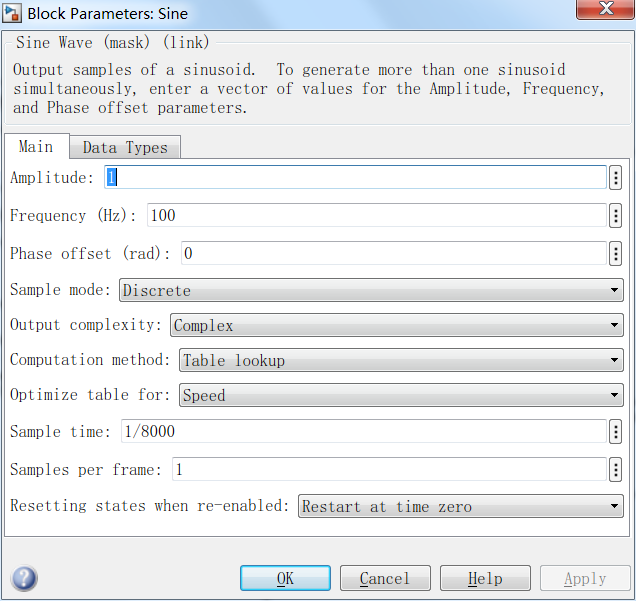

其中 valid 给高电平,输入有效,而 data 通过 Sine Wave 模块进行输入,其中 fft_input_s、fft_hdl_in、fft_hdl_out 均为 To Workspace 模块(Savemode 选择 array),convert 模块转换输入的数据形式:32 位 1D array of complex data 浮点->32 为 fixdt(1,32,14),To Sample 模块改变输出信号的采样模式。重要模块的参数设置如图:

Sine Wave 模块

FFT HDL Optimized 模块

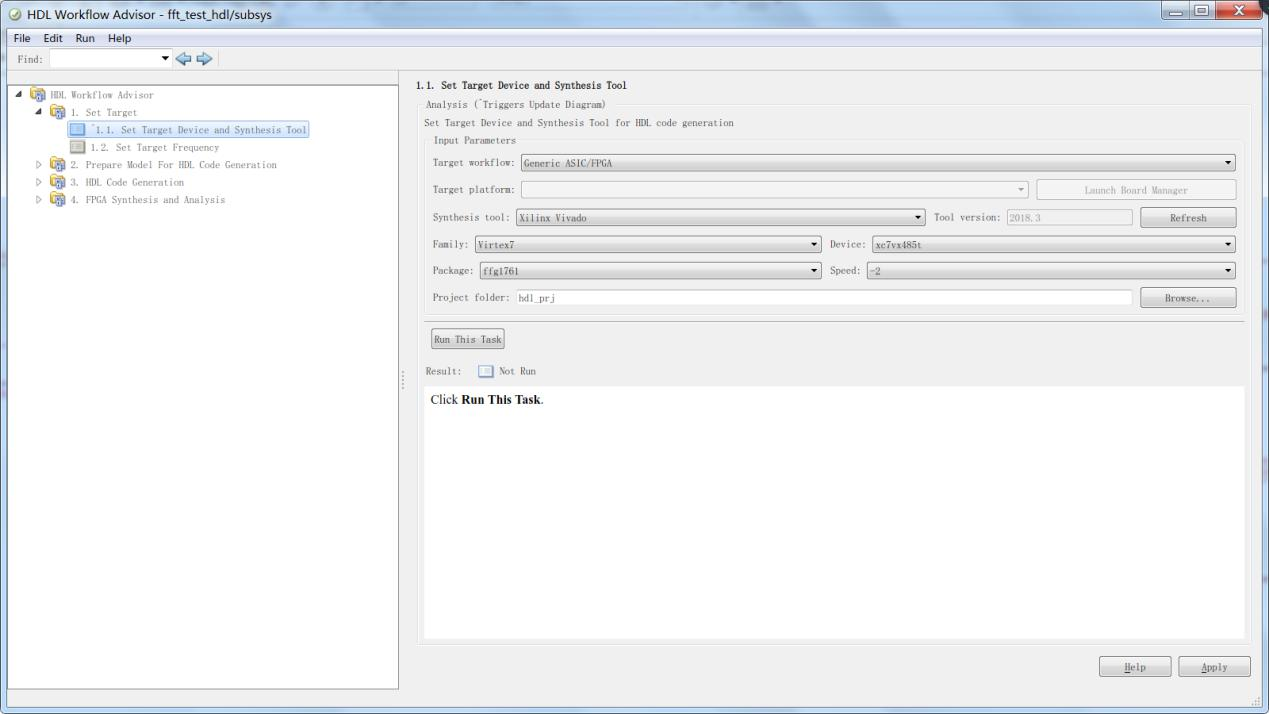

(8)在 HDL Workflow Advisor 窗口中,在 Set Target > Set Target Device and Synthesis Tool step, for Synthesis tool, select Xilinx Vivado and click Run This Task;

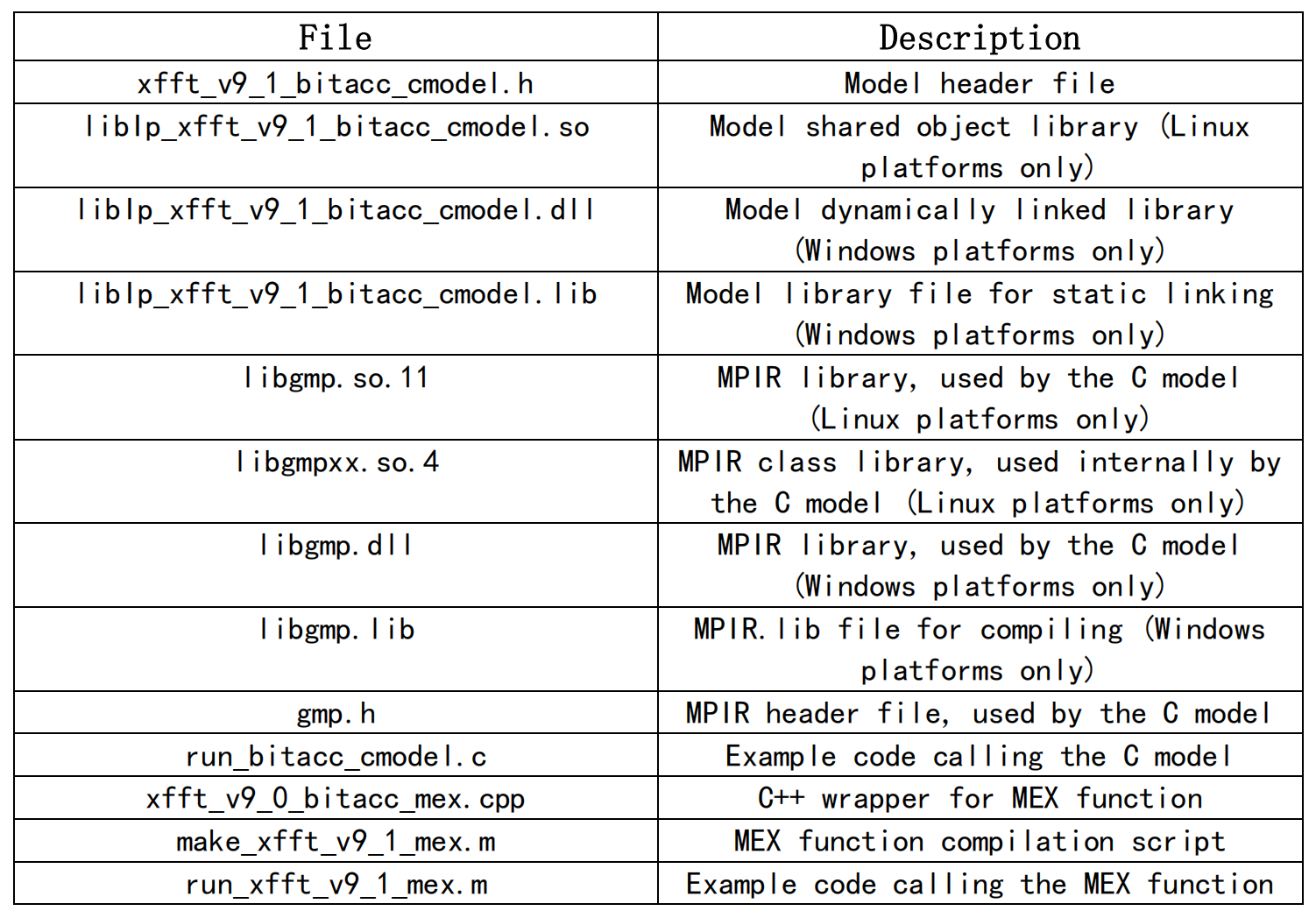

(19)打开 MATLAB,在 MATLAB 命令窗口跳转到xfft_v9_1_bitacc_cmodel_nt64.zip 压缩包解压文件目录下;

1 generics.C_NFFT_MAX = 13; %fft length = 8192

2 generics.C_ARCH = 2; %Burst Radix 2

3 generics.C_HAS_NFFT = 0;

4 generics.C_USE_FLT_PT = 1; %浮点

5 generics.C_INPUT_WIDTH = 32; % Must be 32 if C_USE_FLT_PT = 1

6 generics.C_TWIDDLE_WIDTH = 24; % Must be 24 or 25 if C_USE_FLT_PT =1

7 generics.C_HAS_SCALING = 0; % Set to 0 if C_USE_FLT_PT = 1

8 generics.C_HAS_BFP = 0; % Set to 0 if C_USE_FLT_PT = 1

9 generics.C_HAS_ROUNDING = 0; % Set to 0 if C_USE_FLT_PT = 1

1 % % Check xk_re and xk_im data: Only xk_re[0] should be non-zero

2 % if output(1) ~= expected_xk_re_0

3 % if channels > 1

4 % error('ERROR: Channel %d xk_re[0] is incorrect:

5 expected %f + j%f, actual %f +

6 j%f\n',channel,real(expected_xk_re_0),imag(expected_xk_re_0),real(out

7 put(1)),imag(output(1)))

8 % else

9 % error('ERROR: xk_re[0] is incorrect: expected %f + j%f,

10 actual %f +

11 j%f\n',real(expected_xk_re_0),imag(expected_xk_re_0),real(output(1)),

12 imag(output(1)))

13 % end

14 % end

15 %

16 % % Check all other sample values are zero

17 % for n = 2:samples

18 % if output(n) ~= 0 + 0j

19 % if channel > 1

20 % error('ERROR: Channel %d output sample %d is incorrect:

21 expected %f +j%f, actual %f +

22 j%f\n',channel,n,0.0,0.0,real(output(1)),imag(output(1)))

23 % else

24 % error('ERROR: output sample %d is incorrect: expected %f

25 +j%f, actual %f + j%f\n',n,0.0,0.0,real(output(1)),imag(output(1)))

26 % end

27 % end

28 % end

测试说明:

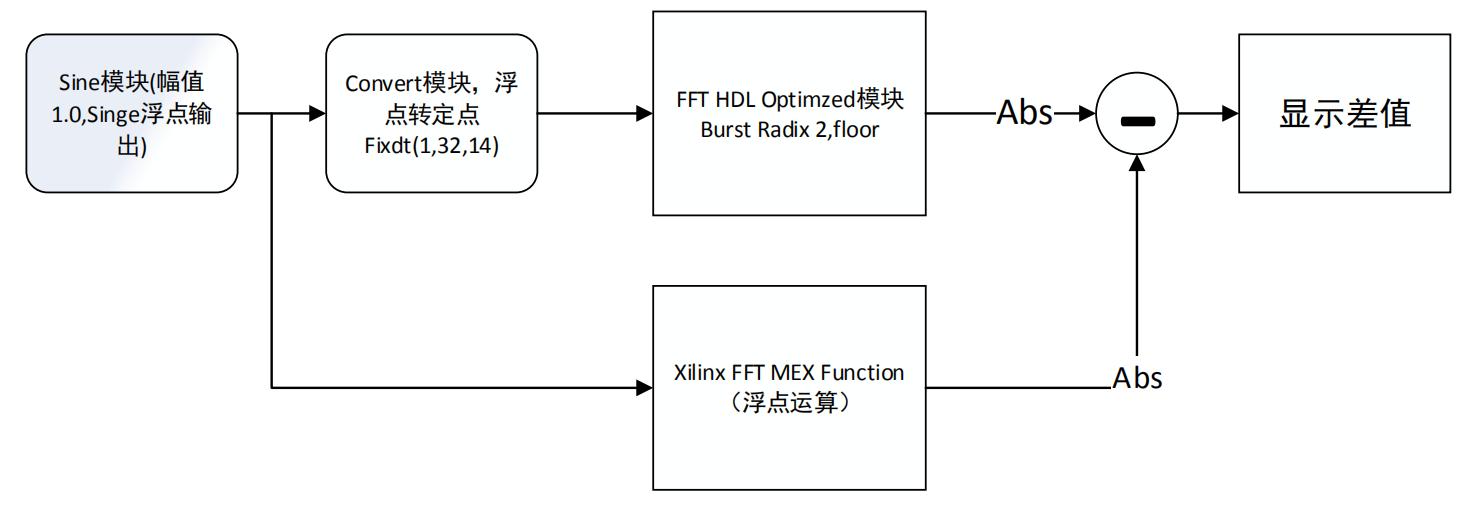

测试一

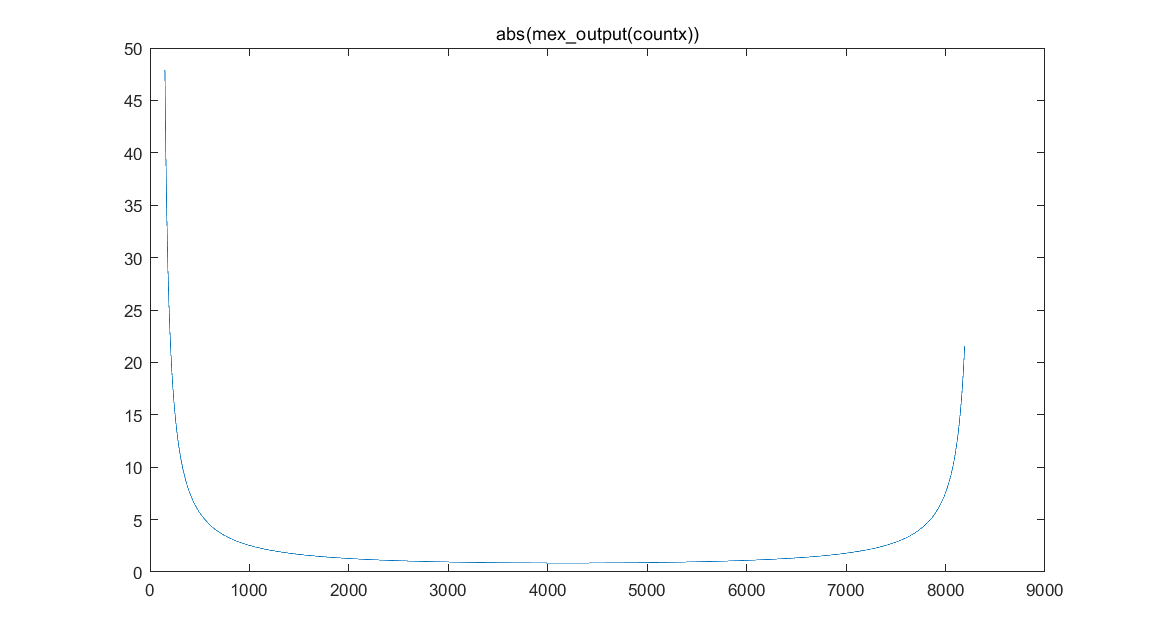

abs(fft_hdl_out_test(countx)- output(countx))

abs(fft_hdl_out_test(countx)- output(countx))

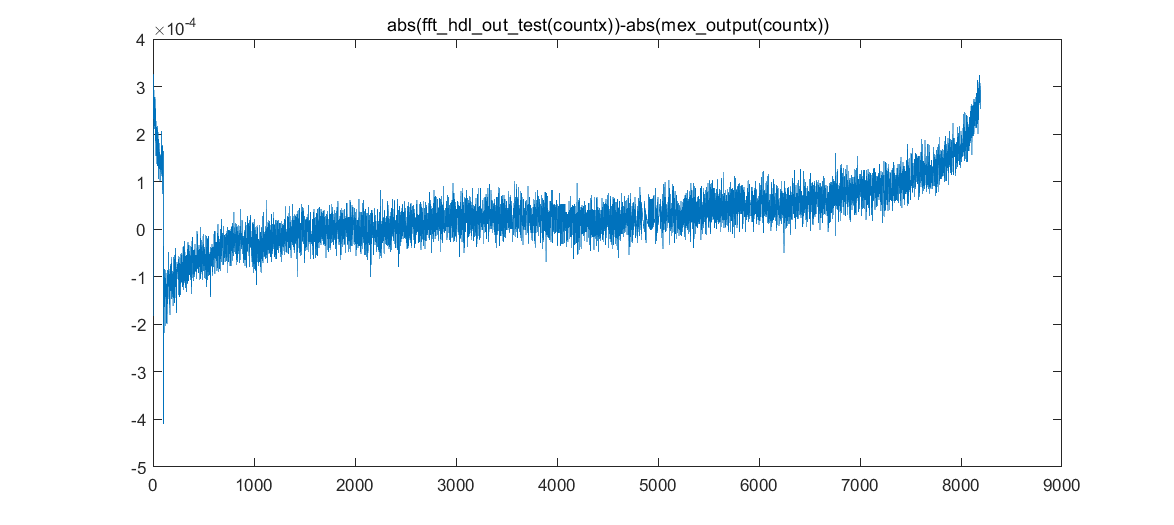

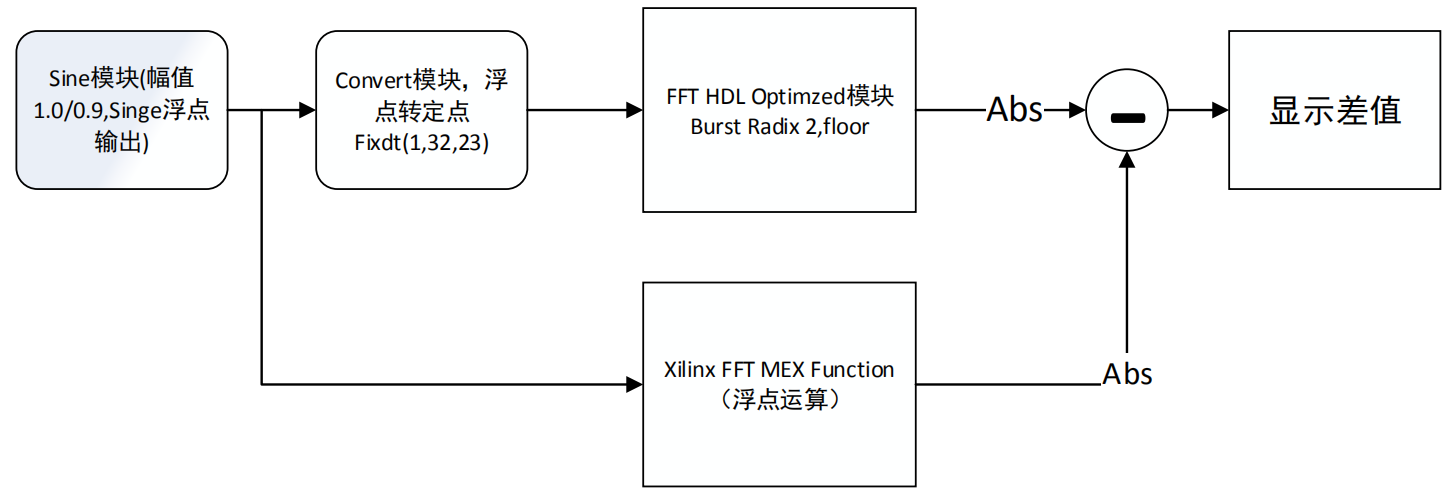

测试二

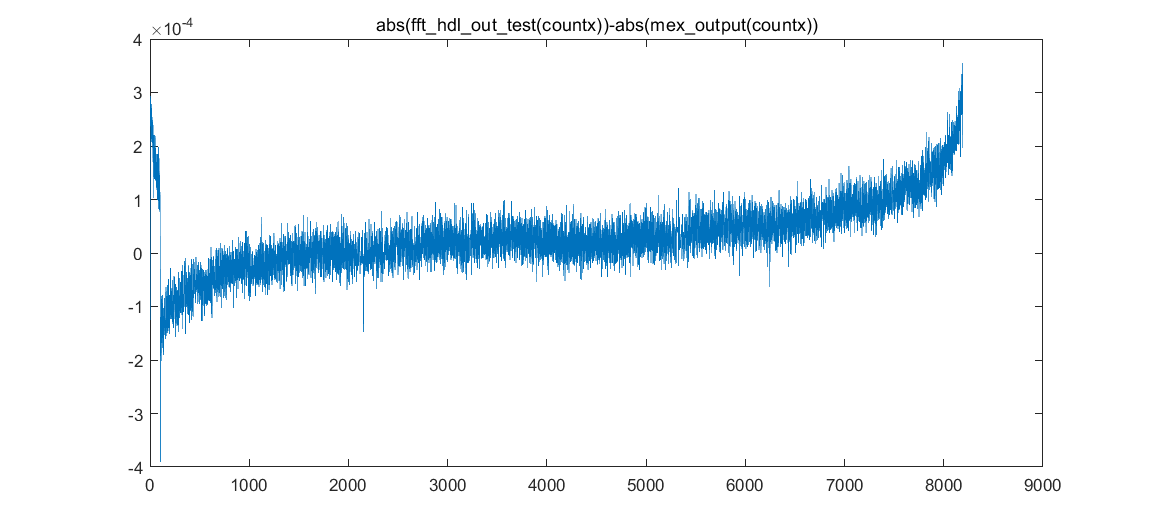

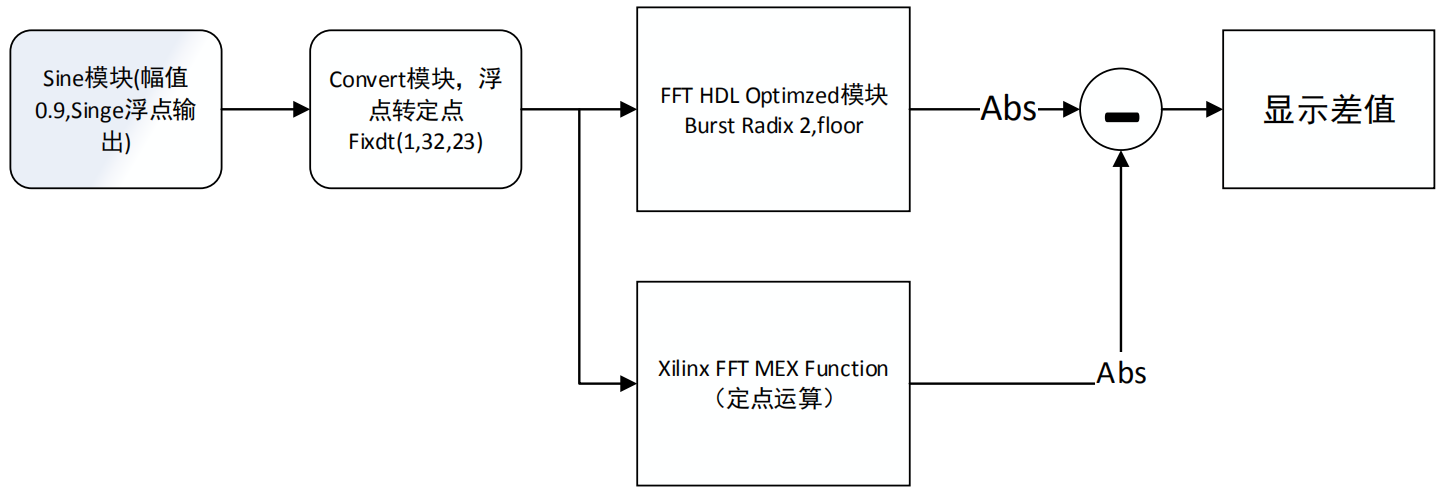

测试三

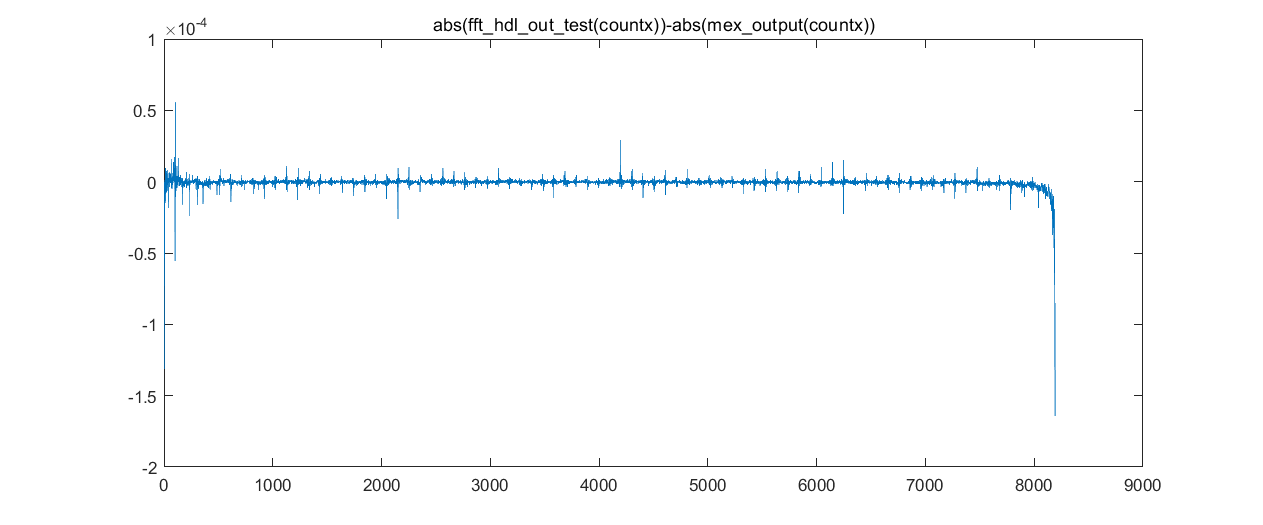

测试四

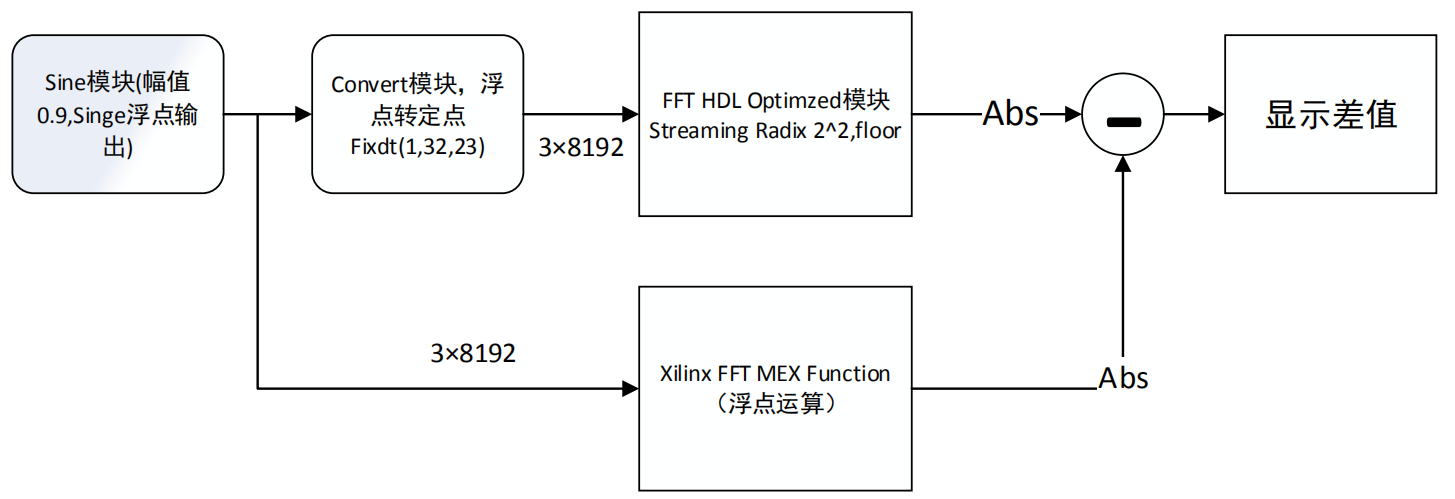

测试五

Xilinx FFT MEX 函数的接口的运算方式设置为浮点测试, fixdt(1,32,23),与 IEEE-754 single-precision 格式一致,小数部分为 23 位二进制精度,

Xilinx FFT MEX 函 数 的 接 口 的 运 算 方 式 设 置 为 浮 点 测 试 ,fixdt(1,32,23),与 IEEE-754 single-precision 格式一致,小数部分为 23位二进制精度,结构改为 Streaming Radix 2^2 ,此为测试五第三个 8192点

Xilinx FFT MEX 函 数 的 接 口 的 运 算 方 式 设 置 为 定 点 测 试 ,fixdt(1,32,23),与 IEEE-754 single-precision 格式一致,小数部分为 23位二进制精度,且 run_xfft_v9_1_mex.m 文件中 generics.C_TWIDDLE_WIDTH设置为 26;结构改为 Streaming Radix 2^2 ,此为测试五第三个 8192 点

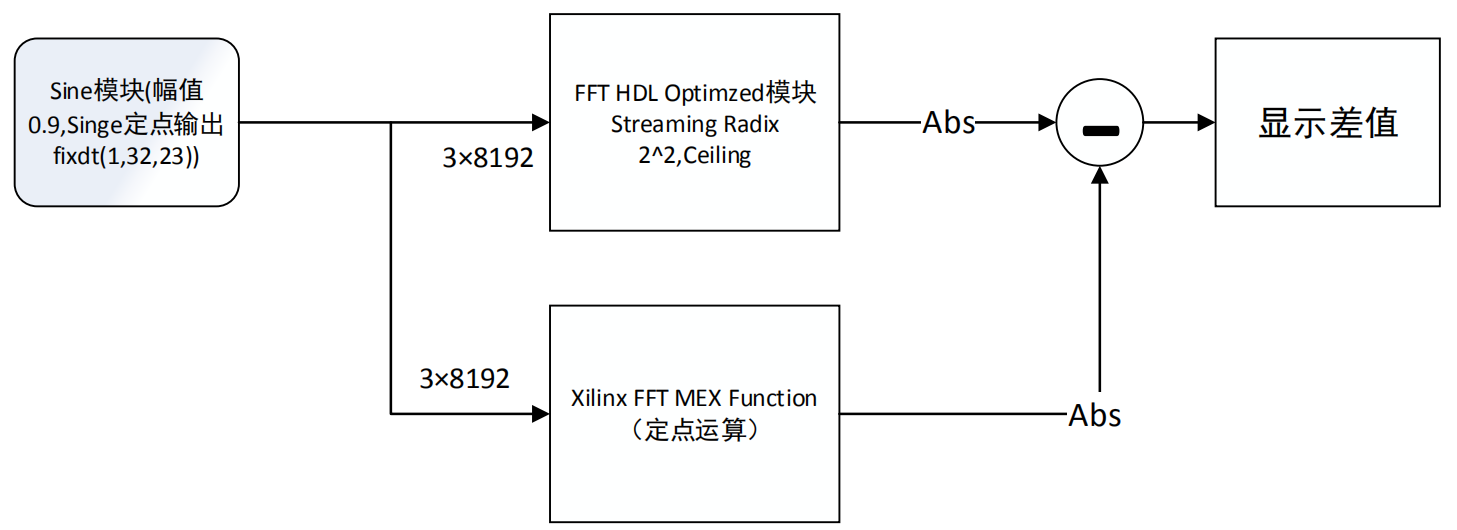

测试六

测试七

测试八

测试结果说明:

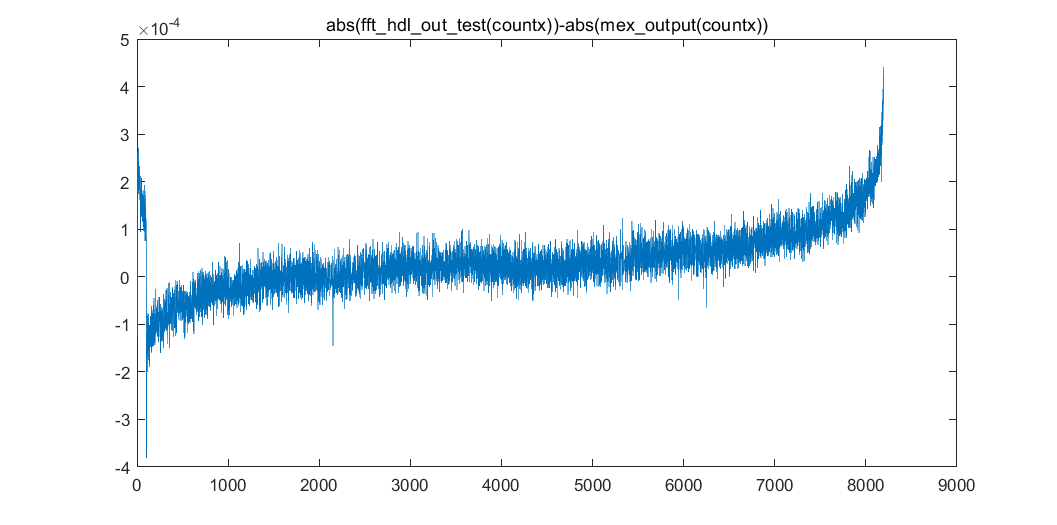

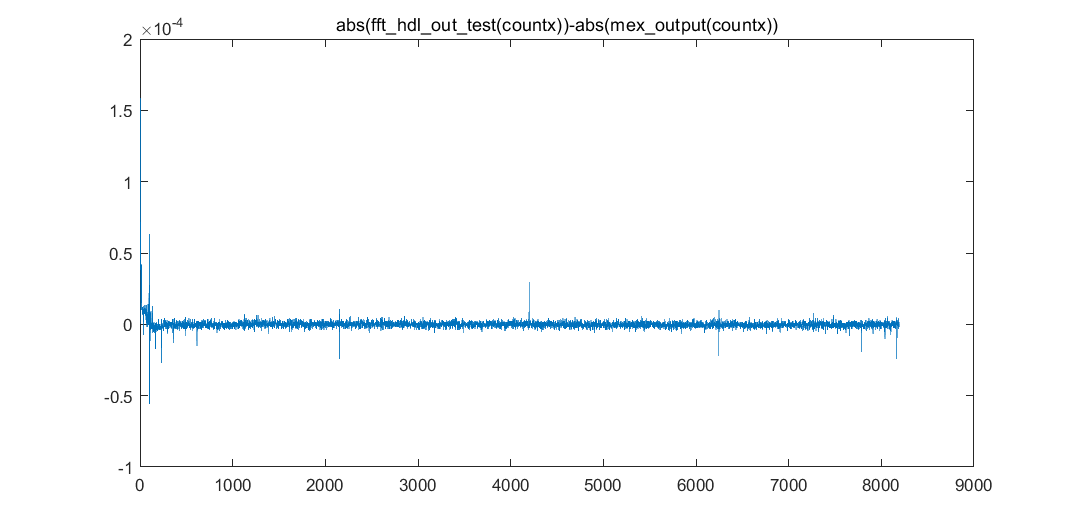

(1)测试一

通过测试一结果图可以看出其运算误差有点大,经过后面测试可以发现其主要原因是因为convert模块的fixdt(1,32,x)中x的影响,测试二及以后的测试均与 IEEE-754 single-precision 格式一致,小数部分为23位二进制精度,即fixdt(1,32,23)。

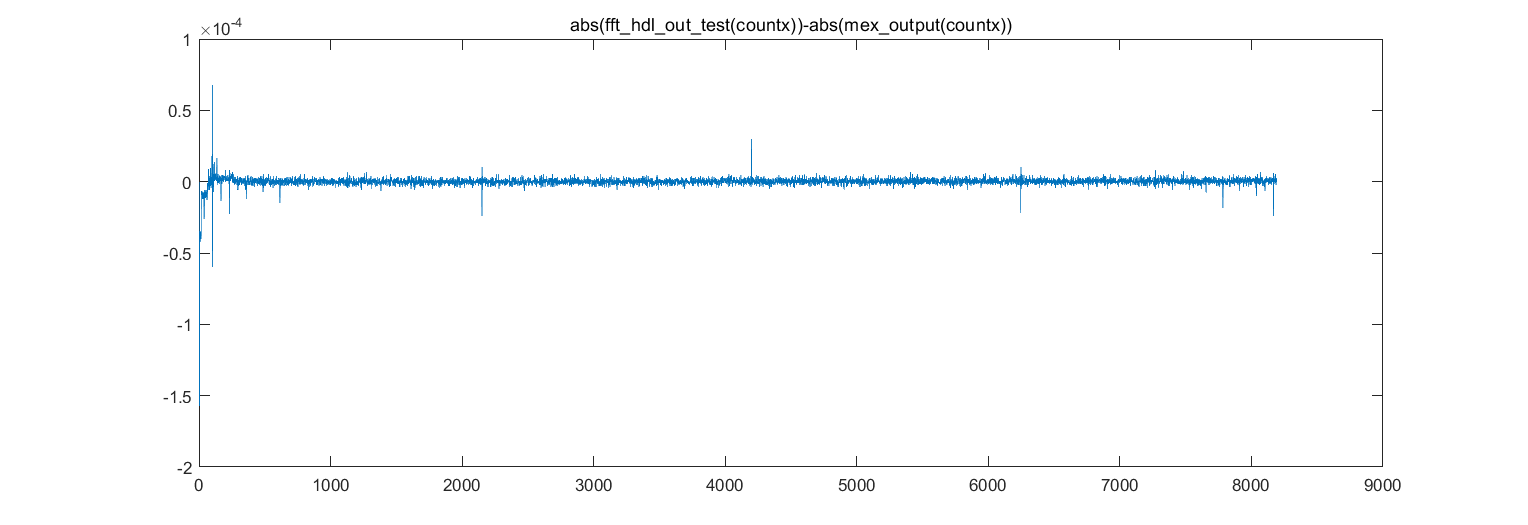

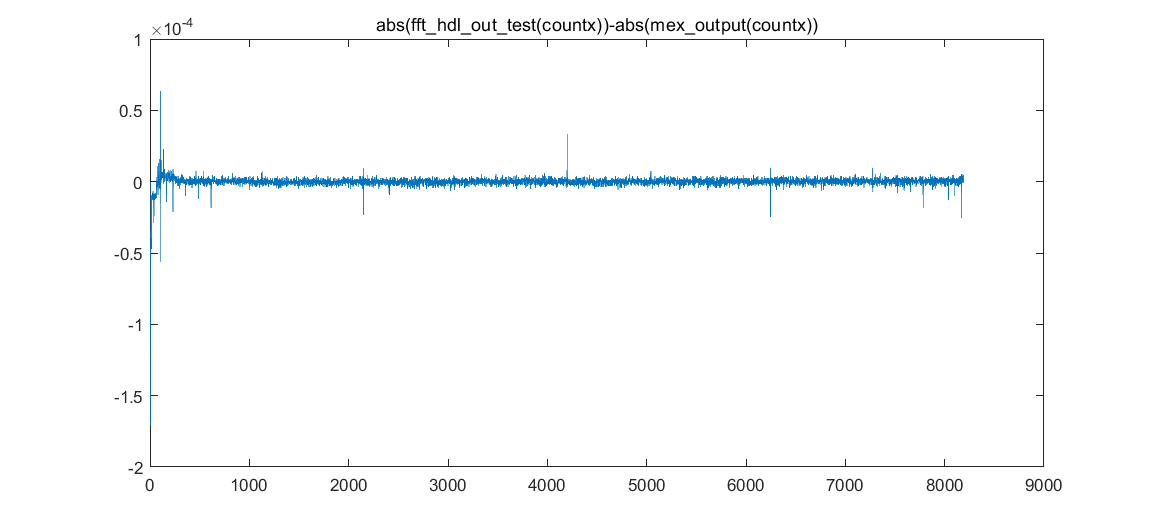

(2)测试二与测试三

在修改前面的浮点转定点参数后,FFT HDL Optimized 模块的运算结果变得精确了,误差较小,差值大概在±2×10-4,diff/reference 大概在 10-5 左右,而为什么选择 0.9 幅值,是因为在做定点运算的时候,Sine 模块幅值 1.0 在输入至 Xilinx FFT MEX Function 在运算中会产生溢出,经测试,1.0 与 0.9 产生的结果基本一致。

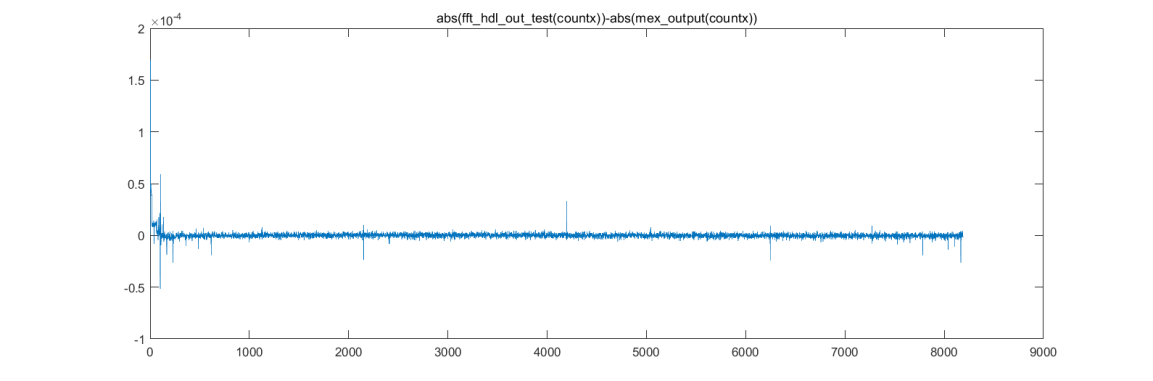

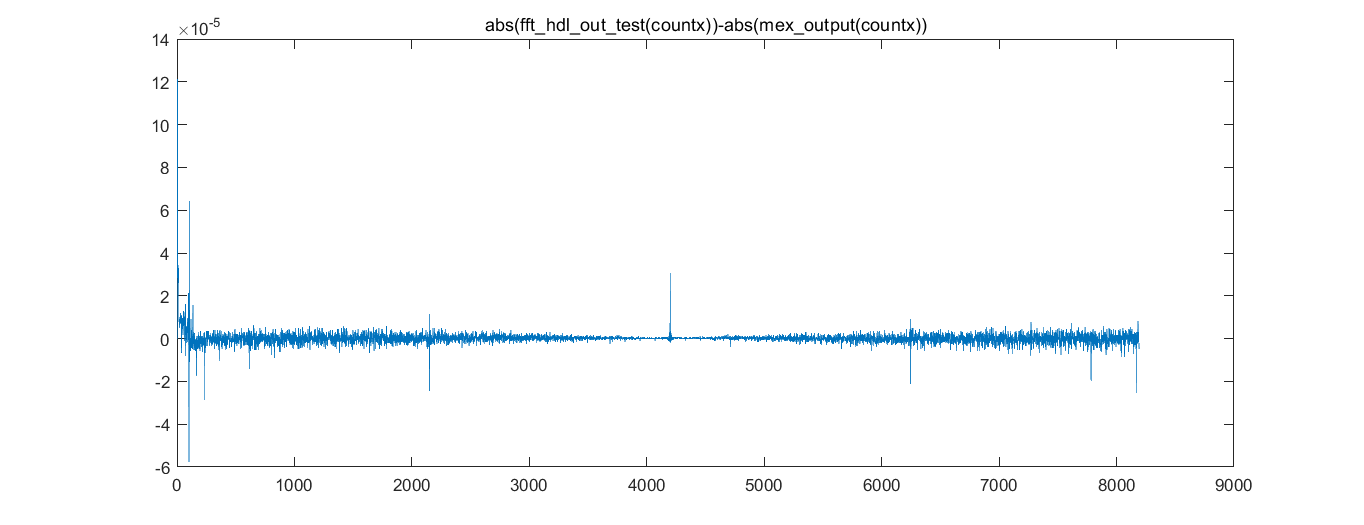

(3)测试四

测试四是与测试三对应的,除了修改了 MEX 定点参数,其他均没有变化,进行定点测试。在定点测试结果中,差值大概在±8×10-6,diff/reference 大概在 10-7左右,从结果说明在定点测试中,FFT HDL Optimized 模块计算误差小。

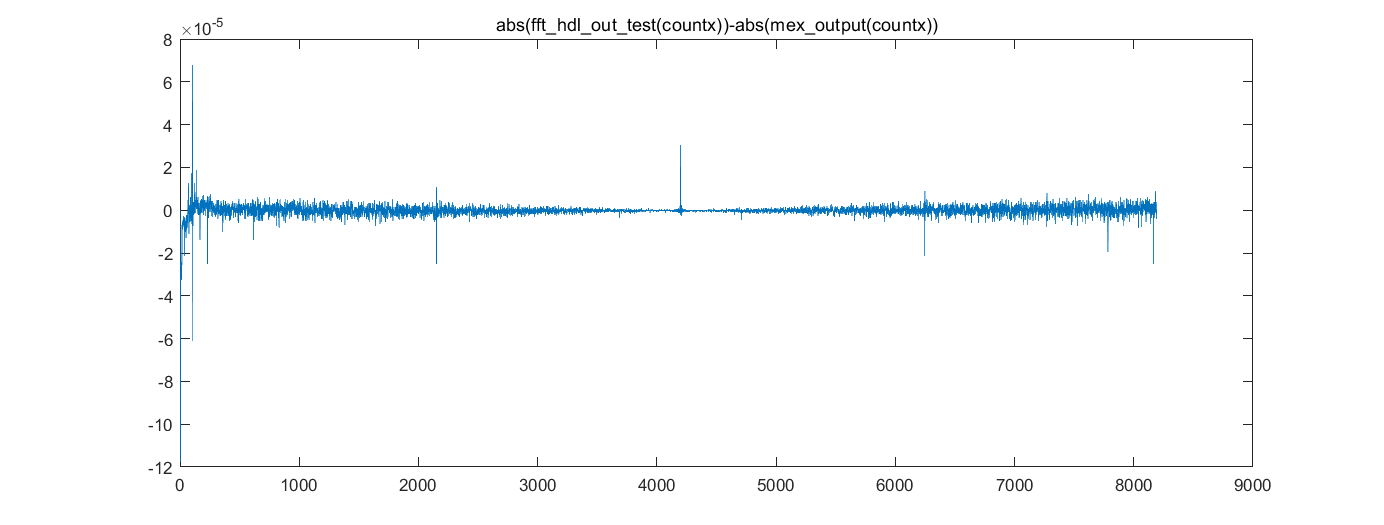

(4)测试五

测试五相比测试一至测试四,最大差别是修改了 FFT HDL Optimized 模块的内部结构即 Streaming Radix 2^2,因为在 Burst Radix 2 结构中,运行时间慢,且在进行第一个 8192 点之后处理之后,后续的 8192 点间隔很大,难以对 FFT HDL Optimized模块与 MEX 进行不同情况下进行测试(两种结构详细区别需看 doc 文档)。在测试五Streaming 情况下,选定了后续三个 8192 点进行测试对比,来说明精度情况。在三轮结果测试中,差值大概均在±2×10-4,diff/reference 大概在 10-5 左右,误差较小。

在三个 8192 的定点测试中,差值大概在±8×10-6,diff/reference 大概在 10-7左右,误差小。

(5)测试六

测试六过程中,Sine 模块直接输出定点 fixdt(1,32,23)数据,MEX 进行定点测试。在测试六 Streaming 情况下,选定了后续三个 8192 点进行测试对比,进一步说明定点精度。定点测试结果中,差值大概在±8×10-6,diff/reference 大概在 10-7 左右,从结果说明在定点测试中,FFT HDL Optimized 模块计算误差小。

(6)测试七

测试七过程中,与测试六相比,改了 FFT HDL Optimized 模块的 data type 模式,即 Rounding Method = Ceiling 模式,Sine 模块直接输出定点 fixdt(1,32,23)数据,MEX 进行定点测试。在测试七 Streaming 情况下,也选定了后续三个 8192 点进行测试对比,来说明 FFT HDL Optimized 模块的不同 data type 模式下的精度区别。定点测试结果中,差值大概在±8×10-6,diff/reference 大概在 10-7 左右,从结果说明在定点测试中, FFT HDL Optimized 模块的不同 data type 模式下的精度区别不大。

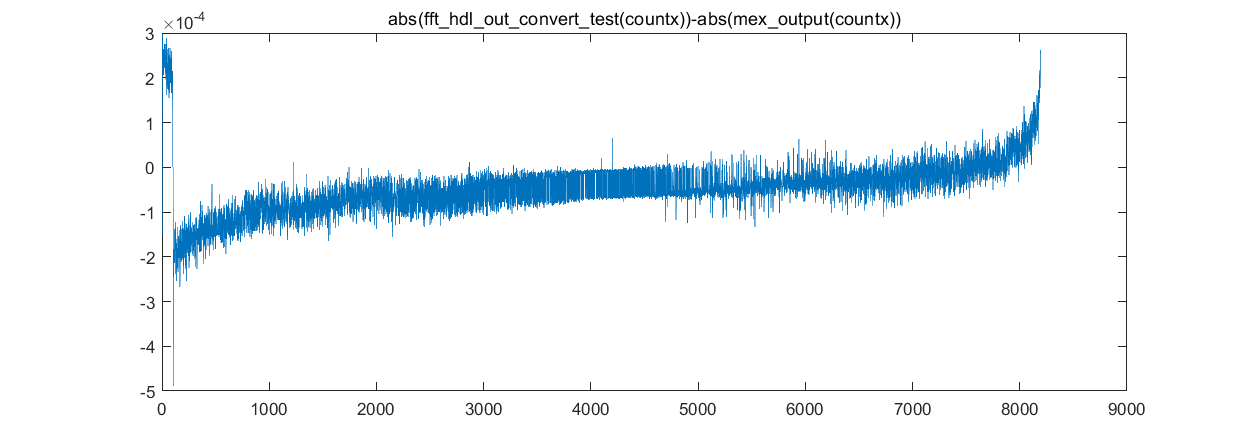

(7)测试八

相比测试五而言,在FFT HDL Optimized模块输出加了定点转浮点convert模块。在测试八Streaming情况下,选定了后续三个8192点进行测试对比,来说明精度情况。在三轮结果测试中,差值大概均在±2×10-4,diff/reference大概在10-5左右,误差较小,与测试五结果基本一致,也说明输出后加的convert定点转浮点模块造成的误差影响较小。

FFT HDL Optimized模块HDL综合代码生成及与Xilinx xfft IP MEX接口精度详细比较的更多相关文章

- HDL代码风格建议(1)使用示例和IP

Recommended HDL Coding Styles HDL coding styles can have a significant effect on the quality of resu ...

- paper:基于verilog HDL 的高速可综合FSM设计

1.寄存器输出型状态机 VS 组合逻辑输出型状态机 2.状态编码方法 这块讲的不好,也比较少. 3.系统设计中模块划分的指导性原则

- 【精选】Nginx模块Lua-Nginx-Module学习笔记(一)Nginx Lua API 接口详解

源码地址:https://github.com/Tinywan/Lua-Nginx-Redis 一.介绍 各种* _by_lua,* _by_lua_block和* _by_lua_file配置指令用 ...

- Spring py登陆模块(包含 记录登陆时间,记录ip,增加积分)

嘛基于最近的复习准备写个关于spring登陆模块的小程序 虽然小但是五脏俱全呐 话不多说让我来介绍一下今天的登陆程序. 这些是 基于Spring JDBC 的持久层实现 基于Spring 声明事物的业 ...

- Nginx模块Lua-Nginx-Module学习笔记(一)Nginx Lua API 接口详解

源码地址:https://github.com/Tinywan/Lua-Nginx-Redis 一.介绍 各种* _by_lua,* _by_lua_block和* _by_lua_file配置指令用 ...

- 第6课:datetime模块、操作数据库、__name__、redis、mock接口

1. datetime模块 import datetime print(datetime.datetime.today()) # 当前时间 2018-01-23 17:22:35.739667 pr ...

- 2020年,最新NGINX的ngx_http_geoip2模块以精准禁止特定国家或者地区IP访问

1.0 geoip2核心识别库 安装geoip2 lib步骤: cd /usr/local/src .tar.gz wget https://github.com/maxmind/libmaxmind ...

- 代码生成java连接数据库的所需代码(超详细)

开始学习: round 1:(一开始学习当然还是要一步一步学习的啦,哪有什么一步登天!!!) a.准备工作:1.eclipse,mysql(这两个软件肯定要的啦,不然学什么把它们连接起来) 2.加载驱 ...

- 使用requests模块进行封装,帮你如何处理restful类型的接口

import requests import urllib3 urllib3.disable_warnings(urllib3.exceptions.InsecureRequestWarning) c ...

随机推荐

- codeforces B. Pasha and String

Pasha got a very beautiful string s for his birthday, the string consists of lowercase Latin letters ...

- c语言中qsort函数的使用、编程中的一些错误

qsort()函数: 功能:相当于c++sort,具有快排的功能,复杂度的话nlog(n)注:C中的qsort()采用的是快排算法,C++的sort()则是改进的快排算法.两者的时间复杂度都是nlog ...

- Jenkins+ant+Jmeter接口自动化框架搭建

工具准备 JDK: jdk1.8.0_111 Ant: apache-ant-1.9.9 Jmeter: apache-jmeter-3.1 Jenkins: jenkins-2.7.4 JDK安装 ...

- 洛谷P1119-灾后重建-floyd算法

洛谷P1119-灾后重建 题目描述 给出\(B\)地区的村庄数NN,村庄编号从\(0\)到\(N-1\),和所有\(M\)条公路的长度,公路是双向的. 给出第\(i\)个村庄重建完成的时间\(t_i\ ...

- OpenStack Train版-6.安装nova计算服务(计算节点)

安装nova计算服务(computel01计算节点 192.168.0.20)安装软件包 yum install centos-release-openstack-train -y yum insta ...

- Maven与Nexus3.x环境构建详解

一.Maven介绍Apache Maven是一个创新的软件项目管理和综合工具.Maven提供了一个基于项目对象模型(POM)文件的新概念来管理项目的构建,可以从一个中心资料片管理项目构建,报告和文件. ...

- 解决debian (Friendly ARM 嵌入式板)的sudo等一部分命令无法TAB补全

TAB对于比较长的命令在使用时是十分方便的,最近就遇到TAB 键无法补全sudo后跟的命令的情况因此去网上取经.在一篇博客中找到解决问题的方法,觉得大牛们写的太精炼然后自己做如下总结方便自已以后解决类 ...

- vue & arrow function error

vue & arrow function error <template> <div class="home"> <img alt=" ...

- Google Developer Profile

Google Developer Profile https://google.dev/u/me https://google.dev/u/109030792841960772125 Google D ...

- website text select notes menu

website text select notes menu website 文字选择笔记菜单(下划线, 标记, 复制, 分享) 下划线, 标记 https://time.geekbang.org/ ...