Verilog中的specify block和timing check

在ASIC设计中,有两种HDL construct来描述delay信息:

1)Distributed delays:通过specify event经过gates和nets的time,来描述delay;

对于net和gate都有三种delay信息: 1)rise delay 2)fall delay 3)transition to high-impedance value

只有一种delay时,所有change都使用这种delay,两个delay值时,才分为rise/fall

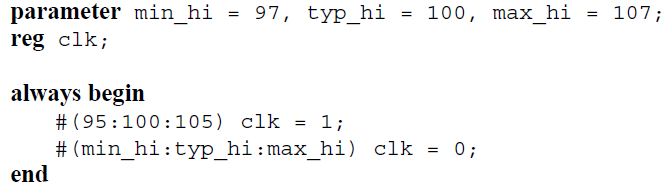

每一种delay信息又分为:min:typical:max三种。

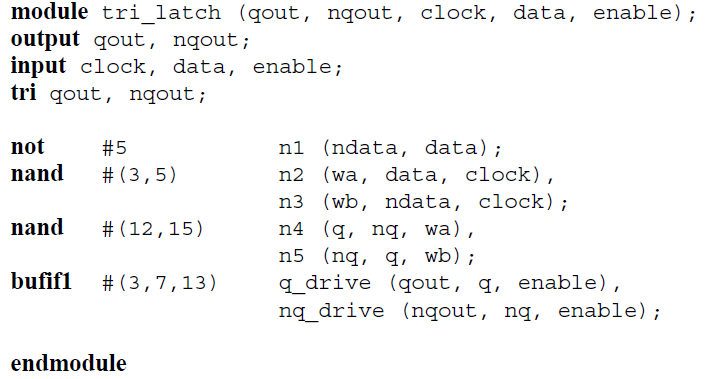

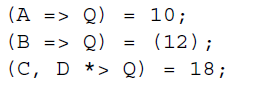

gate和net的model例子:

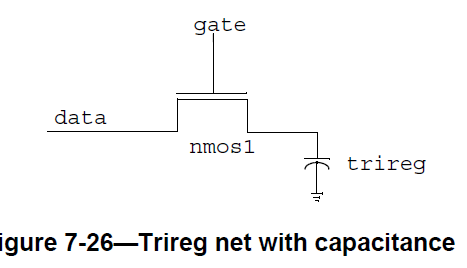

但是trireg类型的变量一般建模cap的信号:第三个delay信息表示他storage的信号值不再保证的时间;

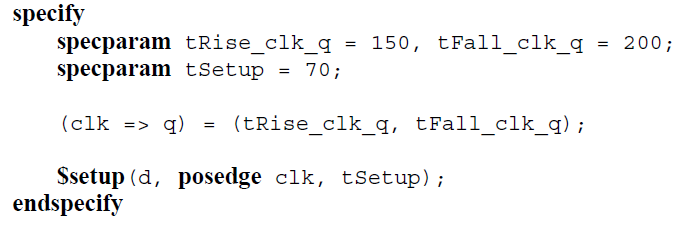

2)Module path delays:通过描述event从source(input/inout port)到destination(output/inout port)的time,来描述delay;

使用specify......endspecify来进行描述。

在specify block中一般有三种信息:

1)various paths across the module;

2)Assign delays to those paths;

3)Perform timing check;

path的declaration包括三类:

1)simple path declaration;

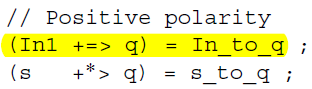

2)edge sensitive path declaration; 加 posedge/negedge

表示FF的有效沿是posedge,从in到out是一个positive的polarity,rise delay是10, fall delay是8。

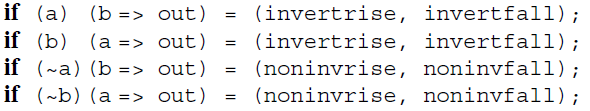

3)state dependent path declaration; 加if/ifnone

4)Edge-sensitive state-dependent paths

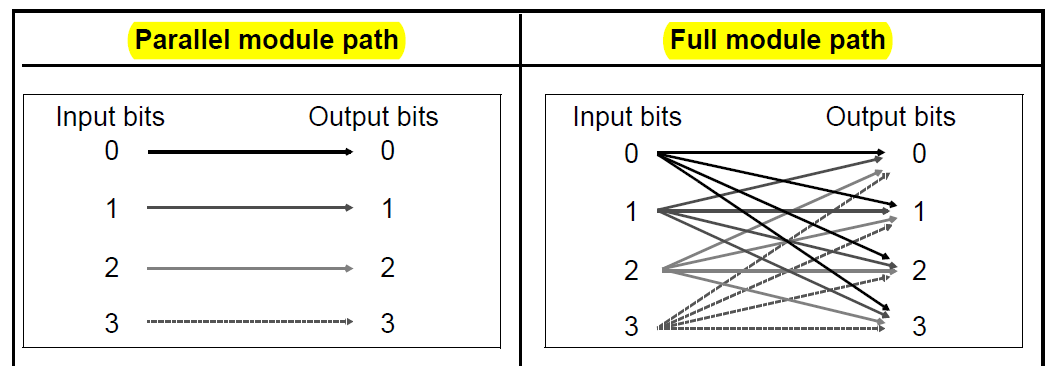

“ *>”表示 full conection, “ =>”表示parallel conection

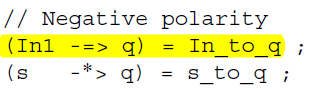

对于会改变polarity的 path,可以通过+/-来进行描述,否则按unknown polarity分析(rise edge可能引起fall edge/rise/edge/no transition)。

"+"表示positive polarity, rise 可能引起rise edge或no transition

"-"表示positive polarity, rise 可能引起fall edge或no transition

Specifying transiiton delay on module path

按rise---fall---to-z的三种来区分,每一种delay信息可以再细分min/typ/max

前三者用","区分,后三者用":"区分

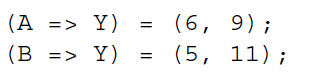

在delay path中,有一些是到同一个output的,这是选择最近有效的一路来计算,如果还是有多条

同时有效,选择delay较小的那一条path。

当Y从0变为1时,如果A transition more recently,那么选择6的delay,否则选择5的delay;

如果A和B都有效,那么选择5的delay;

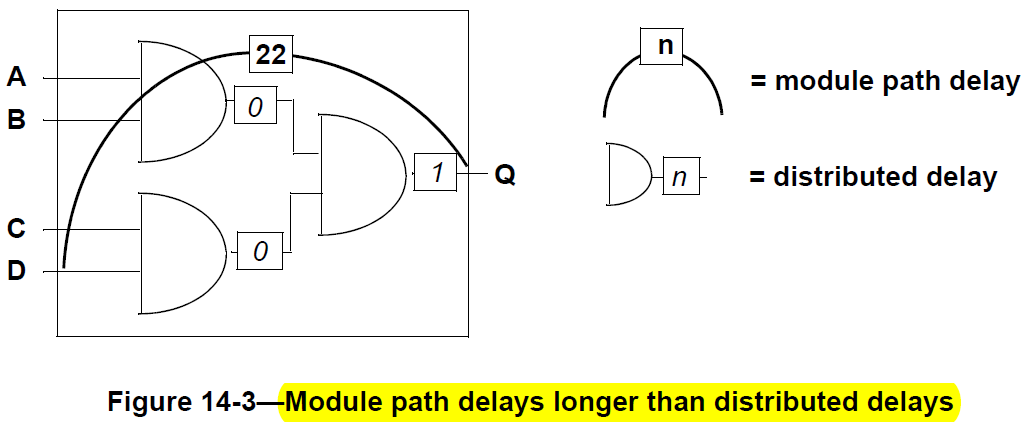

对于module path delay和distributed delay都存在的情况,选择两者之间大的那一个值。

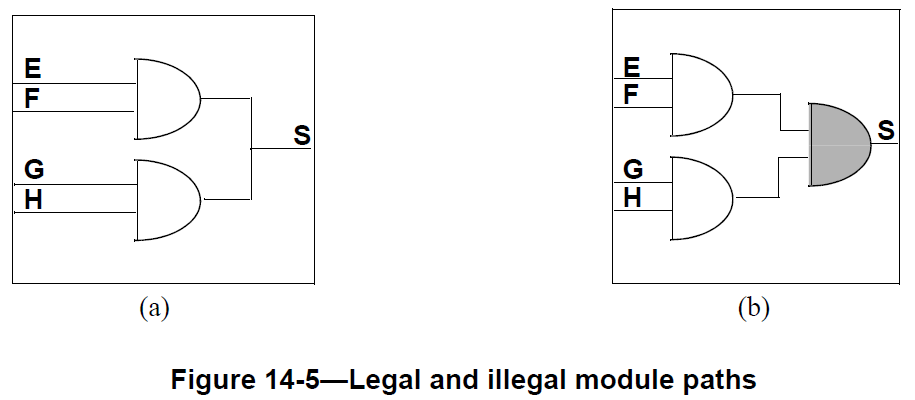

对于path的distination必须是的单一driver的,所以一些wire类型的信号,必须变为gate输出的signal

TIming Check,在给定的timing limit内,保证critical event occur;

可以分为两大类:

1)检查stability time window----------$setup, $hold, $setuphold, $recovery, $removal, $recrem

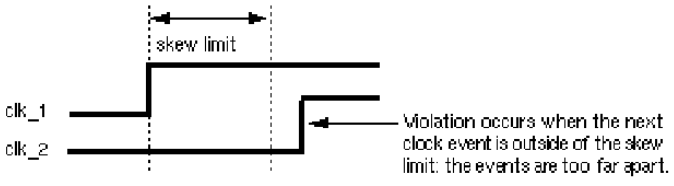

2)检查two event之间的time----------$skew, $width, $period, $nochange

注意这些timing check并不是task,specify内也不允许有task;

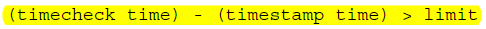

所有的这些timing check都有两个基准时间点:reference event和data event;

两个时间评估点:timestamp event和timecheck event;

不报violation,必须保证data event在正确的time window下发生

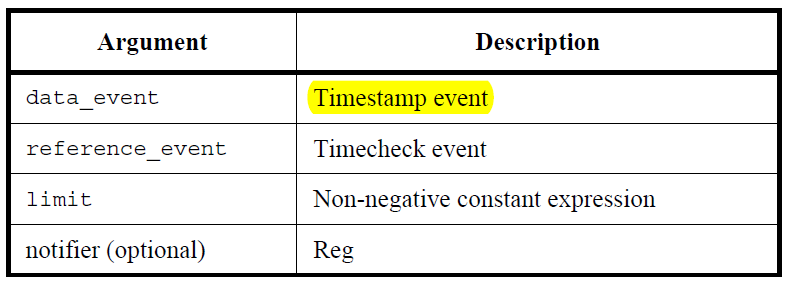

$setup check: $setup(data_event, reference_event, time_check_limit,notifier)

保证timestamp的时间在time window之内,否则会报violation

当limit设置为0时,表示这个检查永远不会报violation

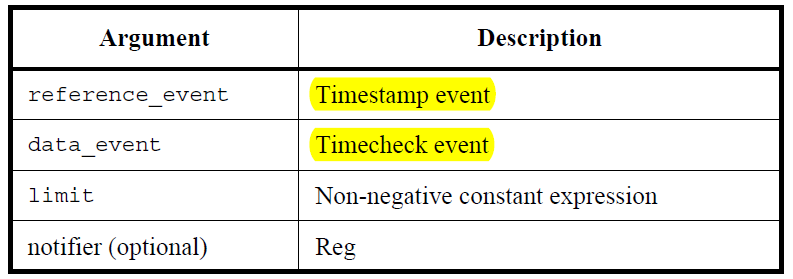

$hold check: $hold(reference_event, data_event, time_check_limit,notifier)

当limit设置为0时,表示这个检查永远不会报violation

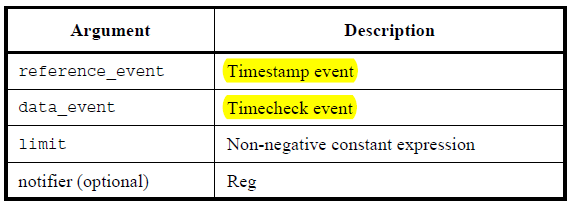

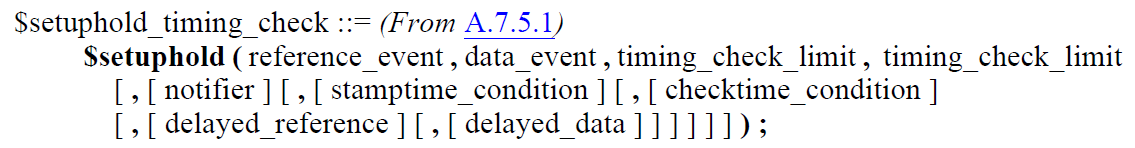

$setuphold check: $setuphold(reference_event, data_event, setup_time_check_limit,hold_time_check_limit,notifier)

$skew(reference_event, data_event, time_check_limit, notifier)

$width(reference_event, time_check_limit, threshold)

reference必须是一个trigger的event,另一个edge作为data event,两者时间间隔大于threshold(防止glitch),小于limit。

$setuphold的完整定义:支持negtive timing

notifier作为一个reg类型变量,在timing check invoke的地方声明,

当检测到timing violation时,notifier通过FF的行为,打印violation信息,并propagate X to the output。

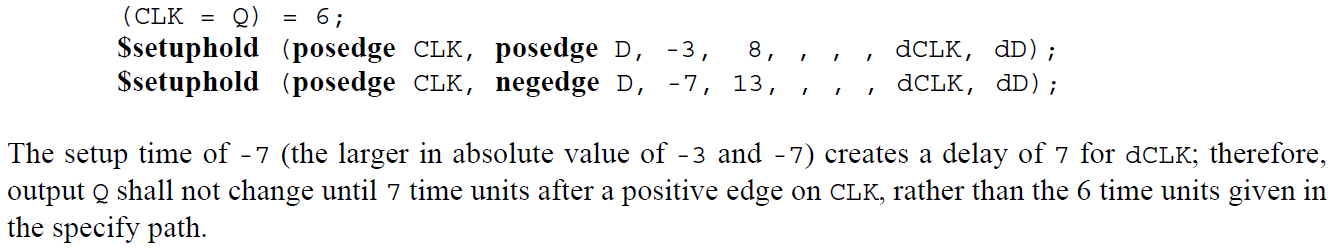

在timing check过程中,data和reference clock的delay copysignal会被创建,

用户可以显式的定义,delayed_reference或者delayed_data。

dclk在setup为负值时,表示clk延时7个cycle,在dclk之前D不再变化,就不会出现violation。

dD在hold为正值时,表示D延时13个cycle,如果dD发生在CLK之后,则不会出现violation。

在多个$setuphold的函数中,选择大的一个赋值。

Verilog中的specify block和timing check的更多相关文章

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- 一段比较有意思的代码——介绍system verilog中的新增幅值语句

system verilog中新加了很多幅值语句,虽然都只适用于阻塞幅值,但是在某些场合中非常实用. 下面是一段有意思的代码,覆盖了一些用法. package definitions; typedef ...

- 关于verilog中if与case语句不完整产生锁存器的问题 分类: FPGA 2014-11-08 17:39 260人阅读 评论(0) 收藏

在很多地方都能看到,verilog中if与case语句必须完整,即if要加上else,case后要加上default语句,以防止锁存器的发生,接下来就来说说其中原因. 一,什么是锁存器?锁存器与触发器 ...

- 关于Verilog 中的for语句的探讨

在C语言中,经常用到for循环语句,但在硬件描述语言中for语句的使用较C语言等软件描述语言有较大的区别. 在Verilog中除了在Testbench(仿真测试激励)中使用for循环语句外,在Test ...

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- 关于Oracle备份中的fractured block

One danger in making online backups is the possibility of inconsistent data within a block. For exam ...

- verilog中always块延时总结

在上一篇博文中 verilog中连续性赋值中的延时中对assign的延时做了讨论,现在对always块中的延时做一个讨论. 观测下面的程序,@0时刻,输入的数据分别是0x13,0x14 . @2时刻, ...

- verilog中读取文件中的字符串_modelsim高级仿真

今天给个程序大家玩玩.因为今天遇到一个问题,就是要向UART发送指令,指令非常多,都是字符串.一直copy 函数 UART ("COMM_1"); UART ("COM ...

随机推荐

- json-lib 之jsonConfig具体应用

一,setCycleDetectionStrategy 防止自包含 public static void testCycleObject() { CycleObject object ...

- ArcGIS API for Silverlight 地图元素点闪烁,线流动显示的处理方式

原文:ArcGIS API for Silverlight 地图元素点闪烁,线流动显示的处理方式 <Grid x:Name="LayoutRoot" Background=& ...

- WebMethod属性详解

WebMethod有6个属性:.Description.EnableSession.MessageName.TransactionOption.CacheDuration.BufferResponse ...

- (leetcode)Reverse Linked List 脑子已经僵住

Reverse a singly linked list. 参考http://www.2cto.com/kf/201110/106607.html 方法1: 讲每个节点的指针指向前面就可以. /** ...

- fdisk 分区

使用fdisk对SD卡进行从新分区.步骤如下: 1. 查看分区情况 ## sudo fdisk -l Disk /dev/sda: 107.4 GB, 107374182400 bytes 255 h ...

- C# base和this

• 是否可以在静态方法中使用base和this,为什么? • base常用于哪些方面?this常用于哪些方面? • 可以base访问基类的一切成员吗? • 如果有三层或者更多继承,那么最下级派生类的b ...

- 在Windows上安装PyCUDA跟Theano

http://www.myexception.cn/cuda/1904274.html

- c3p0参数解释

#最常用配置#initialPoolSize:连接池初始化时创建的连接数,default : 3,取值应在minPoolSize与maxPoolSize之间 c3p0.initialPoolSize= ...

- [CC]CC插件初探

应用程序插件框架的内容包括:主程序App,插件Plugin. 1.实现一个应用程序插架框架关键点有: 一个插件的标准接口,在主程序中存在一个插件的集合.主程序通过循环读取每个插件,将插件对象通过多态的 ...

- git log 常用命令

1.git log 如果不带任何参数,它会列出所有历史记录,最近的排在最上方,显示提交对象的哈希值,作者.提交日期.和提交说明.如果记录过多,则按Page Up.Page Down.↓.↑来控制显示: ...