实验三 组合逻辑电路的VHDL设计

一、实验目的

熟悉QuartusⅡ的VHDL文本设计过程,学习简单组合逻辑电路的设计、仿真和测试方法。

二、实验内容

1. 基本命题

完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤。最后在实验系统上进行硬件测试,验证本项设计的功能。

2. 扩展命题

将设计的2选1多路选择器看成是一个元件mux21a,利用元件例化语句设计能够满足图3-1所示仿真波形的逻辑功能的双2选1多路选择器。

图3-1 仿真波形

三、实验仪器与器材

计算机1台,GW48-PK2S实验箱1台,QuartusⅡ6.0 1套。

四、实验

将实验原理、设计过程、仿真步骤、仿真波形和分析结果、硬件测试实验结果写进实验报告。

2选1多路选择器设计

① 实验原理

由数电知识可知,2选1多路选择器由2个数据输入口(IN0,IN1),1个数据选择端(S1),一个输出口(COUTY)构成。本程序通过判断数据选择端(S1)的取值,将对应的数据输入口(IN0或IN1)输出。

② 程序设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY mux21a IS

PORT ( IN0,IN1,S1:in std_logic;

COUTY : OUT STD_LOGIC);

END mux21a;

ARCHITECTURE behav OF mux21a IS

BEGIN

COUTY<=IN0 when S1='' ELSE IN1;

END behav;

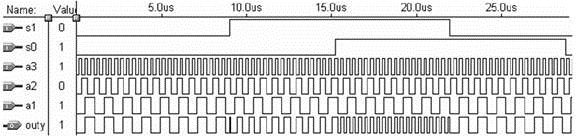

③ mux21a仿真波形图

为了使仿真结果更为直观,我们将IN0设为高电平,IN1设为低电平。

图1 mux21a仿真波形图

由图1可知,我们可知当S1处于高电平时,COUNT输出IN1;反之,输出IN0.所以所设计的实验能够满足要求。

双2选1多路选择器

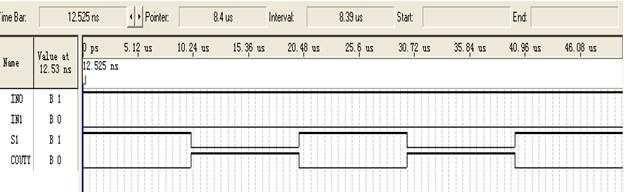

① 实验原理

本实验中直接利用上题的mux21a。由上题可知,mux21a由2个数据输入口(IN0,IN1),1个数据选择端(S1),一个输出口(COUTY)构成。设有两个mux21a,分别为U1和U2。为了充分利用U1和U2的数据选择端,我们将U1的输出口(COUNT)接到U2的输入口IN0,这样U2通过自身的选择端(S1)就可以选择U1的输出或则自己IN0的输入数据,实现2选1选择器到双2选1多路选择器的扩展。(如图2所示)

图2 双二选一多路选择器

② 程序设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY dmux21a IS

PORT ( IN0,IN1,IN2,S0,S1:in STD_LOGIC;

COUTY : OUT STD_LOGIC);

END dmux21a;

ARCHITECTURE BHV OF dmux21a IS

COMPONENT MUX21A

PORT(IN0,IN1,S1:IN STD_LOGIC;

COUTY :OUT STD_LOGIC);

END COMPONENT;

SIGNAL tmp : STD_LOGIC;

BEGIN

u1 : MUX21A PORT MAP(IN0, IN1, S0, tmp);

u2 : MUX21A PORT MAP(IN2, tmp, S1, COUTY);

END BHV;

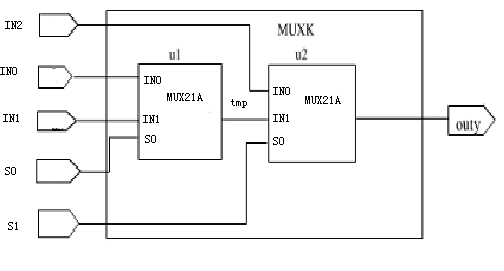

③ dmux21a 仿真波形图

图3dmux21a仿真波形图

图3dmux21a仿真波形图

波形图预测:当S1=0时输出IN2的波形;当S1=1,S0=1,输出IN1的波形;当S1=1,S0=0,输出IN0的波形。

由波形图可知,方针结果与预测结果一致。

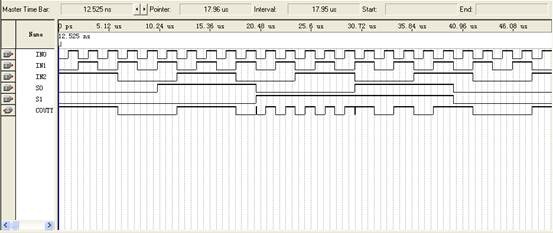

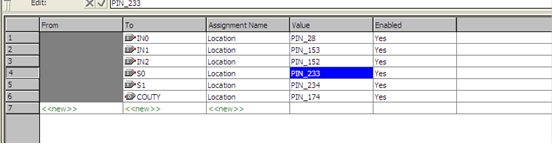

(2)进行本实验引脚锁定时,建议选择实验模式5(No.5),用键1(PIO0)控制端s0;用键2(PIO1)控制端s1;a3、a2、a1分别接clock5、clock0和clock2;输出信号y接扬声器spkert。通过短路帽选择clock0接256Hz信号,clock5接1024kHz信号,clock2接8kHz信号。最后进行编辑、下载和硬件测试实验(通过选择键1、键2、控制s0、s1,可使扬声器输出不同音调)。

表1-1 dmux21a在GWAC6板上目标芯片EP1C6Q240C8的引脚锁定信息

|

端口名称 |

端口符号 |

GWAC6板输入输出元件 |

GWAC6板接口 |

目标器件引脚 |

备注 |

|

控制端s0 |

s0 |

键1 |

PIO0 |

233 |

模式No.5 |

|

控制端s1 |

S1 |

键2 |

PIO1 |

234 |

|

|

输入信号3 |

IN2 |

clock5 |

clock5 |

152 |

|

|

输入信号2 |

IN1 |

Clock0 |

Clock0 |

153 |

|

|

输入信号1 |

IN0 |

Clock2 |

Clock2 |

28 |

|

|

扬声器 |

y |

扬声器 |

SPEAKER |

174 |

如表1所示完成元件dmux21a与实验板引脚的绑定。如图4所示

图4 dmux21a与实验板引脚的绑定

五、实验思考题

比较图形编辑输入与文本编辑输入的主要差别,谈谈例化语句的作用及应用时应注意的问题。

1、比较图形编辑输入与文本编辑输入的主要差别

使用图形编辑法的话,我们需要对逻辑运算与硬件结构对应起来,也就是要懂得将逻辑运算转化成硬件电路,这需要有较为扎实的硬件功底。使用文本编辑输入的话,我们只需要懂得用VHDL表达逻辑运算,而不必关心硬件电路的组成,这可以减轻很多硬件设计方面的功夫(接线,选用元器件等)。

2、例化语句的作用及应用时应注意的问题

1) 例化语句的作用是:引入另一个已经设计好的组件。

2) 应用时应注意的问题:

① 要记得将原先已经设计好的原件放在工程底下。对于本体来说是mux21a。

② 要将引入的元件与顶级元件的引脚一一匹配,有需要的话,使用信号(SINGAL)进行消息的传递。

实验三 组合逻辑电路的VHDL设计的更多相关文章

- 实验四 时序逻辑电路的VHDL设计

一.实验目的 熟悉QuartusⅡ的VHDL文本设计过程,学习简单时序逻辑电路的设计.仿真和测试方法. 二.实验 1. 基本命题 用VHDL文本设计触发器,触发器的类型可任选一种.给出程序设计.仿真分 ...

- 实验五 含有控制信号的计数器VHDL设计

一.实验目的 学习计数器的设计.仿真和硬件测试,进一步熟悉VHDL设计技术. 二.实验仪器与器材 计算机1台,GW48-PK2S实验箱1台,QuartusⅡ6.0 1套. 三.实验 1. 基本命题 在 ...

- 【VHDL】组合逻辑电路和时序逻辑电路的区别

简单的说,组合电路,没有时钟:时序电路,有时钟. ↓ 也就是说,组合逻辑电路没有记忆功能,而时序电路具有记忆功能. ↓ 在VHDL语言中,不完整条件语句对他们二者的影响分别是什么?组合逻辑中可能生成锁 ...

- 20145206《Java程序设计》实验三实验报告

20145206<Java程序设计>实验三实验报告 实验内容 XP基础 XP核心实践 相关工具 实验步骤 (一)敏捷开发与XP 软件工程是把系统的.有序的.可量化的方法应用到软件的开发.运 ...

- Verilog-FPGA硬件电路设计之一——if语句优先级(always块中的阻塞赋值生成的组合逻辑电路是按照顺利执行的)

出处:http://bbs.ednchina.com/BLOG_ARTICLE_3013262.HTM 综合软件:Quartus II 一.有优先级的if语句 if..else if.. else i ...

- FPGA学习笔记(五)—— 组合逻辑电路功能的描述

设计方法: 分析真值表规律 两种描述方式: 方式1:用assign描述,用阻塞赋值= 方式2:用always@(*)描述,用非阻塞赋值<= 选择功能的三种描述方式: ...

- 2017-2018-2 20155228 《网络对抗技术》 实验三:MAL_免杀原理与实践

2017-2018-2 20155228 <网络对抗技术> 实验三:MAL_免杀原理与实践 实验内容 正确使用msf编码器,msfvenom生成如jar之类的其他文件,veil-evasi ...

- 20155324 《Java程序设计》实验三 敏捷开发与XP实践

20155324 <Java程序设计>实验三 敏捷开发与XP实践 实验内容 XP基础 1.XP核心实践 2.相关工具 实验步骤 敏捷开发与XP 1.敏捷开发(Agile Developme ...

- 2017-2018-2 20165306 实验三《敏捷开发与XP实践》实验报告

实验三<敏捷开发与XP实践>实验报告 实验报告封面 实验内容 XP基础 XP核心实践 相关工具 实验步骤 (一) 敏捷开发与XP实践-1 实验要求: 参考 代码规范 安装alibaba 插 ...

随机推荐

- 关于Log和adb知识

1,打印日志:adb logcat -v time >log 2,清除以上日志:adb logcat -c 2,查看设备是否连接电脑:adb devices 3,登陆手机设备:adb shell ...

- jquery ajax load

jQuery load() 方法 jQuery load() 方法是简单但强大的 AJAX 方法. load() 方法从服务器加载数据,并把返回的数据放入被选元素中. 语法: $(selector). ...

- Python 集合方法总结

1.添加一个元素: add(...) Addan element to a set. 1 2 3 4 >>> a = {'shaw',11,22} >>>a. ...

- VC++ WINDOWS自定义消息范围

WINDOWS自定义消息WM_USER和WM_APP WM_USER常量是Windows帮助应用程序定义私有窗口类里的私有消息,通常使用WM_USER+一个整数值,但总值不能超过0x7FFF(十进制: ...

- shell讲解-小案例

shell讲解-小案例 一.文件拷贝输出检查 下面测试文件拷贝是否正常,如果cp命令并没有拷贝文件myfile到myfile.bak,则打印错误信息.注意错误信息中basename $0打印脚本名.如 ...

- MFC 实现字符串的移动

在视类添加一个WM_KeyDown,然后实现函数写上 switch(nChar) {.. CRect rc; GetClientRect(&rc); int nWidth = rc.Wid ...

- Windows下使用性能监视器监控SqlServer的常见指标

这篇文章主要介绍了Windows下使用性能监视器监控SqlServer的常见指标,常见指标包括Buffer Cache Hit Ratio.Pages/sec. Available Bytes.Dis ...

- frame和bounds的区别与联系

首先先看一下下面两个属性的代码实现: -(CGRect)frame{ return CGRectMake(self.frame.origin.x,self.frame.origin.y,self.fr ...

- C++矩阵运算库armadillo配置笔记

前言 最近在用C++实现神经网络模型,优化算法需要用到矩阵操作,一开始我用的是boost的ublas库,但用着用着感觉很不习惯,接口不够友好.于是上网搜索矩阵运算哪家强,大神们都推荐armadillo ...

- BHP编译器教程

BHP编译器教程 BHP是一个WEB模版编程语言编译器,生成PHP后端代码. 最简单的Helloworld例子 编写一个hello.bhp文件 <? $hello="hello,wor ...