Verilog笔记.3.有限状态机

有限状态机

有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态

所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究竟转向

哪一状态还是留在原状态不但取决于各个输入值,还取决于当前所在状态。(这里指的是米里Mealy型有限状态

机,而莫尔Moore型有限状态机究竟转向哪一状态只决于当前状态。)

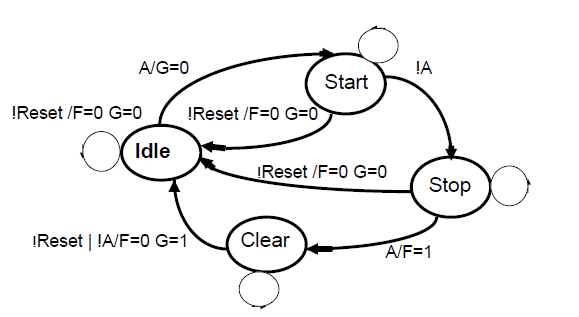

例

采用独热码实现的有限状态机。采用了独热编码后有了多余的状态,就有一些不可到达的状态,为此在CASE语句的最后需要增加default分支项,以确保多余状态能回到Idle状态。

module fsm (Clock, Reset, A, F, G);

input Clock, Reset, A;

output F,G;

reg F,G;

reg [:] state ;

parameter Idle = ’b1000,

Start = ’b0100,

Stop = ’b0010,

Clear = ’b0001;

always @(posedge clock)

if (!Reset)

begin

state <= Idle; F<=; G<=;

end

else

case (state)

Idle: begin

if (A) begin

state <= Start;

G<=;

end

else state <= Idle;

end

Start: if (!A) state <= Stop;

else state <= Start;

Stop: begin

if (A) begin

state <= Clear;

F <= ;

end

else state <= Stop;

end

Clear: begin

if (!A) begin

state <=Idle;

F<=; G<=;

end

else state <= Clear;

end

default: state <=Idle;

endcase

endmodule

用always语句和连续赋值语句把状态机的触发器部分和组合逻辑部分分成两部分来描述。

module fsm (Clock, Reset, A, F, G);

input Clock, Reset, A;

output F,G; reg [:] state ;

wire [:] Nextstate;

parameter Idle = ’b00,

Start = ’b01,

Stop = ’b10,

Clear = ’b11; always @(posedge Clock)

begin

if (!Reset)

begin

state <= Idle;

end

else

state <= Nextstate;

end assign Nextstate = ( state == Idle ) ? ( A ? Start : Idle ) :

( state==Start ) ? ( !A ? Stop : Start ) :

( state== Stop ) ? ( A ? Clear : Stop ) :

( state== Clear) ? ( !A ? Idle : Clear) :

Idle;

assign F = (( state == Stop) && A );

assign G = (( state == Clear) && (!A || !Reset)); endmodule

用沿触发的always语句和电平敏感的always语句把状态机的触发器部分和组合逻辑部分分成两部分来描述。

module fsm (Clock, Reset, A, F, G);

input Clock, Reset, A;

output F,G; reg [:] state, Nextstate;

parameter Idle = ’b00,

Start = ’b01,

Stop = ’b10,

Clear = ’b11; always @(posedge Clock)

begin

if (!Reset)

begin

state <= Idle;

end

else

state <= Nextstate;

end always @( state or A )

begin

F=;

G=;

if (state == Idle)

begin

if (A)

Nextstate = Start;

else

Nextstate = Idle;

G=;

end

else

if (state == Start)

if (!A)

Nextstate = Stop;

else

Nextstate = Start;

else

if (state == Stop)

if (A)

Nextstate = Clear;

else

Nextstate = Stop;

else

if (state == Clear)

begin

if (!A)

Nextstate = Idle;

else

Nextstate = Clear;

F=;

end

else

Nextstate= Idle;

end

end

endmodule

状态必须明确赋值,通常使用参数(parameters)或宏定义(define)语句加上赋值语句来实现。

原则 1:时序电路建模时,用非阻塞赋值。

原则 2:锁存器电路建模时,用非阻塞赋值。

原则 3:用always 块写组合逻辑时,采用阻塞赋值。

原则 4:在同一个always 块中同时建立时序和组合逻辑电路时,用非阻塞赋值。

原则 5:在同一个always 块中不要同时使用非阻塞赋值和阻塞赋值。

原则 6:不要在多个always 块中为同一个变量赋值。

Verilog笔记.3.有限状态机的更多相关文章

- Verilog笔记——Verilog数字系统设计(第二版)夏宇闻

本片记录Verilog学习笔记,主要是和以往用的C语言的不同之处,以例子.代码的形式记录.学习以<Verilog数字系统设计>(第二版)为参考资料,援助作者夏宇闻. 1. C语言和Veri ...

- Verilog笔记.2.数字逻辑电路

1.数字逻辑电路的种类:1) 组合逻辑:输出只是当前输入逻辑电平的函数(有延时),与电路的原始状态无关的逻辑电路.也就是说,当输入信号中的任何一个发生变化时,输出都有可能会根据其变化而变化,但与电路目 ...

- Verilog笔记.1.基本语法

0.前 抽象模型分级: • 系统级(system):用高级语言结构实现设计模块的外部性能的模型.• 算法级(algorithm):用高级语言结构实现设计算法的模型.• RTL级(Register Tr ...

- [笔记][FPGA]有限状态机FSM学习笔记(三)

0. 简介 在数电FPGA中,FSM是一个重要的部分,藉此可以完成一些复杂算法的硬件实现等.其中有关于FSM的写法按照always块的个数来划分,又分为一段式.两段式.三段式状态机.顾名思义,一段式就 ...

- 自学FPGA笔记之 “有限状态机”

“有限状态机”,一份好的代码必需掌握的技能. 首先状态机需要分清楚一共有多少种状态,其次画出状态图,状态图根据需求来画,尽可能的细分画到每一个状态,如有需要用到状态机一定要画出状态图,一定要画出状态图 ...

- Verilog笔记——YUV2RGB的模块测试

1 YUV2RGB的模块如下: module yuv2rgb( clk, //时钟输入 rstn, //复位输入,低电平复位 y_in, //变换前Y分量输出 cb_in, //变换前Cb分量输出 c ...

- Verilog笔记.三段式状态机

之前都是用的一段式状态机,逻辑与输出混在一起,复杂点的就比较吃力了. 所以就开始着手三段式状态机. 组合逻辑与时序逻辑分开,这样就能简单许多了. 但是两者在思考方式上也有着很大的区别. 三段式,分作: ...

- Verilog笔记.6.FIFO

FIFO,First In First Out ,是一种先进先出的数据缓存器. 没有外部读写地址线,只能顺序写入数据,顺序的读出数据, 其数据地址由内部读写指针自动加1完成. 不能像普通存储器那样可以 ...

- Verilog笔记.5.同步、异步

在数字电路中经常有同步synchronism.异步asynchronism的概念.异步指输入信号和时钟无关:同步指输入信号和时钟信号有关,实际上就是输入信号和时钟信号进行了与运算或者与非运算.实际开发 ...

随机推荐

- linux学习笔记4

查看当前系统还有哪些用户 who 字符计数 wc -l(line) 可以统计有多少行 -w(word) 可以统计有多少个单词 -c(character) 可以统计有多少个字符 切个字符 - 排序 l ...

- ssh & sftp & MacOS

ssh & sftp & MacOS https://www.technoduet.com/a-simple-way-to-connect-to-remote-ftp-sever-on ...

- Shell Script的默认变量

$? #上一个命令执行后所回传的值,当我们执行某些命令时,这些命令都会回传一个执行后的代码.一般来说,如果成功执行该命令则会回传一个0值.如果执行过程发生错误,就会回传“错误代码” $$ #代表目前这 ...

- bzoj1853-大包子的幸运数字

题意 称只含有 6 和 8 的数字为幸运数字.称幸运数字的倍数为类幸运数字.求 \([l,r]\) 中有多少个类幸运数字.\(1\le l,r\le 10^{10}\) . 分析 幸运数字最多有 \( ...

- noip模拟题《迷》enc

[问题背景]zhx 和他的妹子聊天.[问题描述] 考虑一种简单的加密算法. 假定所有句子都由小写英文字母构成, 对于每一个字母, 我们将它唯一地映射到另一个字母.例如考虑映射规则:a- ...

- [BZOJ3223]文艺平衡树 无旋Treap

3223: Tyvj 1729 文艺平衡树 Time Limit: 10 Sec Memory Limit: 128 MB Description 您需要写一种数据结构(可参考题目标题),来维护一个 ...

- 关于qt中的tr()函数

关于qt中的tr()函数 在论坛中漂,经常遇到有人遇到tr相关的问题.用tr的有两类人: (1)因为发现中文老出问题,然后搜索,发现很多人用tr,于是他也开始用tr (2)另一类人,确实是出于国际化的 ...

- Tajo--一个分布式数据仓库系统(分布式环境安装试用)

前面两篇介绍了一下tajo,下面就说一下安装和使用吧. 一.分布式安装 前提:hadoop2中的hdfs和yarn已经安装并运行正常. 1.下载source并build源码 $git clone ht ...

- Alpha 冲刺 —— 十分之一

队名 火箭少男100 组长博客 林燊大哥 作业博客 Alpha 冲鸭! 成员冲刺阶段情况 林燊(组长) 过去两天完成了哪些任务 协调各成员之间的工作,对多个目标检测及文字识别模型进行评估.实验,选取较 ...

- dfs序七个经典问题(转)

我这个人不怎么喜欢写轻重链剖分和LCT 还是喜欢dfs序.括号序列之类的 毕竟线段树好写多了 然后就有了这篇转载的文章 写在这边以后有时间看看 原文链接:https://www.cnblogs.com ...