Training JTAG Interface

For most embedded CPU architecture implementations, the JTAG port is used by the debugger to interface the chip for debugging one or more cores.

The normal user will probably not need to know details of the JTAG implementation unless there is a need

to debug several daisy-chained JTAG TAP controllers or to access special test functions or configurations

via JTAG that are not implemented in the debugger software.

JTAG is the name used for the IEEE 1149.1 standard entitled Standard Test Access Port

and Boundary-Scan Architecture for test access ports (TAP) used for testing printed circuit boards (PCB) using boundary scan.

JTAG is the acronym for Joint Test Action Group, the name of the group of people that developed the IEEE 1149.1 standard.

The functionality usually offered by JTAG is Debug Access and Boundary Scan:

Debug Access is used by debugger tools to access the internals of a chip making its resources and functionality available and modifiable,

e.g. registers, memories and the system state.

Boundary Scan is used by hardware test tools to test the physical connection of a device,

e.g. on a PCB.

Although the TAP (Test Access Port) access itself is generic for all architectures, the functionality implemented behind JTAG is different for each device.

The following chapter explains all necessities for accessing a JTAG TAP. For a complete description of JTAG see the IEEE 1149.1 standard.

JTAG is defined as a serial communication protocol and a state machine accessible via a TAP.

The DTAB (Debug and Test Access Block) is implemented on the target chip as a “passive” device that never sends data without request.

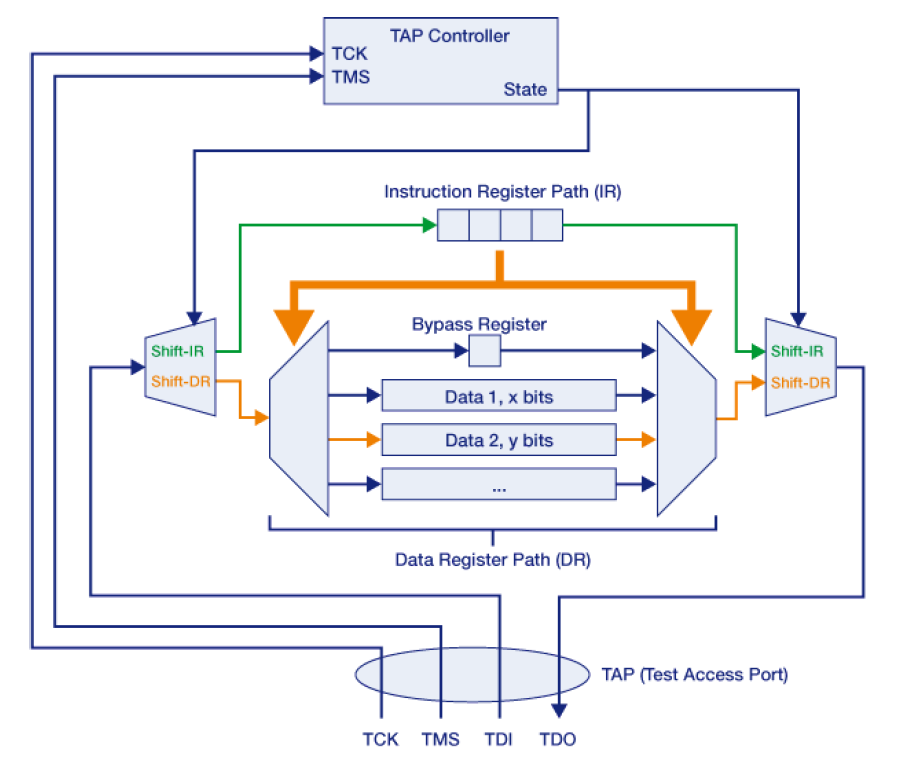

The DTAB mainly consists of the following

The TAP (Test Access Port) with its physical connections (signals) to the external world.

The TAP Controller (a 16-state state machine).

One IR (Instruction Register) and several DRs (Data Registers).

The Debug Bus for communication with the on-chip debug logic.

The TAP defines the interface between the DTAB and the debug tool.

The JTAG Port is the physical connector on the PCB where the debug cable is plugged.

The IEEE standard defines the following TAP signals,

used for the serial communication and driving the TAP controller (JTAG state machine):

The TMS and TDI line are sampled by the DTAP on each rising edge on the TCK line.

The TDO line changes its value after a falling edge on the TCK line.

Instruction and Data Registers

The functionality of the DTAB is accessible via different instructions stuffed into the Instruction Register.

By loading an instruction, the corresponding Data Register is selected for access,

providing and/or accepting data according to the selected instruction.

Only a few instructions are defined by the IEEE standard, and only a few of them are mandatory,

the BYPASS instruction (mandatory) for use in daisy-chained multi-core configurations

IDCODE instruction (not mandatory) for identifying a device

Unused instruction codes can be freely implemented by the device manufacturer.

The width of the IR is not specified by the JTAG standard but needs to be the same for all instructions of a specific device.

Since the DR is selected according to the loaded instruction the DR width is variable.

The following schematic shows the connection of the input signals

with the DTAB and the selection of the Data Register depending on the content of the Instruction Register:

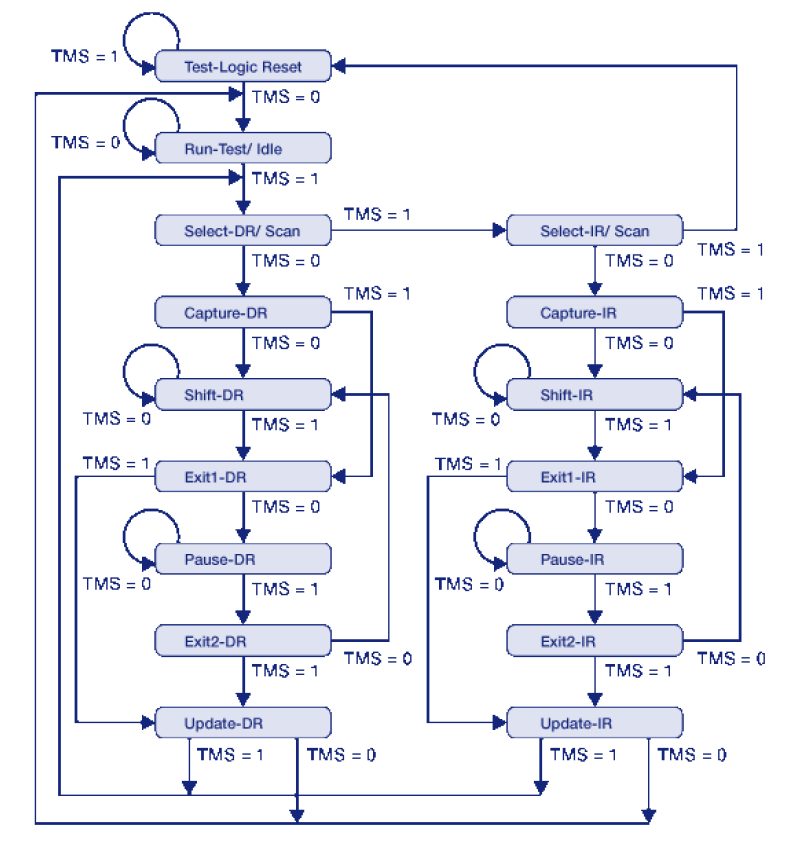

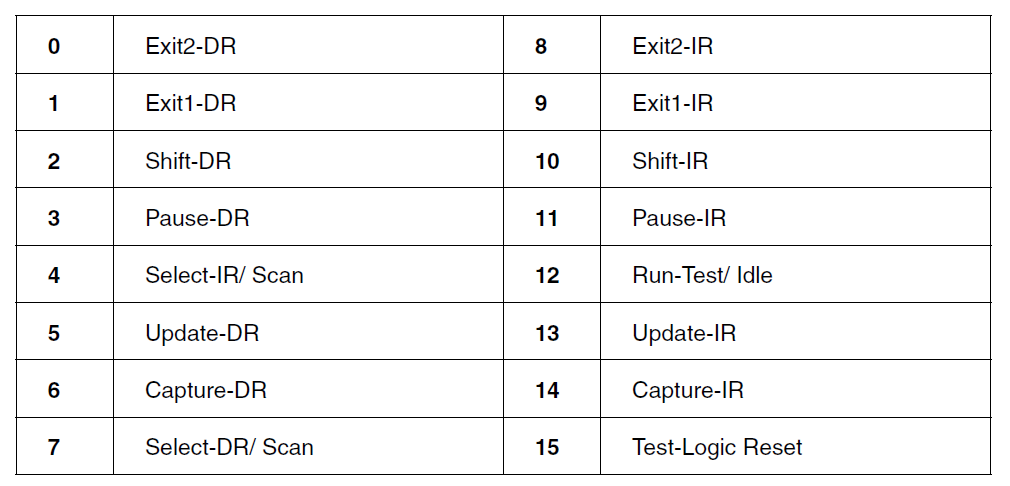

The IEEE standard defines a 16-state state machine called the TAP controller to control several actions:

Each state of the TAP controller can be reached by a sequence of bits transmitted via the TMS line depending on the current state.

Normally a DR or IR shift access starts from the pause parking position,

changes to one of the shift states where data is transmitted and ends up in the pause parking position again.

Pause parking position: state the TAP controller holds while waiting for the next shift operation.

The following states of the TAP controller are of importance:

Test Logic Reset

sets the Instruction Register to its reset value (IDCODE or BYPASS).

This state can be reached from any other state by shifting five times “1” on TMS.

Some CPUs do also reset the DTAB and/or the on-chip debug logic when this state is entered.

As a result an active debug connection might get lost, if this state is driven by a PRACTICE script or a custom application.

Run-Test/ Idle and Select DR-Scan are used by most debuggers as pause parking position.

In the Shift-IR state the debug tool shifts an instruction into the Instruction Register.

The instruction is activated once the TAP controller reaches the Update-IR state.

In the Shift-DR state the debug tool shifts data to/from the Data Register selected by the currently loaded instruction.

The debug tool communicates with the DTAB by reading and/or writing IRs and DRs.

The debug tool first drives the TAP Controller to the Shift-IR state to write the appropriate instruction to IR.

Then it drives to the Shift-DR state where the DR can be read or written.

Once the Update-DR state is reached, the processing of DR is started, e.g. the data contained in DR is forwarded to the on-chip debug system.

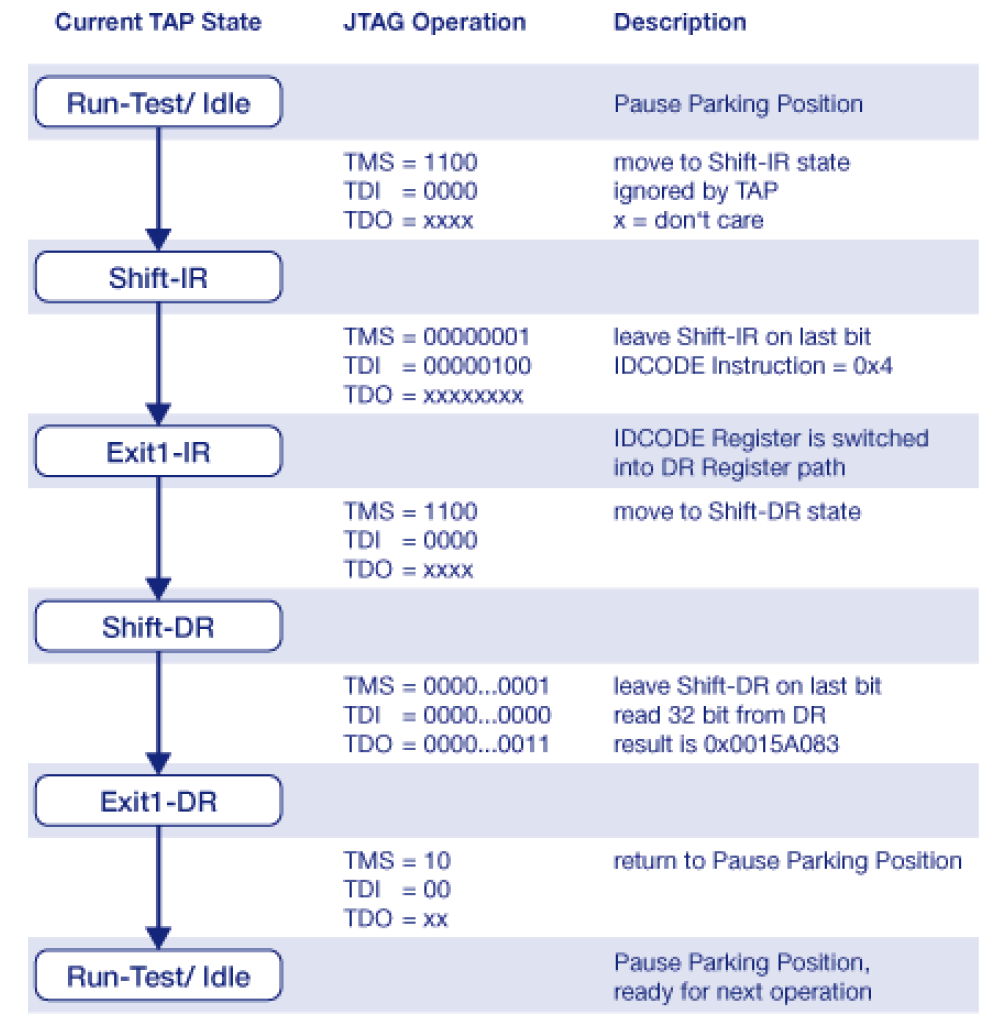

The following example shows how the chip ID code is read on a TriCore processor

(IR: 8 bits, IDCODE DR: 32 bits)

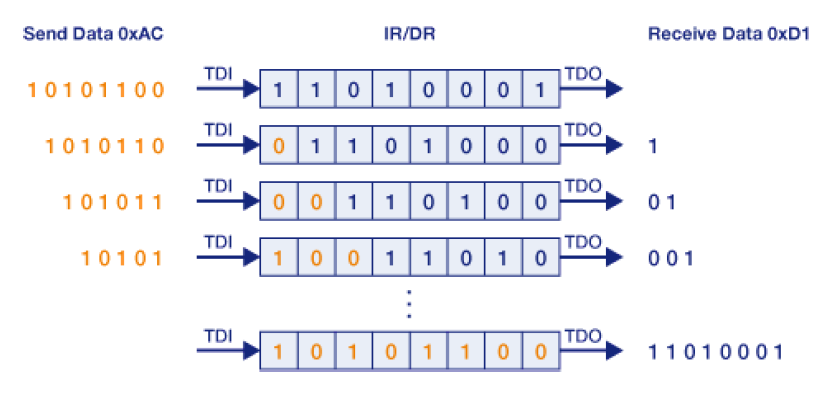

Reading or writing the IR or DR is performed bitwise from LSB to MSB. With every bit shifted into the TAP controller via TDI,

the contents of DR is rightshifted one bit, providing the LSB on TDO.

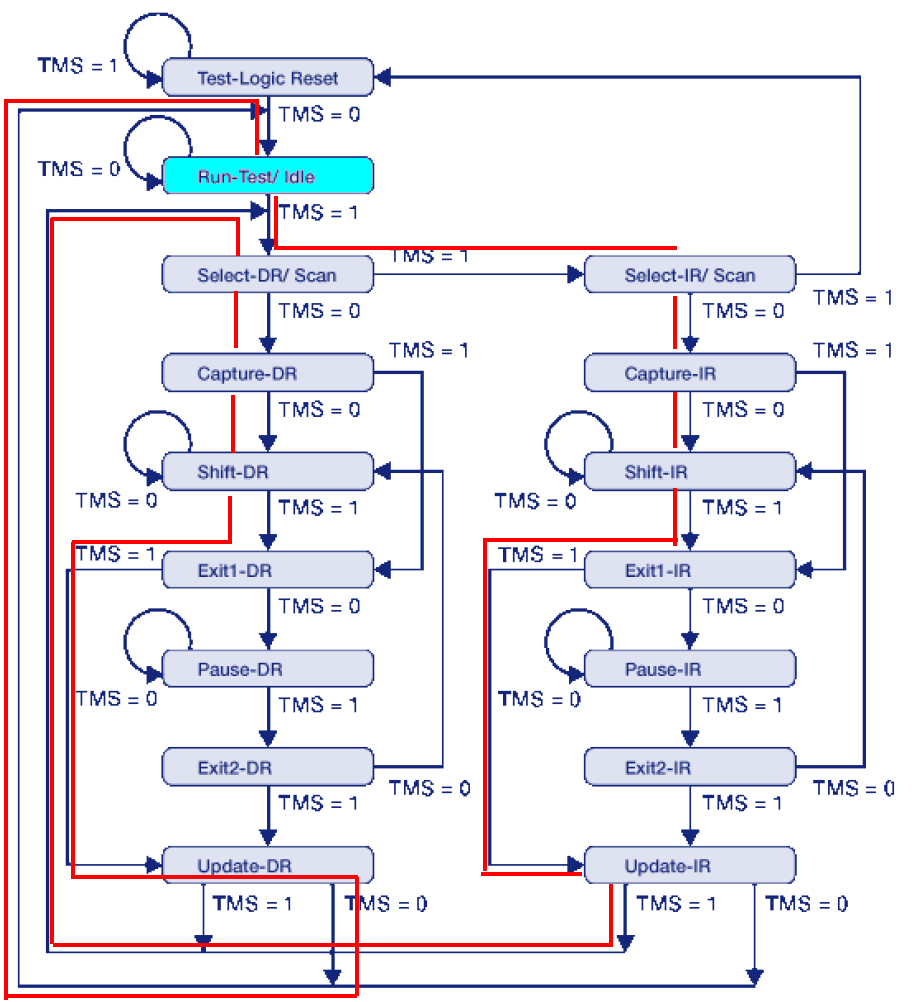

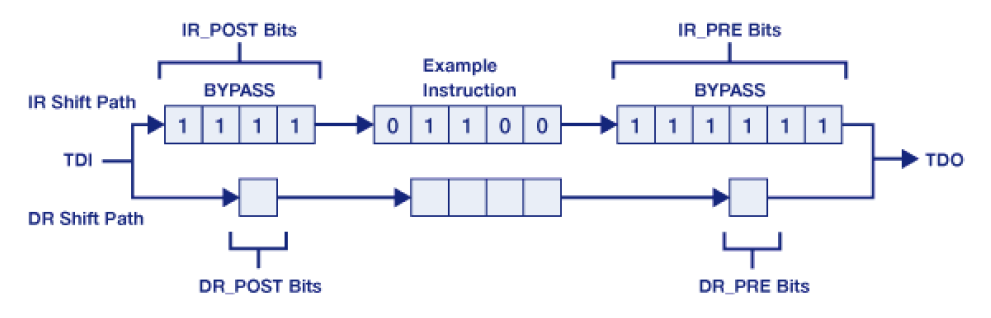

Shifting in a Daisy-chained Multi-TAP Solution

The TAP controllers of all DTABs are synchronized.

So when transmitting data in Shift-IR and Shift-DR states this means that the Instruction- and Data Registers are chained, too.

Communication with all DTABs simultaneously is not possible

since the connected debuggers all have different tasks to do and so have an individual communication with their core.

Instead only one debugger at a time communicates with one single DTAB,

by loading the Instruction Registers of all other DTABs with the BYPASS instruction (“ignore” mode).

Loading the BYPASS instruction into the Instruction Register will switch the Bypass Register into the Data Register path:

• The JTAG standard defines the BYPASS instruction to consist of “1”s only.

In case the width of the Instruction Register (IR-width) is 4 bit, the JTAG instruction is 0xf,

in case IR-width is 7 bit, the BYPASS instruction is 0x7f.

• The Bypass Register must be a 1-bit register and is preloaded with “0” in the Capture-DR state.

So depending on the position of the DTAB to be addressed,

the Instruction-/Data-Registers of the other DTABs have to be filled with BYPASS instructions, respectively “bypass” bits.

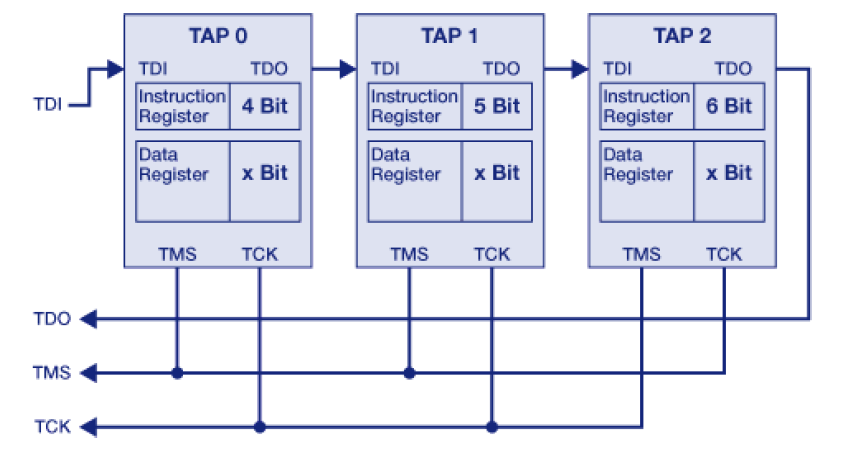

On the following pages an example chip is used, which provides a chain of three DTABs (one TAP each):

The picture below shows the Instruction/Data Registers if TAP1 is accessed.

Remember that shifting is performed from LSB to MSB, so in case of an IR shift,

the BYPASS instruction(s) of the TAP(s) after the addressed TAP are shifted in first.

Accordingly these bits are called IR_PRE bits.

The BYPASS instructions of the TAP(s) before are shifted in last so these bits are called IR_POST.

The same applies to the DR path with DR_PRE and DR_POST.

On embedded designs with several TAPs the signals can be chained on board level, so only one common debug connector is required.

This saves space and costs. In case the TAPs are already connected on-chip this also saves pins.

In case a single debugger hardware handles access to all cores under debug,

advanced debug features such as the synchronous multi-core start can be implemented more performant.

The tool must be able to address its core within the TAP chain (multi-TAP capable),

and it must be able to share the JTAG port with other tools.

Because all IRs need to be accessed for shifting instructions,

the complete TAP chain can only be as fast as the slowest TAP thus reducing performance of faster TAPs.

This is especially the case in designs with a return clock (RTCK), e.g. DTABs from ARM.

The connection of the JTAG signals as well as the on-board or on-chip routing must be handled with care to avoid electrical interference,

e.g. by interference of reflections at the end of branch lines.

For handling a multi-TAP system, needs to know only few details about the chain:

• IR_POST is the sum of the IR-width of all TAPs between the TDI pin of the debug connector and the addressed TAP.

• IR_PRE is the sum of the IR-width of all TAPs between the addressed TAP and the TDO pin of the debug connector.

• DR_POST usually is the sum of the bypass registers of all TAPs between the TDI pin of the debug connector and the addressed TAP.

• DR_PRE usually is the sum of the bypass registers of all TAPs between the addressed TAP and the TDO pin of the debug connector.

• TAP State is the neutral parking position where a host instance hands over control of the JTAG chain to another host instance or another debug tool.

The following code are available for the neutral parking position:

Training JTAG Interface的更多相关文章

- HappyJTAG2 - JTAG AND SPI AVR8 interface EMBEDDED JTAG ! EMBEDDED SPI !

New version released ! V2.45 (Check version list for details) This construction is based on HappyJTA ...

- ST40 自制 JTAG 适配器

// 文章首发于 https://zhuanlan.zhihu.com/p/28762429 // 但是不知道为什么搜索引擎还没有收录,便在博客再次发布. 0. 引言 意法半导体生产的 SH4 架构的 ...

- JTAG 引脚自动识别 JTAG Finder, JTAG Pinout Tool, JTAG Pin Finder, JTAG pinout detector, JTAGULATOR, Easy-JTAG, JTAG Enumeration

JTAG Finder Figuring out the JTAG Pinouts on a Device is usually the most time-consuming and frustra ...

- ARM JTAG 信号 RTCK 应该如何处理?

用户在调试内嵌可综合内核的 CPU 如 ARM7TDMI-S 时,需要通过打开仿真器的自适应时钟功能. 此时,ARM仿真器根据 RTCK 时钟信号的频率,产生可用于 CPU 内核当前时钟主频的最快的 ...

- Serial Wire Debug (SWD) Interface -- PSoc5

PSoC 5 supports programming through the serial wire debug (SWD) interface. There are two signals in ...

- JTAG Simplified

JTAG Simplified So the other day, I explored the JTAG bus interface which is frequently found in CPL ...

- JTAG – A technical overview and Timing

This document provides you with interesting background information about the technology that underpi ...

- Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors

Implementation of Serial Wire JTAG flash programming in ARM Cortex M3 Processors The goal of the pro ...

- Turtelizer 2 provide JTAG Flash programming and debugging of ARM based boards via USB

http://www.ethernut.de/en/hardware/turtelizer/ Introducing Turtelizer 2 Overview Turtelizer 2 had be ...

随机推荐

- 浅谈区间DP的解题时常见思路

一.区间DP解题时常见思路 如果题目中答案满足: 大的区间的答案可以由小的区间答案组合或加减得到 大的范围可以由小的范围代表 数据范围较小 我们这时可以考虑采用区间DP来解决. 那么常见的解法有两种: ...

- 内存对齐与ANSI C中struct型数据的内存布局 【转】

转自:http://blog.chinaunix.net/uid-25909619-id-3032209.html 当在C中定义了一个结构类型时,它的大小是否等于各字段(field)大小之和?编译器将 ...

- 为你详细解读HTTP请求头的具体含意

当我们打开一个网页时,浏览器要向网站服务器发送一个HTTP请求头,然后网站服务器根据HTTP请求头的内容生成当次请求的内容发送给浏览器.你明白HTTP请求头的具体含意吗?下面一条条的为你详细解读,先看 ...

- MCS-51 单片机的中断系统

MCS-51 单片机的中断系统 MCS-51中断系统:5个中断源(两个外部中断, 两个定时器, 一个串口),2个优先级 中断相关概念 中断:当CPU正在处理某件事情时,单片机外部或内部发生的某一紧急事 ...

- mapreduce的组件介绍

第一部分:重要的组件 Combiner •什么是Combiner •combine函数把一个map函数产生的<key,value>对(多个key, value)合并成一个新的<key ...

- 【linux】sed -e 's/-//g'

sed是用来处理文本的 s/正则表达式/替换字符串/ :表示将正则表达式的内容替换为后面的字符串 g :表示替换全部,即如果不加g,则只会替换第一个 -e :多点编辑(这个没懂) 例 ...

- Laravel 的 JSON API 接口自动化测试

Laravel 自带了两种测试类型 Feature Test: 功能测试.针对类似接口这种流程性的测试. Unit Test: 单元测试.针对单个函数这种输入输出结果的测试. 新建一个 Feature ...

- Java编程的逻辑 (27) - 剖析包装类 (中)

本系列文章经补充和完善,已修订整理成书<Java编程的逻辑>,由机械工业出版社华章分社出版,于2018年1月上市热销,读者好评如潮!各大网店和书店有售,欢迎购买,京东自营链接:http: ...

- prometheus如何使用blackbox-exporter来获取k8s的网络性能

如果学会了如何抓取app的metrics,则blackbox-exporter抓取网络性能套路是相同的. 一,在blackbox-exporter的blackbox.yml里配置好抓取模块,常见的是h ...

- 11 个最佳 jQuery 模拟滚动条插件 scrollbar

1. Windows:全屏窗口滚动插件 该插件可以很好地实现全屏滚动,每滚动一次即为一屏.比如,用户浏览下一屏幕内容时,只需手动滚动到某一位置,该插件会自动滚动显示下一屏全部内容.对于浏览类似于PP ...