FPGA中的时序分析(一)

谈及此部分,多多少少有一定的难度,笔者写下这篇文章,差不多是在学习FPGA一年之后的成果,尽管当时也是看过类似的文章,但是都没有引起笔者注意,笔者现在再对此知识进行梳理,也发现了有很多不少的收获。笔者根据网上现有的资源,作进一步的总结,希望能够有所帮助。

一个不错的网站,类似于一个手册,随时可以去查询如何去定义各个时序约束指令怎么用。http://quartushelp.altera.com/current/mergedProjects/tafs/tafs/tcl_pkg_sdc_ver_1.5.htm

静态时序分析(STA,static timing analysis),对于STA的理解,可以想象在FPGA的内部好比一块PCB,FPGA的逻辑阵列好比PCB板上的一些分立元器件,PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通,PCB上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过内部逻辑门传输也有一定的延时,PCB信号走线也有延时,FPGA信号走线也有延时,这就带来了一系列的问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理之后从FPGA的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输延时的不一致,不仅会影响FPGA本身会给FPGA之外的电路或者系统带来诸多的问题。

所以针对上面的一系列问题,设计者需要提出一些特定的时序要求,针对现有的电路给出时序约束,

分析时序,本质上是节点对节点之间的时序分析,如果没有节点,时序也就无从谈起。在FPGA中,我们可以把节点当作是寄存器与寄存器之间的时序分析,寄存器与寄存器之间可能还有一些组合逻辑充斥着。所以时序路径通常有四大类:

(1)寄存器到寄存器类型,即reg2reg;

(2)输入引脚到寄存器类型,即pin2reg;

(3)寄存器到输出引脚类型,即reg2pin;

(4)输入引脚到输出引脚类型,即pin2pin;

针对上述四种基本时序路径,最关心的就是数据信号和时钟锁存沿之间的建立时间和保持时间的关系。

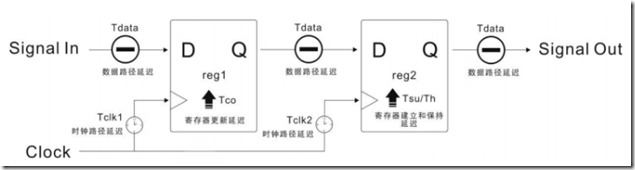

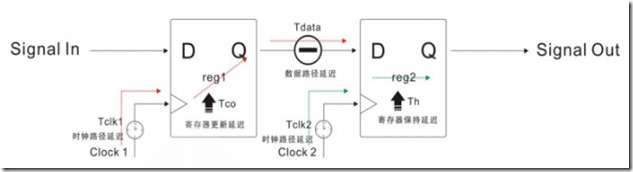

对于四种延时路径可以用图1所示,对于signal in,是外部IC到FPGA的输入信号引脚,一般情况下芯片手册都会给出各引脚关于时序方面的说明,如Tco、TSU、Th、等信息,这个是在分析时序时会用到。Reg1到reg2之间的时序路径是相当于在FPGA内部的寄存器到寄存器之间的延时路径,signal out是相当于FPGA的输出信号到外部IC之间的引脚信息。

图1 时序路径分析

这里只分析FPGA内部的时序路径,外部IC的时序路径需要结合具体的IC数据手册,然后结合FPGA输入引脚部分的大概延时进行推测一个值,之后具体再分析。

所以从寄存器1到寄存器2之间的延迟时间的分析。

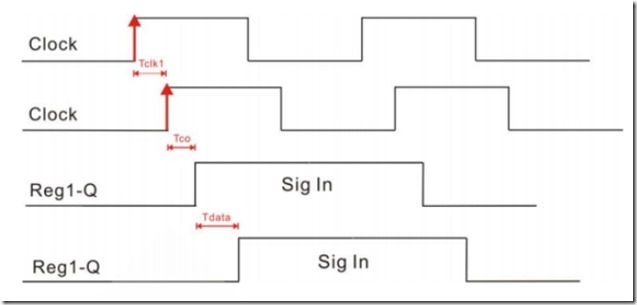

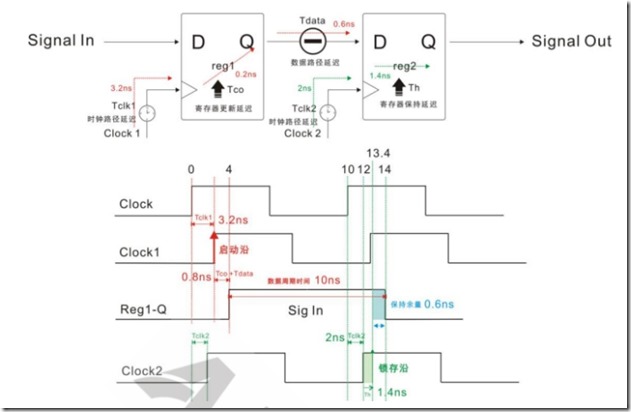

图16.2 寄存器到寄存器延时

上图是考虑各种延迟之后的从输入数据到输出数据的时间延迟。

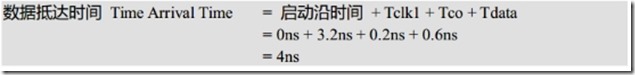

所以我们引入第一个概念:数据抵达时间(官方视频上面的概念),也就是实际到达时间,

, 而启动沿时间往往是按0处理,只考虑后三者。

, 而启动沿时间往往是按0处理,只考虑后三者。

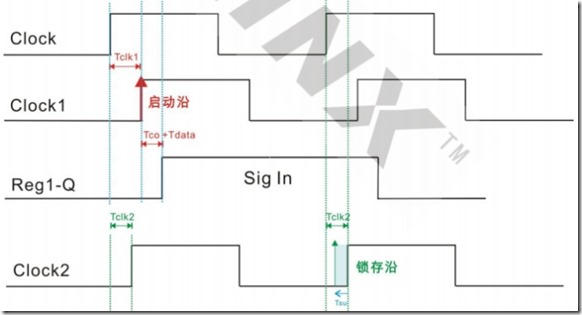

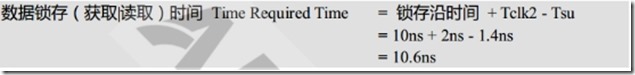

引入第二个概念:数据要求时间

图16.3 数据要求时间分析

由于有寄存器建立时间的参与,所以会使得数据锁存时间由下面的公式决定,但是在应用时Tsu按照负值代入公式,这样计算的才正确,可能是官方的bug,所以按照负值计算即可。

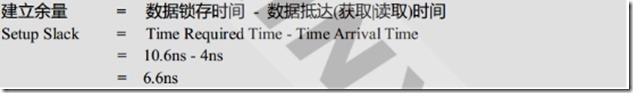

建立余量

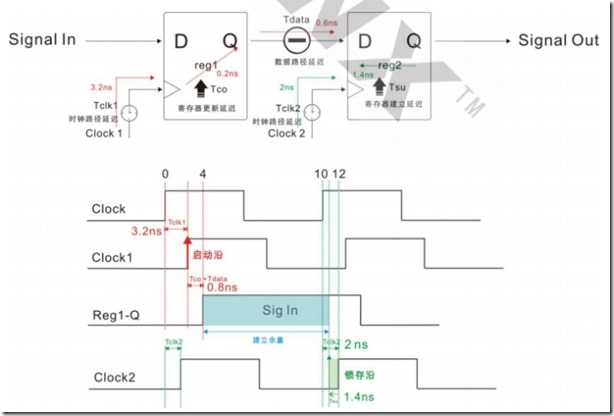

为了说明怎么计算得到建立余量,特举例如下所示。

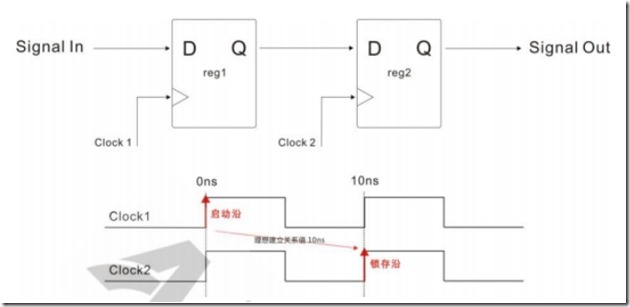

对于公式上面的锁存沿时间,其实就是启动沿和锁存沿之间的差值,也就是建立时间关系,建立时间关系是理想状态下,启动沿与锁存沿之间的距离,如下图2所示,这个建立时间关系 = 时钟周期,所以在计算的时候,可以先计算出建立时间关系值,然后也就确定了锁存沿时间。

图2 建立时间和时钟周期的关系

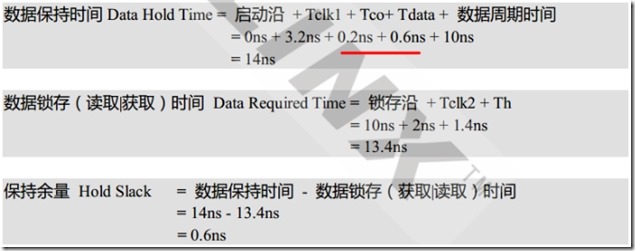

保持余量

还是用我们的经典的图来说明保持余量,那么数据从寄存器1到寄存器2要经过的时间为

其中数据周期时间,是以时钟周期为计算值。

根据上图,用一些数字来计算,如下图

由此得到了保持余量值。

//=======================================================================

更多详细的资料下载可以登录笔者百度网盘:

网址:http://pan.baidu.com/s/1bnwLaqF

密码:fgtb

//=======================================================================

FPGA中的时序分析(一)的更多相关文章

- FPGA中的时序分析(四)

常用约束语句说明 关于Fmax 上述是实现Fmax的计算公式,clock skew delay的计算如下图, 就是两个时钟的差值.到头来,影响Fmax的值的大小就是组合逻辑,而Fmax是针对 ...

- FPGA中的时序分析(五)

时序约束实例详解 本篇博客结合之前的内容,然后实打实的做一个约束实例,通过本实例读者应该会实用timequest去分析相关的实例.本实例以VGA实验为基础,介绍如何去做时序约束. 首先VGA这种情况属 ...

- FPGA中的时序分析(三)

验证公式正确性 前两篇博客提及了关于时序的建立余量和保持余量的计算.结合实际情况,验证公式的运算正确性.结合之前博客提及的LED实验,看一下建立余量和保持余量是否都合格. 建立余量 图1是最大时钟 ...

- FPGA中的时序分析(二)

使用Timequest 笔者对Altera较熟悉,这里以quartus ii中的timequest作为讲解. Timequest分析时序的核心,也就是在于延迟因数的计算.那么建立约束文件,去告诉tim ...

- 【转】关于FPGA中建立时间和保持时间的探讨

时钟是整个电路最重要.最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错:因而明确FPGA设计中决定系统时钟的因素,尽 ...

- 【转载】FPGA 中的latch 锁存器

以下这篇文章讲述了锁存器的一些概念和注意事项.原文标题及链接: FPGA 中的latch 锁存器 - 快乐至永远上的博客 - 与非博客 - 与网 http://www.eefocus.com/liuy ...

- 巧用FPGA中资源

随着FPGA的广泛应用,所含的资源也越来越丰富,从基本的逻辑单元.DSP资源和RAM块,甚至CPU硬核都能集成在一块芯片中.在做FPGA设计时,如果针对FPGA中资源进行HDL代码编写,对设计的资源利 ...

- FPGA中的delay与latency

delay和latency都有延迟的意义,在FPGA中二者又有具体的区别. latency出现在时序逻辑电路中,表示数据从输入到输出有效经过的时间,通常以时钟周期为单位. delay出现在组合逻辑电路 ...

- FPGA中的INOUT接口和高阻态

除了输入输出端口,FPGA中还有另一种端口叫做inout端口.如果需要进行全双工通信,是需要两条信道的,也就是说需要使用两个FPGA管脚和外部器件连接.但是,有时候半双工通信就能满足我们的要求,理论上 ...

随机推荐

- FullWebBrowserCookie 取得WebBrowser的完整Cookie

using System; using System.ComponentModel; using System.Net; using System.Runtime.InteropServices; u ...

- 【Unity】3.5 导入音频文件

分类:Unity.C#.VS2015 创建日期:2016-04-05 一.简介 音频文件 (Audio File) 资源的选择原则应该以无故障地流畅运行为宗旨.下面列出了常用的音频文件. .AIFF ...

- 深入理解Linux内核-访问文件

文件的访问模式:1.规范模式:2.同步模式:3.内存映射模式:4.直接I\O模式5.异步模式: 内存映射模式:1.共享型:在线性区页上的任何写操作都会修改磁盘上的文件:而且这种修改对映射了同一文件的所 ...

- npm WARN build `npm build` called with no arguments. Did you mean to `npm run-script build`?

跑npm build结果如下: npm WARN build `npm build` called with no arguments. Did you mean to `npm run-script ...

- SQL server 存储过程实现统计赋值

@EmptyCount int output 参数 declare @strCount nvarchar(max); 声明变量 取值语句: set @strCount='select @Count= ...

- 李洪强iOS开发之静态库的打包一

李洪强iOS开发之静态库的打包一 //静态库一般做一下几种事情 //1 工具类 算法逻辑 新建工具类LHQTools 定义类方法 + (NSInteger)sumWithNum1: (NSIntege ...

- 【Ubuntu】查看GPU状态

watch -n 10 nvidia-smi TensorFlow指定GPU CUDA_DEVICE_ORDER="PCI_BUS_ID" CUDA_VISIBLE_DEVICES ...

- 设计模式之单一职责原则(iOS开发,代码用Objective-C展示)

单一职责原则:就一个类而言,应该只有一个引起它变化的原因. 在iOS开发中,我们会很自然的给一个类添加各种各样的功能,比如随便写一个简单的应用程序,一般都会生成一个viewController类,于是 ...

- Spring事务管理要点总结

# Spring事务管理要点总结 ### 要点---- 事务是企业级应用中必不可缺少的技术,用来确保数据的完整性和一致性.- Spring事务管理并不实现事务管理的实现,而是借助Hibernate\J ...

- TCP、UDP数据包大小的限制

版权声明:本文为灿哥哥http://blog.csdn.net/caoshangpa 原创文章,转载请标明出处. https://blog.csdn.net/caoshangpa/article/de ...