FPGA开平方的实现

3种方法:

1.JPL近似的实现方法

`timescale 1ns / 1ps

module complex_abs#(parameter N=)(

clk,

syn_rst,

dataa,

datab,

ampout); input clk;

input [N-:] dataa;

input [N-:] datab;

input syn_rst;

output reg [N-:]ampout; reg [N-:]dataa_reg ;

reg [N-:]datab_reg ;

wire [N-:]dataa_abs ;

wire [N-:]datab_abs ;

reg [N-:]dataabs_max,dataabs_min ;

reg [N-:]absmin_3 ; always @(posedge clk)

begin

if(syn_rst == 'b1)

begin

dataa_reg <= 'd0 ;

datab_reg <= 'd0 ;

end

else

begin

dataa_reg <= dataa ;

datab_reg <= datab ;

end

end assign dataa_abs = (dataa_reg[] == 'b1) ? (31'd0-dataa_reg[N-:]) : dataa_reg[N-:] ;

assign datab_abs = (datab_reg[] == 'b1) ? (31'd0-datab_reg[N-:]) : datab_reg[N-:] ; always @(posedge clk)

begin

if(dataa_abs > datab_abs)

begin

dataabs_max <= dataa_abs ;

dataabs_min <= datab_abs ;

absmin_3 <= {'b0,datab_abs}+{datab_abs,1'b0} ;

end

else

begin

dataabs_max <= datab_abs ;

dataabs_min <= dataa_abs ;

absmin_3 <= {'b0,dataa_abs}+{dataa_abs,1'b0} ;

end

end always @(posedge clk)

begin

if(absmin_3 > {'b0,dataabs_max})

ampout <= {'b0,dataabs_max} - {4'b0,dataabs_max[N-:]} + {'b0,dataabs_min[N-2:1]} ;

else

ampout <= {'b0,dataabs_max} + {4'b0,dataabs_min[N-:]} ;

end endmodule

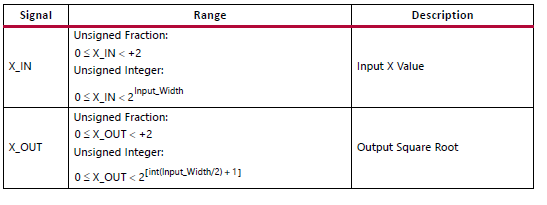

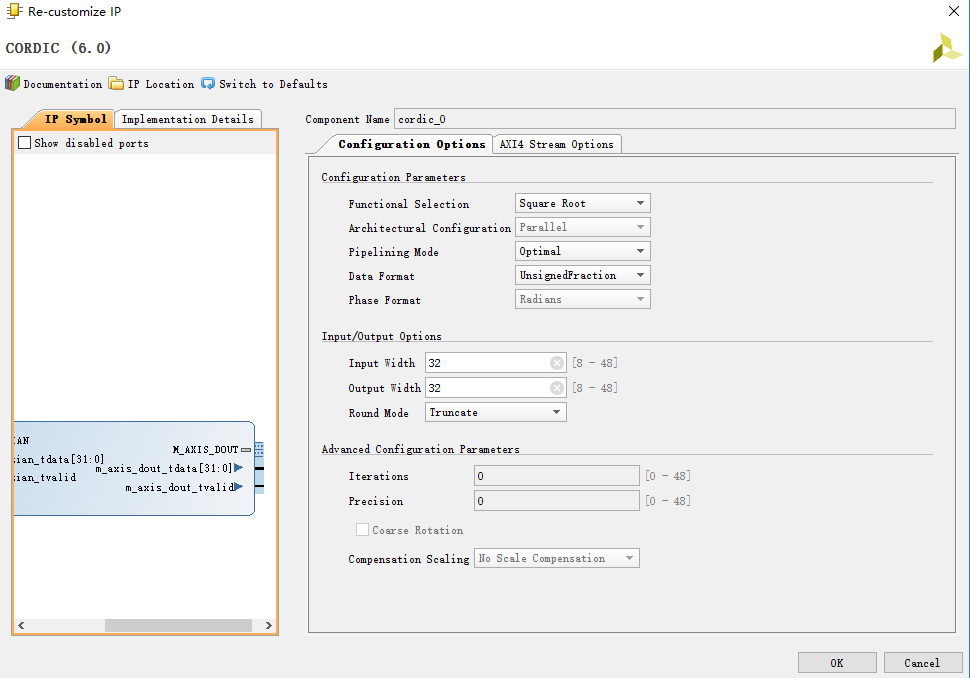

2.调用IP模块的cordic算法实现效果

可选模式可以是fraction或者intergalactic

工程中输入数据的范围是远大于2的,于是我们可以采用实现方法是将所有的数据先归一化成-2~2之间,然后再进一步的采用cordic模块

IP的配置如下

3.牛顿迭代忽略余数的实现方法

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/08/07 16:26:46

// Design Name:

// Module Name: sqrt

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module sqrt

#(

parameter d_width = ,

parameter q_width = d_width/ - ,

parameter r_width = q_width + )

(

input wire clk,

input wire rst,

input wire i_vaild,

input wire [d_width-:] data_i,//data_21,data_12,data_22, //输入 output reg o_vaild,

output reg [q_width:] data_o, //输出

output reg [r_width:] data_r //余数

); //-------------------------------------------------------------------------------- reg [d_width-:] D [r_width:]; //被开方数

reg [q_width:] Q_z [r_width:]; //临时

reg [q_width:] Q_q [r_width:]; //确认

reg ivalid_t [r_width:];

//--------------------------------------------------------------------------------

always@(posedge clk or posedge rst)

begin

if(rst)

begin

D[r_width] <= ;

Q_z[r_width] <= ;

Q_q[r_width] <= ;

ivalid_t[r_width] <= ;

end

else if(i_vaild)

begin

D[r_width] <= data_i;//data_11+data_21+data_12+data_22; //被开方数据

Q_z[r_width] <= {'b1,{q_width{1'b0}}}; //实验值设置

Q_q[r_width] <= ; //实际计算结果

ivalid_t[r_width] <= ;

end

else

begin

D[r_width] <= ;

Q_z[r_width] <= ;

Q_q[r_width] <= ;

ivalid_t[r_width] <= ;

end

end

//------------------------------------------------------------------------------- // 迭代计算过程 //-------------------------------------------------------------------------------

generate

genvar i;

for(i=r_width-;i>=;i=i-)

begin:U

always@(posedge clk or posedge rst)

begin

if(rst)

begin

D[i] <= ;

Q_z[i] <= ;

Q_q[i] <= ;

ivalid_t[i] <= ;

end

else if(ivalid_t[i+])

begin

if(Q_z[i+]*Q_z[i+] > D[i+])

begin

Q_z[i] <= {Q_q[i+][q_width:i],'b1,{{i-1}{1'b0}}};

Q_q[i] <= Q_q[i+];

end

else

begin

Q_z[i] <= {Q_z[i+][q_width:i],'b1,{{i-1}{1'b0}}};

Q_q[i] <= Q_z[i+];

end

D[i] <= D[i+];

ivalid_t[i] <= ;

end

else

begin

ivalid_t[i] <= ;

D[i] <= ;

Q_q[i] <= ;

Q_z[i] <= ;

end

end

end

endgenerate

//-------------------------------------------------------------------------------- // 计算余数与最终平方根 //--------------------------------------------------------------------------------

always@(posedge clk or posedge rst)

begin

if(rst)

begin

data_o <= ;

data_r <= ;

o_vaild <= ;

end

else if(ivalid_t[])

begin

if(Q_z[]*Q_z[] > D[])

begin

data_o <= Q_q[];

data_r <= D[] - Q_q[]*Q_q[];

o_vaild <= ;

end

else

begin

data_o <= {Q_q[][q_width:],Q_z[][]};

data_r <= D[] - {Q_q[][q_width:],Q_z[][]}*{Q_q[][q_width:],Q_z[][]};

o_vaild <= ;

end

end

else

begin

data_o <= ;

data_r <= ;

o_vaild <= ;

end

end

//--------------------------------------------------------------------------------

endmodule

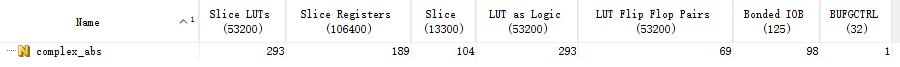

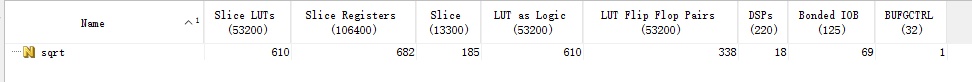

三种方法的精度对比以及资源占用情况

JPL近似

IPcordic使用:

牛顿迭代

可以看出资源占用:newtoon>JPL > IPcordic,精度的估计JPL<newtoon<IPcordic,

其中JPL 的计算速度快,但是误差太高了

单独求倒数的模块 / 快速高精度求平方根倒数的算法

FPGA开平方的实现的更多相关文章

- 基于FPGA的Sobel边缘检测的实现

前面我们实现了使用PC端上位机串口发送图像数据到VGA显示,通过MATLAB处理的图像数据直接是灰度图像,后面我们在此基础上修改,从而实现,基于FPGA的动态图片的Sobel边缘检测.中值滤波.Can ...

- 基于 FPGA 的图像边缘检测

本文主要内容是实现图像的边缘检测功能 目录 mif文件的制作 调用 ip 核生成rom以及在 questasim 仿真注意问题 灰度处理 均值滤波:重点是3*3 像素阵列的生成 sobel边缘检测 图 ...

- 【转】基于FPGA的Sobel边缘检测的实现

前面我们实现了使用PC端上位机串口发送图像数据到VGA显示,通过MATLAB处理的图像数据直接是灰度图像,后面我们在此基础上修改,从而实现,基于FPGA的动态图片的Sobel边缘检测.中值滤波.Can ...

- FPGA与simulink联合实时环路系列——实验三 按键key

实验三 按键key 实验内容 在FPGA的实验中,经常涉及到按键的使用,按键是必不可少的人机交互的器件之一,在这些实验中,有时将按键的键值读取显示到数码管.LCD或者是通过串口传送到PC的串口助手上进 ...

- FPGA与simulink联合实时环路系列——实验二LED

实验二LED 实验内容 在实验一的基础上,将simulink产生的测试信号输出到FPGA开发板上的LED灯进行显示,这里要在生成的硬件模型上进行修改,将传送到FPGA的信号输出到8个LED灯上,并且对 ...

- FPGA优化之高扇出

Fanout即扇出,模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛.因此,在写代码时应尽量避免高扇出的情况.但是,在某些特殊情况下,受到 ...

- 关于 FPGA 内部信号扇入扇出

扇入.扇出系数 扇入系数是指门电路允许的输入端数目.一般门电路的扇入系数为1—5,最多不超过8.扇出系数是指一个门的输出端所驱动同类型门的个数,或称负载能力.一般门电路的扇出系数为8,驱动器的扇出系数 ...

- FPGA Timing笔记

很多FPGA工程师都会遇到timing的问题,如何让FPGA跑到更快的处理频率是永久话题.决定FPGA的timing关键是什么?如何才能跑到更快的频率呢? A. 第一步需要了解FPGA的timing路 ...

- FPGA的引脚VCCINT 、VCCIO VCCA

首先是看到FPGA在配置的时候有三种不同的电VCCINT .VCCIO VCCA,于是就查了下有什么不同: FPGA一般会有许多引脚,那它们都有什么用呢? VCCINT为施加于 FPGA 内核逻辑的电 ...

随机推荐

- JavaScript—面向对象 贪吃蛇_2 游戏对象

游戏对象 function Game(map) { this.map = map; this.food = new Food(this.map) this.snake = new Snake(this ...

- ubuntu 插网线无法上网解决方案

前言 不知道最近是什么情况,ubuntu链接网线总是上不去网,但是wifi还能用,一直也就没有捣鼓,不过今天连wifi都不能用了,只能开始修理了. 修复方案 使用ifconfig命令查看以太网的名称 ...

- python 网络请求、下载

#获取qq群中的群成员qq号import requestsmembers = []url = 'https://qun.qq.com/cgi-bin/qun_mgr/search_group_memb ...

- IaaS SaaS PaaS区别

- 三、VIP课程:并发编程专题->01-并发编程之Executor线程池详解

01-并发编程之Executor线程池详解 线程:什么是线程&多线程 线程:线程是进程的一个实体,是 CPU 调度和分派的基本单位,它是比进程更小的能独立运行的基本单位.线程自己基本上不拥有系 ...

- UML-类图定义

1.之前,学习过领域模型(概念模型),与类图的区别: 1).属于OOA 2).没有方法,只有属性和关联 类图属于OOD,属于静态对象建模 2.例子 3.类元包含哪些? 1).类(抽象类) 2).接口

- [Algo] 649. String Replace (basic)

Given an original string input, and two strings S and T, replace all occurrences of S in input with ...

- shell里脚本里写个简单的函数,显示颜色

如果多次用到颜色显示,还是定义一个函数比较实在,具体什么颜色上网找一下 #!/bin/bash # 定义一个红色显示的函数 function echo_red () { local what=$* e ...

- Django静态文件配置-request方法-ORM简介-字段的增删改查

app的创建注意事项: 在Django新创建的app要在seetings.py中添加注册,才会生效 创建app:django-adminapp an startapp app名称 或者 python3 ...

- eclipse优化自动补全(解决空格、分号等上屏问题)

第一步:打开"Window"——>"Show View"——>"Other"——>找到"Plug-in Deve ...