FPGA 原语之一位全加器

FPGA原语之一位全加器

1、实验原理

一位全加器,三个输入,两个输出。进位输出Cout=AB+BC+CA,本位输出S=A异或B异或C。实验中采用三个与门、一个三输入或门(另外一个是两个或门,功能一致)、一个三输入异或门实现该简单功能。

2、实验操作

实验设计还是比较简单的,直接看代码即可:

- module test2(

- input clk,

- input rt_n,

- input [3:0] key_c,

- output [3:0] key_r,

- output [11:0] led

- );

- wire k1,k2,k3,k4;

- assign k1=key_c[0];

- assign k2=key_c[1];

- assign k3=key_c[2];

- assign k4=key_c[3];

- assign key_r=4'b0;

- xor xor1(led[0],k1,k2,k3);

- and and1(led[11],k1,k2);

- and and2(led[10],k2,k3);

- and and3(led[9],k3,k1);

- or or1(led[8],led[11],led[10]);

- or or2(led[2],led[8],led[9]);

- or or3(led[3],led[9],led[10],led[11]);

- endmodule

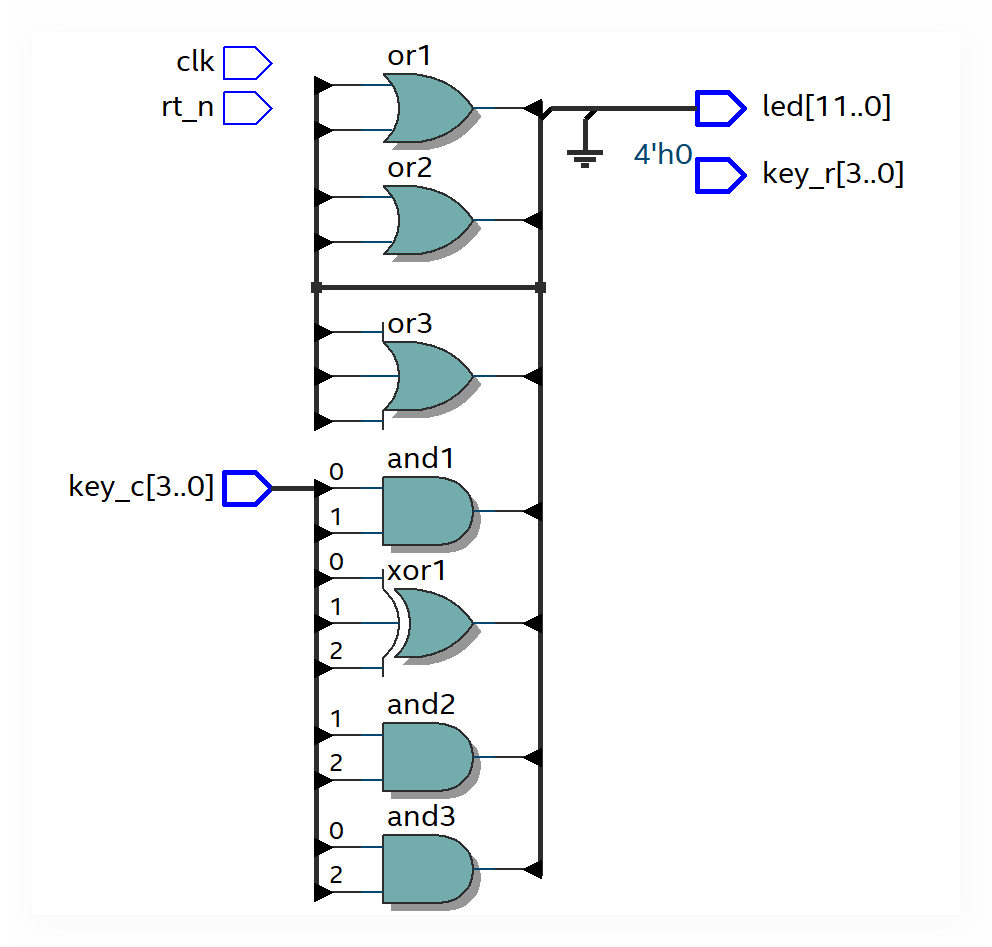

就是直接调用,输出结果直接显示在led上,也就没有区分led,下次可能需要注意一下。生成的RTL视图看不出具体的电路结构,只能看到调用的器件和总线。

3、实验结果

RTL视图

器件的数量和连线基本正确。板级验证就是按相应的输入即可得到具体的输出。这里就不展示了。后面可能验证的就是更加复杂的数字电路。可以将FPGA作为一个可以反复使用的数字电路实验平台。

FPGA 原语之一位全加器的更多相关文章

- 关于FPGA设计16位乘法器的两…

原文地址:关于FPGA设计16位乘法器的两种算法作者:ChrisChan 部分原代码如下: 用特权的右移算法虽复杂点,但节省不少LEs,如下图: 用左移算法尽管浅显易懂,但因每次都会从最右端移位,会占 ...

- FPGA代码一位半加器入门-第2篇

1. 代码比较简单,总结起来是用逻辑运算替代了数学运算加减,应该是因为这样的逻辑资源耗费的少.S是A+B的个位,CO是A+B的进位. module half_adder(A,B,S,CO); inpu ...

- 基于Verilog HDL的超前进位全加器设计

通常我们所使用的加法器一般是串行进位,将从输入的ci逐位进位地传递到最高位的进位输出co,由于电路是有延迟的,这样的长途旅行是需要时间的,所以为了加快加法器的运算,引入了超前进位全加器. 全加器的两个 ...

- 【FPGA学习】Verilog之加法器

在fpga工程应用设计中,随处可见加法器,乘法器等等.现在将一些常用模块和心得体会先记录下来,以便日后使用. 一位半加器: module halfadder(cout,sum,a,b); output ...

- Scheme实现数字电路仿真(2)——原语

版权申明:本文为博主窗户(Colin Cai)原创,欢迎转帖.如要转贴,必须注明原文网址 http://www.cnblogs.com/Colin-Cai/p/12045295.html 作者:窗户 ...

- Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi.Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号.列表有: Xi Yi Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 ...

- 2.计算机组成-数字逻辑电路 门电路与半加器 异或运算半加器 全加器组成 全加器结构 反馈电路 振荡器 存储 D T 触发器 循环移位 计数器 寄存器 传输门电路 译码器 晶体管 sram rom 微处理 计算机

现代计算机的各个部件到底是如何通过逻辑电路构成的呢 半加器 我们说过了门电路 看似简单的三种门电路却是组成了整个逻辑电路的根基 真值表--其实就是根据输入输出状态枚举罗列出来的所有可能 比如有一台 ...

- verilog之四位全加器的编译及仿真(用开源免费的软件——iverilog+GTKWave)

verilog之四位全加器的编译及仿真(用开源免费的软件——iverilog+GTKWave) 四位全加器的verilog的代码比比皆是,这里上一个比较简单的: /* 4位全加器全加器需要有输入输出, ...

- FPGA之IO信号类型深入理解

在FPGA设计开发中,很多场合会遇到同一根信号既可以是输入信号,又可以是输出信号,即IO类型(Verilog定义成inout). 对于inout型的信号,我们既可以使用FPGA原语来实现,也可以使用V ...

- ModelSim仿真入门

ModelSim仿真入门之一:软件介绍 编写这个教程之前,为了让不同水平阶段的人都能阅读,我尽量做到了零基础入门这个目标,所有的操作步骤都经过缜密的思考,做到了详细再详细的程度. 如果您是FPGA开发 ...

随机推荐

- 立创EDA使用笔记

立创EDA 在立创EDA上制作的PCB可以直接导入到嘉立创下单, 每个注册用户每个月可以下两个免费订单, 限制PCB尺寸10CMx10CM, 每单五片, 连制作到快递全部免费, 非常适合做样板. 立创 ...

- 【OpenGL ES】渲染管线

1 前言 渲染管线是指图形渲染流程,涉及到的概念非常多,主要包含图元.片段.光栅化.空间.变换.裁剪.着色器.片段测试.混合等.渲染管线主体流程如下: 为方便读者理解渲染管线,本文将先介绍顶点 ...

- MacBook M1 VulnHub靶机搭建(arm Mac搭建x86 ova镜像)

个人博客: xzajyjs.cn 自从换了M1系的arm Mac后,原本的Vulnhub上的几乎所有靶场按照之前的方法都无法正常搭建了(VirtualBox),在外网论坛上找了一遍,有一个相对麻烦一些 ...

- 问题:RuntimeError: Model class LuffyAPI.apps.user.models.UserInfo doesn't declare an explicit app_label and isn't in an application in INSTALLED_APPS.

问题截图 报错原因 提示app未注册,但实际上已经注册的 1. # settings配置文件移动后要将这个settings添加到环境变量中 sys.path.insert(0, BASE_DIR) # ...

- 如何在矩池云使用 Poetry 管理项目环境

官网介绍:Poetry is a tool for dependency management and packaging in Python. It allows you to declare th ...

- 在MATPool矩池云完成Pytorch训练MNIST数据集

本文为矩池云入门手册的补充:Pytorch训练MNIST数据集代码运行过程. 案例代码和对应数据集,以及在矩池云上的详细操作可以在矩池云入门手册中查看,本文基于矩池云入门手册,默认用户已经完成了机器租 ...

- 使用objc4V818.2源码编译,没有什么比苹果底层源码更有说服力去证明底层原理真假

前言 为什么会想要调试源码? 苹果开源了部分源码, 但相似内容太多, 基本找不到代码见的对应关系, 如果能像自己工程一样进行跳转那多好哇~~ 苹果源码开源地址: https://opensource. ...

- 【Azure 应用服务】Function App / App Service 连接 Blob 报错

问题描述 因 Blob 启用了防火墙功能,但是当把App Service 或 Function App的出站IP地址都加入到Blob的白名单中,为什么访问还是403错误呢? 问题解答 Azure St ...

- 【Azure Developer】使用 Azure VM 上的用户分配托管标识访问 Azure Key Vault 中国区代码示例

问题描述 在Global版本的Azure Key Vault 文档中,有一节介绍在Azure VM中使用标识获取访问令牌,调用Key Vault中的资源.但是在示例中,只有curl的命令执行,而没有代 ...

- multiple definition of `MainWindow::MainWindow(QWidget*)

qt刚建好工程运行的时候没问题,后面写了一点东西之后,再运行就发现出现MainWindow重复,我不理解. 解决方法:删除重复的引用. 再重新构建一下就好了.