FPGA学习笔记(三)—— 数字逻辑设计基础(抽象的艺术)

FPGA设计的是数字逻辑,在开始用HDL设计之前,需要先了解一下基本的数字逻辑设计—— 一门抽象的艺术。

现实世界是一个模拟的世界,有很多模拟量,比如温度,声音······都是模拟信号,通过对模拟信号进行约束,我们就会抽象出来高电平和低电平,也就是0和1,用来构建整个数字逻辑世界,这个约束就是电平规则约束,比如常见的有以下几种:

| 电平约束 | VDD/VCC | 0 | 1 |

| CMOS | 3~8V | 0~0.3VDD | 0.7~1VDD |

| TTL | 5V±5% | 0~0.7 | 2.4~5 |

| LVCMOS | 3.3 | 0~0.9 | 2.7~3.3 |

| LVTTL | 3.3 | 0~0.8 | 2.4~3.3 |

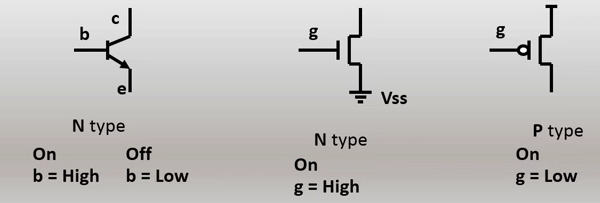

晶体管(三极管和MOS管)主要有两种作用,一是工作在放大状态,用于信号放大,二是工作在截止区(断)和饱和区(通),所以我们可以用晶体管实现数字世界的0和1:

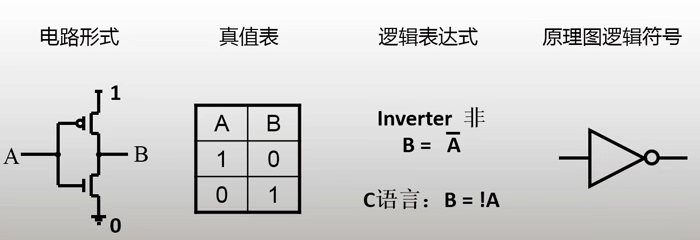

接下来我们用0和1进行最基本的组合,构成一个只有两个晶体管的最简单的门电路 —— 非门:

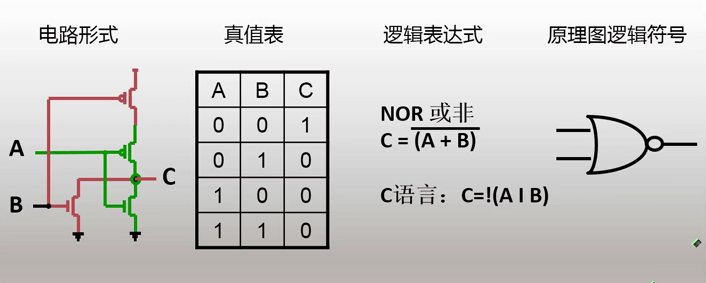

再稍微复杂一下,我们可以用4个晶体管构成与非门、或非门、三态门:

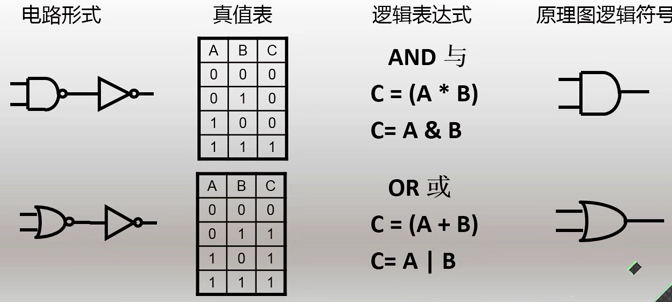

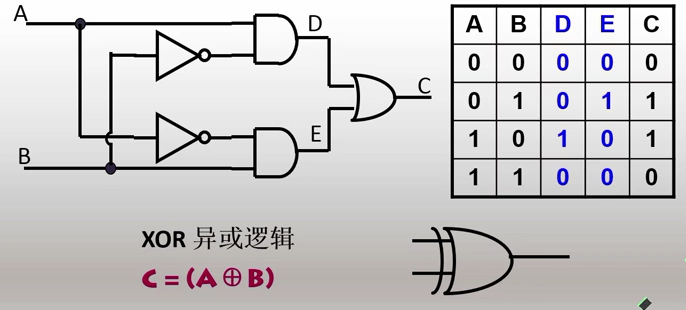

这个时候可以进一步抽象,不再利用晶体管构建电路,而是用非门、与非门、或非门构建更复杂的门电路,比如非门、或门、异或、同或等等······

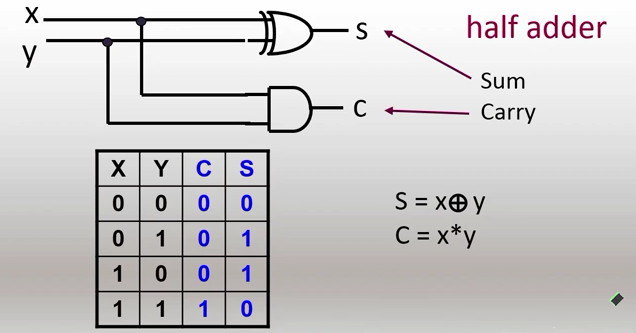

有了这些基本的门电路,我们可以用这些门电路搭建各种各样的功能电路,比如用一个异或门和一个非门构成半加器(HalfAdder):

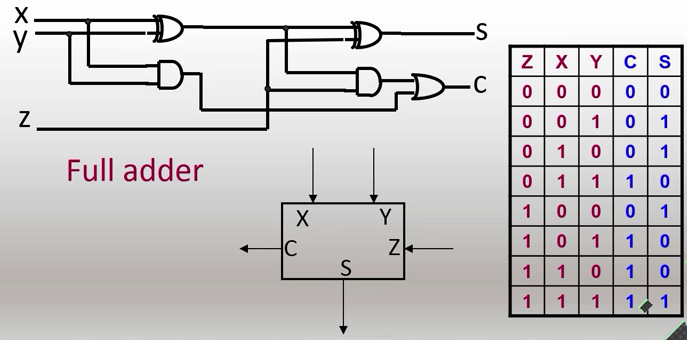

这个时候再次进行抽象,将功能模块用一个带有输入输出表示的小方块表示,然后用这些小方块去搭建更复杂的电路,比如将半加器抽象成一个功能模块,然后用两个半加器搭建一个全加器(Adder):

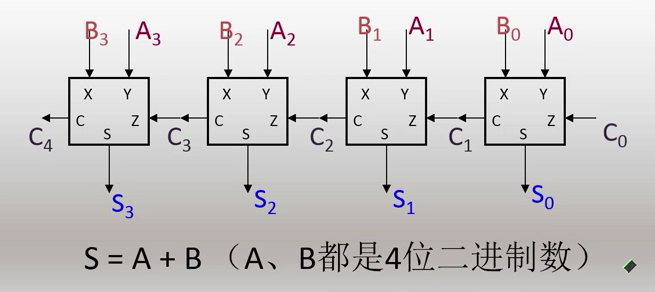

全加器设计出来之后,也被抽象成了如上图所示的功能模块,我们依然可以用这个功能模块去搭建更复杂的功能,比如将四个全加器级联起来构成四位加法器:

用基本的逻辑门电路构建半加器,再用半加器构建全加器,再将1bit全加器级联构成4bit加法器,这种设计体现了数字逻辑设计中最基本的思想 —— 层次化和模块化;

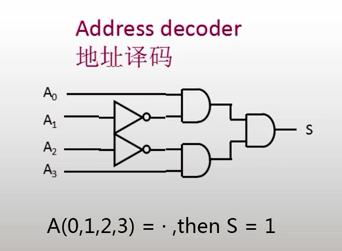

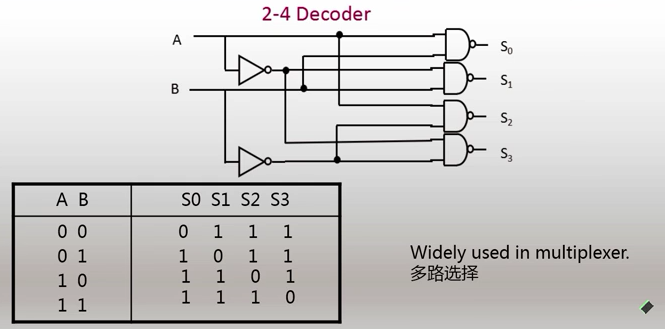

利用这种设计思想,除了用门电路搭建多位加法器之外,还可以实现各种各样的功能电路,比如最常见的组合逻辑电路多路选择器、译码器(地址译码器、显示译码器、2-4译码器等等),这些电路有一个最大的特点就是输出只取决于当前输入:

上述功能电路都是组合逻辑电路,输出只取决于当前输入,那么,如何将0和1锁存起来不要变化呢?我们可以用门电路搭建一个D锁存器,当控制端C为1时,输出 = 输入,当控制端C为0时,输出保持上一状态的值不变,这样就成功的将0和1锁存起来;

当控制端C不再人为控制,而是接入时钟信号CLK,这样它就会不断的进行锁存、刷新,构成一个最基本的时序逻辑电路,时序逻辑电路的特点是输出不仅与输入有关,还与上一状态也有关,同样的,这个用门电路搭建的电路也可以抽象成一个带有输入和输出的方块,如图所示:

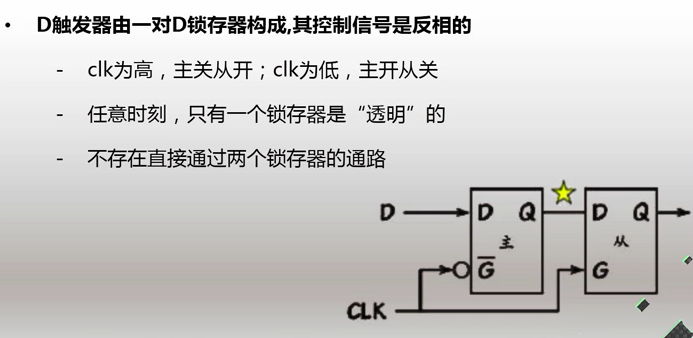

对于D锁存器而言,当控制端C为高电平时,输出一直保持与输入同步,这样的功能还不能够满足应用,我们希望它可以只在某个特定时刻发生变化,上升沿或者下降沿触发,也叫边沿触发,所以,我们用两个D锁存器构成D触发器来实现这个功能:在时钟CLK上升沿将输入刷新到输出,其它时刻均保持不变:

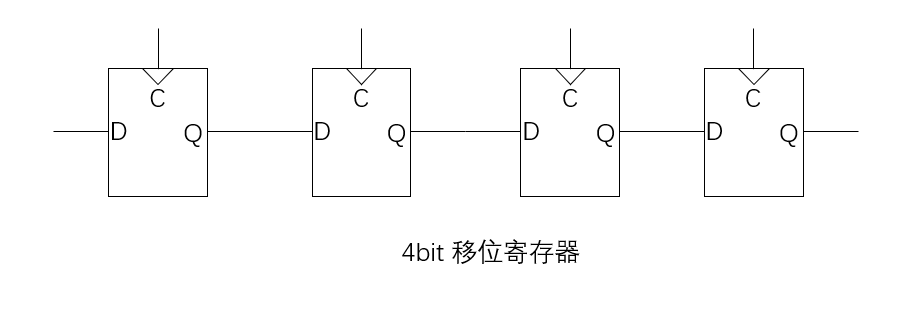

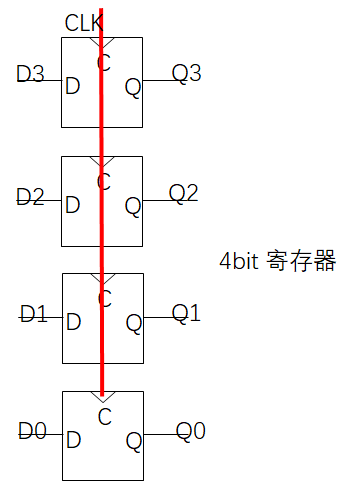

同样的,我们可以将D触发器抽象成一个带有输入输出的小方块(注意:CLK信号带有三角形表示边沿触发),当4个小方块共享一个CLK信号时,就构成了一个4bit寄存器;当4个小方块一级一级进行级联时,就构成了一个4bit移位寄存器,在数字逻辑世界中,左移1bit和右移1bit就表示了乘法和除法;

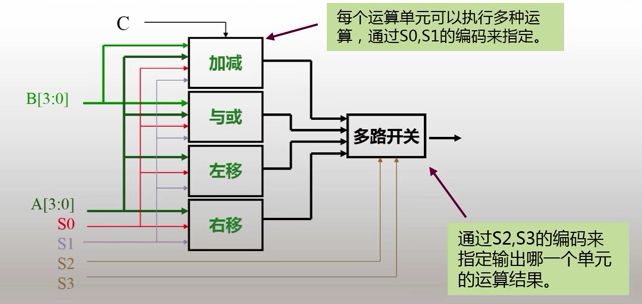

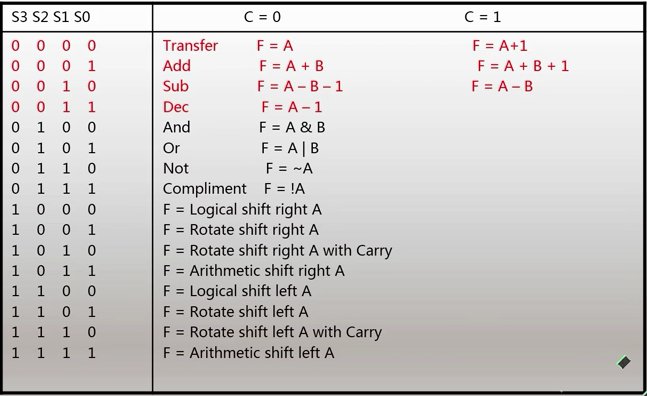

抽象出来D锁存器和D触发器的小方块后,我们构建了寄存器,然后我们可以用寄存器来构建一些简单的时序逻辑电路,比如计数器;也可以用来构建同步时序逻辑电路,主要为状态机和流水线;设计这些越来越复杂的系统时,用原理图的方式会变得越来越繁琐,实现起来用74系列数字逻辑元件会更加复杂,幸好我们有硬件描述语言,有FPGA,可以帮我们更加方便的设计复杂数字逻辑系统,接下来的几篇会讲解用硬件描述语言verilog去描述逻辑门,描述组合逻辑功能模块,描述时序逻辑电路功能模块,然后进一步描述最重要的数字逻辑设计 —— FSM有限状态机的设计,最后,用两张图了解一下数字逻辑系统设计的巅峰之作 —— CPU(Center Peocess Uint),燃烧对数字逻辑设计的激情!

FPGA学习笔记(三)—— 数字逻辑设计基础(抽象的艺术)的更多相关文章

- Oracle学习笔记三 SQL命令

SQL简介 SQL 支持下列类别的命令: 1.数据定义语言(DDL) 2.数据操纵语言(DML) 3.事务控制语言(TCL) 4.数据控制语言(DCL)

- python学习笔记4_类和更抽象

python学习笔记4_类和更抽象 一.对象 class 对象主要有三个特性,继承.封装.多态.python的核心. 1.多态.封装.继承 多态,就算不知道变量所引用的类型,还是可以操作对象,根据类型 ...

- 学习笔记(三)--->《Java 8编程官方参考教程(第9版).pdf》:第十章到十二章学习笔记

回到顶部 注:本文声明事项. 本博文整理者:刘军 本博文出自于: <Java8 编程官方参考教程>一书 声明:1:转载请标注出处.本文不得作为商业活动.若有违本之,则本人不负法律责任.违法 ...

- muduo网络库学习笔记(三)TimerQueue定时器队列

目录 muduo网络库学习笔记(三)TimerQueue定时器队列 Linux中的时间函数 timerfd简单使用介绍 timerfd示例 muduo中对timerfd的封装 TimerQueue的结 ...

- Liunx学习笔记(三) 文件权限

一.文件权限 1.查看文件权限 (1)文件权限 在 Linux 中对于文件有四种访问权限,列举如下: 可读取:r,Readable 可写入:w,Writable 可执行:x,Execute 无权限:- ...

- ZooKeeper学习笔记三:使用ZooKeeper实现一个简单的配置中心

作者:Grey 原文地址:ZooKeeper学习笔记三:使用ZooKeeper实现一个简单的配置中心 前置知识 完成ZooKeeper集群搭建以及熟悉ZooKeeperAPI基本使用 需求 很多程序往 ...

- [Firefly引擎][学习笔记三][已完结]所需模块封装

原地址:http://www.9miao.com/question-15-54671.html 学习笔记一传送门学习笔记二传送门 学习笔记三导读: 笔记三主要就是各个模块的封装了,这里贴 ...

- JSP学习笔记(三):简单的Tomcat Web服务器

注意:每次对Tomcat配置文件进行修改后,必须重启Tomcat 在E盘的DATA文件夹中创建TomcatDemo文件夹,并将Tomcat安装路径下的webapps/ROOT中的WEB-INF文件夹复 ...

- java之jvm学习笔记三(Class文件检验器)

java之jvm学习笔记三(Class文件检验器) 前面的学习我们知道了class文件被类装载器所装载,但是在装载class文件之前或之后,class文件实际上还需要被校验,这就是今天的学习主题,cl ...

随机推荐

- LAV Filter 源代码分析 3: LAV Video (1)

LAV Video 是使用很广泛的DirectShow Filter.它封装了FFMPEG中的libavcodec,支持十分广泛的视频格式的解码.在这里对其源代码进行详细的分析. LAV Video ...

- 【52】java多线程剖析

线程的状态: 线程共有下面4种状态: 新建状态(New): 新创建了一个线程对象,当你用new创建一个线程时,该线程尚未运行. 就绪状态(Runnable): 线程对象创建后,其他线程调用了该对象的s ...

- Android高通平台调试Camera驱动全纪录

项目比较紧,3周内把一个带有外置ISP,MIPI数据通信,800万像素的camera从无驱动到实现客户全部需求. 1日 搭平台,建环境,编译内核,烧写代码. 我是一直在Window下搭个虚拟机登服务器 ...

- ios的位置和方向(来自苹果官方文档,仅供简单参考)

取得用户的当前位置 Core Location框架使您可以定位设备的当前位置,并将这个信息应用到程序中.该框架利用设备内置的硬件,在已有信号的基础上通过三角测量得到固定位置,然后将它报告给您的代码.在 ...

- javascript加RoR实现JSONP

我们知道不同域中的js代码受同源策略的限制,不同域中的AJAX同样受此限制,不过使用html中的script远程脚本可以跳过该限制,下面我们实际看一下利用RoR和js如何实现所谓的JSONP. 这里只 ...

- 用JAVA代码获取Weblogic配置的JNDI 数据源连接

第一步:生成与JDK版本对应的weblogicjar,利用cmd 进入到weblogic_home 路径下进入到server/lib目录,然后运行 JDK 1.6 命令 "java -j ...

- Mac OS X 10.10优胜美地如何完美接管iphone上的电话和短信

自从今年苹果第一次的发布会上毛猫就特别注意这个功能,感觉特别Cool,特别方便.但直到今天毛猫才第一次成功测试出这个功能呀!虽然handoff功能还未测出来,但是觉得在mac上发短信和打电话也已经足够 ...

- 2010_3_1最新 完整 FFMPEG 编译详解

在网上看了很多编译详解,都很零散.经过自己的编译,解决一些BUG,在此分享自己的一些经验... 话不多说了!直接上贴. 第一步:准备编译平台. 需要 一个 MinGW 和 一个 MSYS 安装包 以及 ...

- Factory Method (工厂模式)

什么是工厂设计模式 根据名字即可了解,工厂肯定是用来生产产品的,在我们的程序开发中,需要用到不同的类,对于熟悉SSH.SSM开发的可以知道,在初期学习的时候,总是有一个框架提供好的的factory供我 ...

- Flask类的属性和方法大全

Flask Property__class____dict____doc____module__app_ctx_globals_classconfig_classdebugdefault_config ...