基于Verilog HDL的超前进位全加器设计

通常我们所使用的加法器一般是串行进位,将从输入的ci逐位进位地传递到最高位的进位输出co,由于电路是有延迟的,这样的长途旅行是需要时间的,所以为了加快加法器的运算,引入了超前进位全加器。

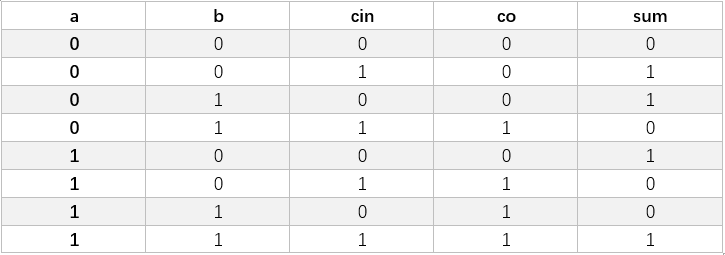

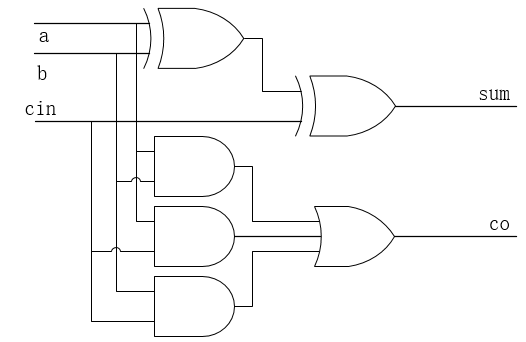

全加器的两个逻辑表达式

sum = a ^ b ^ cin;

co = a & b | (a ^ b) & cin;

sum = a ^ b ^ cin;

co = a & b + a & cin + b & cin;

这两个公式的电路图看起来不一样,但其实是一样的,同一个功能的电路可以有不同的描述方式。而且把co这两个表达式展开,观察其最小项表达式(画卡诺图),最终的结果也是一样的和真值表完全相符。

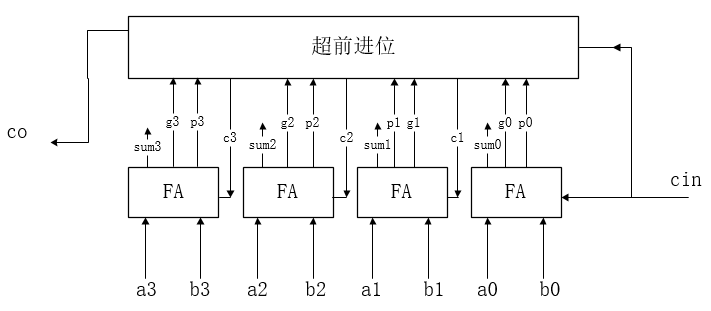

四位超前进位全加器

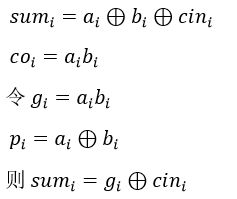

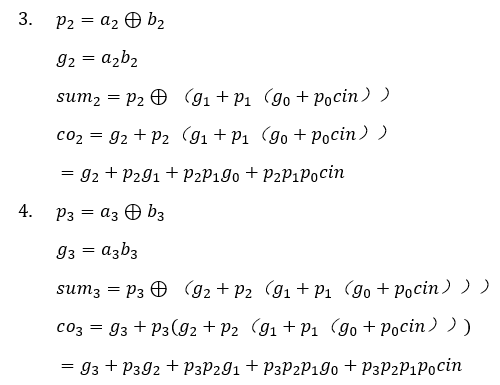

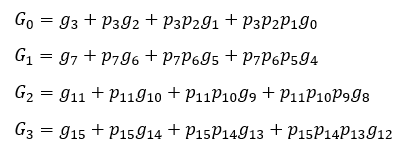

根据一位全加器的表达式可以推理出,四位全加器每一位的计算通式。

为了达到并行的效果,通过公式化简,得到co和sum的表达式,每一位之间的运算都是独立的,和低位的运算没有关系,这样做达到完全并行,这就是四位超前进位全加器。

有了四位全加器,我们可以以通过四位超前进位全加器设计出16位、32位、64位超前进位全加器,有些设计方法是将四个四位超前进位全加器串联起来,即将低四位的co连接到高四位的cin上,但这样并不能算得上是真正的并行,每四位是并行的,但每四位之间是串行的,博主目的是要达到完全并行的设计,继续往下看吧。

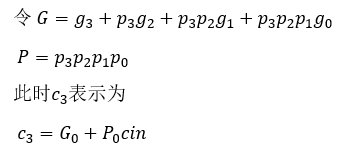

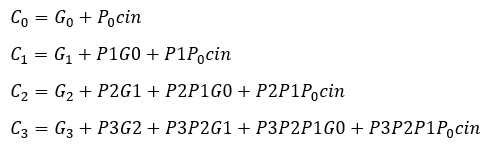

这里的g是generation(生成)的意思,当a和b同时为1时,1位全加器必然产生进位,p表示propagation(传到)的意思,当a或b中有一个是1时,如果进位cin位1,1位全加器必然产生进位,利用这个原理即可做出四位超前进位全加器之间的超前进位。

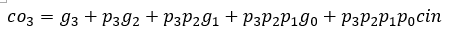

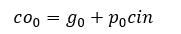

四位超前进位全加器的co进位输出端为

这与一位全加器的进位类似,

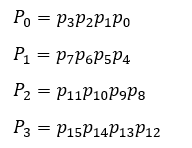

我们可以推出如下关系式

我们通过调用四个超前进位全加器即可实现16位超前进位全加器,那么实现64位超前进位全加器其实也是和这个实现方法一样了,调用4个超前进位全加器就可以实现64位超前进位全加器。不过实际中CPU采用的是超前进位和串行进位集合,并行设计占面积,串行设计速度慢,尽量做到面积与速度之间的权衡。

博主最近要学Verilog设计一个32位的简易CPU,其中ALU中想用上32位超前进位全加器。对于32位超前进位全加器,也是一样的方法。我选择的是三级并行设计,即四个四位超前进位全加器组间并行实现16位超前进位全加器,两个16位超前进位全加器组间并行实现32位超前进位全加器,至于两级并行还是多级并行看自己选择了。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/8798972.html

基于Verilog HDL的超前进位全加器设计的更多相关文章

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 基于Verilog HDL 的数字电压表设计

本次实验是在“基于Verilog HDL的ADC0809CCN数据采样”实验上进一步改进,利用ADC0809采集到的8位数据,进行BCD编码,以供查表方式相加进行显示,本次实验用三位数码管. ADC0 ...

- 基于Verilog HDL 各种实验

菜鸟做的的小实验链接汇总: 1.基于Verilog HDL 的数字时钟设计 2.乘法器 3.触发器(基本的SR触发器.同步触发器.D触发器) 4.基于Verilog HDL的ADC ...

- 基于Verilog的奇数偶数小数分频器设计

今天呢,由泡泡鱼工作室发布的微信公共号“硬件为王”(微信号:king_hardware)正式上线啦,关注有惊喜哦.在这个普天同庆的美好日子里,小编脑洞大开,决定写一首诗赞美一下我们背后伟大的团队,虽然 ...

- paper:基于verilog HDL 的高速可综合FSM设计

1.寄存器输出型状态机 VS 组合逻辑输出型状态机 2.状态编码方法 这块讲的不好,也比较少. 3.系统设计中模块划分的指导性原则

- 基于Verilog HDL的二进制转BCD码实现

在项目设计中,经常需要显示一些数值,比如温湿度,时间等等.在数字电路中数据都是用二进制的形式存储,要想显示就需要进行转换,对于一个两位的数值,对10取除可以得到其十位的数值,对10取余可以得到个位的数 ...

- 基于Verilog HDL的ADC0809CCN数据采样

本实验是用ADC0809CCN进行数据采样,并用7段数码管进行显示. ADC0809由一个8路模拟开关.一个地址锁存与译码器.一个A/D转换器和一个三态输出锁存器组成.多路开关可选通8个模拟通道,允许 ...

- 【转】Verilog HDL常用建模方式——《Verilog与数字ASIC设计基础》读书笔记(四)

Verilog HDL常用建模方式——<Verilog与数字ASIC设计基础>读书笔记(四) Verilog HDL的基本功能之一是描述可综合的硬件逻辑电路.所谓综合(Synthesis) ...

随机推荐

- 3Des加解密 C#--->Java

Java的Byte范围为-128至127,c#的Byte范围是0-255.核心是确定Mode和Padding,关于这两个的意思可以搜索3DES算法相关文章. C#采用CBC Mode,PKCS7 Pa ...

- docker初次体验-管理MySQL+tomcat镜像

引言 平时经常用linux,我没少吃苦后悔linux没好好研究研究.装一些软件配一些环境时很是害怕,多亏有了docker.docker是一个应用容器引擎,可以管理很多的软件镜像,这些镜像被官方放在了d ...

- table_rows查询优化

日常应用运维工作中,Dev或者db本身都需要统计表的行数,以此作为应用或者维护的一个信息参考.也许很多人会忽略select count(*) from table_name类似的sql对数据库性能的影 ...

- Online Judge(OJ)搭建——1、项目介绍

项目名 Piers 在线评测 项目需求 用户: 获取题库.题目的相关信息. 在线对代码进行编译.执行.保存.返回运行(编译)结果. 总体题目评测成绩查询. 用户信息服务,包括注册.登录.忘记密码.邮箱 ...

- 以太坊挖矿源码:ethash算法

本文具体分析以太坊的共识算法之一:实现了POW的以太坊共识引擎ethash. 关键字:ethash,共识算法,pow,Dagger Hashimoto,ASIC,struct{},nonce,FNV ...

- 微信小程序开发之--”emplate模板“的应用

第一步:定义模板 ①:新建一个template文件夹用来管理项目中所有的模板(本文案例定义文件夹名为:temp): ②.新建一个wxml文件来定义模板(本文案例定义文件夹名为:temp.wxml): ...

- Java 缩写总结

1.JVM:Java Virtual Machine(Java虚拟机)的缩写. 它是一个虚构出来的计算机,是通过在实际的计算机上仿真模拟各种计算机功能来实现的. Java语言的一个非常重要的特点就是与 ...

- angular的$scope的使用

1. 可以在scope中直接使用 // 监听日期变化 $scope.$watch('vaFilter.startEffectiveDate', function(newDate, oldDate, s ...

- java swing 下拉框与文本框

import java.awt.*; import javax.swing.*; import javax.swing.border.*; import java.awt.event.*; publi ...

- Java I/O 总结

Java I/O的的架构使用了装饰器的模式,我们在使用流的时候需要新建很多的装饰器对象,对源数据进行层层包装.各个包装类名以及它们的应用场景比较多,初学的时候难以摸清规律,这里我把它们归一下类,方便大 ...