[原创]Modelsim后仿真

因调试需要,进行后仿真,ISE生成的sim文件和sdf文件

`timescale ns/ ps module lut_dly (

clkout, fpga_clk, config_in

);

output clkout;

input fpga_clk;

input [ : ] config_in;

wire clk_in;

wire dly1;

wire config_in_4_IBUF_49;

wire config_in_5_IBUF_50;

wire dly2_0;

wire dly3;

wire config_in_2_IBUF_53;

wire config_in_3_IBUF_54;

wire dly4_0;

wire dly5;

wire config_in_0_IBUF_57;

wire config_in_1_IBUF_58;

wire dly2;

wire dly1_pack_1;

wire dly4;

wire dly3_pack_1;

wire clkout_OBUF_129;

wire dly5_pack_1;

wire \config_in<>/INBUF ;

wire \config_in<>/INBUF ;

wire \config_in<>/INBUF ;

wire \config_in<>/INBUF ;

wire \config_in<>/INBUF ;

wire \config_in<>/INBUF ;

wire \clkout/O ;

wire \fpga_clk/INBUF ;

wire VCC;

initial $sdf_annotate("lut_dly_timesim.sdf");

X_BUF #(

.LOC ( "SLICE_X88Y0" ))

\dly2/XUSED (

.I(dly2),

.O(dly2_0)

);

X_BUF #(

.LOC ( "SLICE_X88Y0" ))

\dly2/YUSED (

.I(dly1_pack_1),

.O(dly1)

);

X_LUT4 #(

.INIT ( 'h8888 ),

.LOC ( "SLICE_X88Y0" ))

u_lut6 (

.ADR0(clk_in),

.ADR1(config_in_5_IBUF_50),

.ADR2(VCC),

.ADR3(VCC),

.O(dly1_pack_1)

);

X_BUF #(

.LOC ( "SLICE_X88Y1" ))

\dly4/XUSED (

.I(dly4),

.O(dly4_0)

);

X_BUF #(

.LOC ( "SLICE_X88Y1" ))

\dly4/YUSED (

.I(dly3_pack_1),

.O(dly3)

);

X_LUT4 #(

.INIT ( 'h3C0C ),

.LOC ( "SLICE_X88Y1" ))

u_lut4 (

.ADR0(VCC),

.ADR1(dly2_0),

.ADR2(config_in_3_IBUF_54),

.ADR3(clk_in),

.O(dly3_pack_1)

);

X_BUF #(

.LOC ( "SLICE_X89Y0" ))

\clkout_OBUF/YUSED (

.I(dly5_pack_1),

.O(dly5)

);

X_LUT4 #(

.INIT ( 'h3838 ),

.LOC ( "SLICE_X89Y0" ))

u_lut2 (

.ADR0(clk_in),

.ADR1(config_in_1_IBUF_58),

.ADR2(dly4_0),

.ADR3(VCC),

.O(dly5_pack_1)

);

X_IPAD #(

.LOC ( "PAD685" ))

\config_in<>/PAD (

.PAD(config_in[])

);

X_BUF #(

.LOC ( "PAD685" ))

config_in_0_IBUF (

.I(config_in[]),

.O(\config_in<>/INBUF )

);

X_BUF #(

.LOC ( "PAD685" ))

\config_in<>/IFF/IMUX (

.I(\config_in<>/INBUF ),

.O(config_in_0_IBUF_57)

);

X_IPAD #(

.LOC ( "PAD686" ))

\config_in<>/PAD (

.PAD(config_in[])

);

X_BUF #(

.LOC ( "PAD686" ))

config_in_1_IBUF (

.I(config_in[]),

.O(\config_in<>/INBUF )

);

X_BUF #(

.LOC ( "PAD686" ))

\config_in<>/IFF/IMUX (

.I(\config_in<>/INBUF ),

.O(config_in_1_IBUF_58)

);

X_IPAD #(

.LOC ( "PAD683" ))

\config_in<>/PAD (

.PAD(config_in[])

);

X_BUF #(

.LOC ( "PAD683" ))

config_in_2_IBUF (

.I(config_in[]),

.O(\config_in<>/INBUF )

);

X_BUF #(

.LOC ( "PAD683" ))

\config_in<>/IFF/IMUX (

.I(\config_in<>/INBUF ),

.O(config_in_2_IBUF_53)

);

X_IPAD #(

.LOC ( "PAD681" ))

\config_in<>/PAD (

.PAD(config_in[])

);

X_BUF #(

.LOC ( "PAD681" ))

config_in_3_IBUF (

.I(config_in[]),

.O(\config_in<>/INBUF )

);

X_BUF #(

.LOC ( "PAD681" ))

\config_in<>/IFF/IMUX (

.I(\config_in<>/INBUF ),

.O(config_in_3_IBUF_54)

);

X_IPAD #(

.LOC ( "PAD688" ))

\config_in<>/PAD (

.PAD(config_in[])

);

X_BUF #(

.LOC ( "PAD688" ))

config_in_4_IBUF (

.I(config_in[]),

.O(\config_in<>/INBUF )

);

X_BUF #(

.LOC ( "PAD688" ))

\config_in<>/IFF/IMUX (

.I(\config_in<>/INBUF ),

.O(config_in_4_IBUF_49)

);

X_IPAD #(

.LOC ( "PAD682" ))

\config_in<>/PAD (

.PAD(config_in[])

);

X_BUF #(

.LOC ( "PAD682" ))

config_in_5_IBUF (

.I(config_in[]),

.O(\config_in<>/INBUF )

);

X_BUF #(

.LOC ( "PAD682" ))

\config_in<>/IFF/IMUX (

.I(\config_in<>/INBUF ),

.O(config_in_5_IBUF_50)

);

X_OPAD #(

.LOC ( "PAD680" ))

\clkout/PAD (

.PAD(clkout)

);

X_OBUF #(

.LOC ( "PAD680" ))

clkout_OBUF (

.I(\clkout/O ),

.O(clkout)

);

X_IPAD #(

.LOC ( "PAD684" ))

\fpga_clk/PAD (

.PAD(fpga_clk)

);

X_BUF #(

.LOC ( "PAD684" ))

u_ibufg (

.I(fpga_clk),

.O(\fpga_clk/INBUF )

);

X_BUF #(

.LOC ( "PAD684" ))

\fpga_clk/IFF/IMUX (

.I(\fpga_clk/INBUF ),

.O(clk_in)

);

X_LUT4 #(

.INIT ( 'h0FA0 ),

.LOC ( "SLICE_X88Y0" ))

u_lut5 (

.ADR0(clk_in),

.ADR1(VCC),

.ADR2(config_in_4_IBUF_49),

.ADR3(dly1),

.O(dly2)

);

X_LUT4 #(

.INIT ( 'h3C30 ),

.LOC ( "SLICE_X88Y1" ))

u_lut3 (

.ADR0(VCC),

.ADR1(config_in_2_IBUF_53),

.ADR2(dly3),

.ADR3(clk_in),

.O(dly4)

);

X_LUT4 #(

.INIT ( 'h0AF0 ),

.LOC ( "SLICE_X89Y0" ))

u_lut1 (

.ADR0(clk_in),

.ADR1(VCC),

.ADR2(dly5),

.ADR3(config_in_0_IBUF_57),

.O(clkout_OBUF_129)

);

X_BUF #(

.LOC ( "PAD680" ))

\clkout/OUTPUT/OFF/OMUX (

.I(clkout_OBUF_129),

.O(\clkout/O )

);

X_ONE NlwBlock_lut_dly_VCC (

.O(VCC)

);

endmodule `timescale ps / ps module glbl (); parameter ROC_WIDTH = ;

parameter TOC_WIDTH = ; wire GSR;

wire GTS;

wire PRLD; reg GSR_int;

reg GTS_int;

reg PRLD_int; //-------- JTAG Globals --------------

wire JTAG_TDO_GLBL;

wire JTAG_TCK_GLBL;

wire JTAG_TDI_GLBL;

wire JTAG_TMS_GLBL;

wire JTAG_TRST_GLBL; reg JTAG_CAPTURE_GLBL;

reg JTAG_RESET_GLBL;

reg JTAG_SHIFT_GLBL;

reg JTAG_UPDATE_GLBL; reg JTAG_SEL1_GLBL = ;

reg JTAG_SEL2_GLBL = ;

reg JTAG_SEL3_GLBL = ;

reg JTAG_SEL4_GLBL = ; reg JTAG_USER_TDO1_GLBL = 'bz;

reg JTAG_USER_TDO2_GLBL = 'bz;

reg JTAG_USER_TDO3_GLBL = 'bz;

reg JTAG_USER_TDO4_GLBL = 'bz; assign (weak1, weak0) GSR = GSR_int;

assign (weak1, weak0) GTS = GTS_int;

assign (weak1, weak0) PRLD = PRLD_int; initial begin

GSR_int = 'b1;

PRLD_int = 'b1;

#(ROC_WIDTH)

GSR_int = 'b0;

PRLD_int = 'b0;

end initial begin

GTS_int = 'b1;

#(TOC_WIDTH)

GTS_int = 'b0;

end endmodule

SDF文件

(DELAYFILE

(SDFVERSION "3.0")

(DESIGN "lut_dly")

(DATE "Sun Mar 22 15:04:04 2015")

(VENDOR "Xilinx")

(PROGRAM "Xilinx SDF Writer")

(VERSION "K.31")

(DIVIDER /)

(VOLTAGE 1.425)

(TEMPERATURE )

(TIMESCALE ps)

(CELL (CELLTYPE "X_BUF")

(INSTANCE dly2\/XUSED)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE dly2\/YUSED)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_LUT4")

(INSTANCE u_lut6)

(DELAY

(ABSOLUTE

(PORT ADR0 ( ))

(PORT ADR1 ( ))

(IOPATH ADR0 O ( ))

(IOPATH ADR1 O ( ))

(IOPATH ADR2 O ( ))

(IOPATH ADR3 O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE dly4\/XUSED)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE dly4\/YUSED)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_LUT4")

(INSTANCE u_lut4)

(DELAY

(ABSOLUTE

(PORT ADR1 ( ))

(PORT ADR2 ( ))

(PORT ADR3 ( ))

(IOPATH ADR0 O ( ))

(IOPATH ADR1 O ( ))

(IOPATH ADR2 O ( ))

(IOPATH ADR3 O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE clkout_OBUF\/YUSED)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_LUT4")

(INSTANCE u_lut2)

(DELAY

(ABSOLUTE

(PORT ADR0 ( ))

(PORT ADR1 ( ))

(PORT ADR2 ( ))

(IOPATH ADR0 O ( ))

(IOPATH ADR1 O ( ))

(IOPATH ADR2 O ( ))

(IOPATH ADR3 O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in_0_IBUF)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in\<\>\/IFF\/IMUX)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in_1_IBUF)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in\<\>\/IFF\/IMUX)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in_2_IBUF)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in\<\>\/IFF\/IMUX)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in_3_IBUF)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in\<\>\/IFF\/IMUX)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in_4_IBUF)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in\<\>\/IFF\/IMUX)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in_5_IBUF)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE config_in\<\>\/IFF\/IMUX)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_OBUF")

(INSTANCE clkout_OBUF)

(DELAY

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE u_ibufg)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE fpga_clk\/IFF\/IMUX)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

(CELL (CELLTYPE "X_LUT4")

(INSTANCE u_lut5)

(DELAY

(ABSOLUTE

(PORT ADR0 ( ))

(PORT ADR2 ( ))

(PORT ADR3 ( ))

(IOPATH ADR0 O ( ))

(IOPATH ADR1 O ( ))

(IOPATH ADR2 O ( ))

(IOPATH ADR3 O ( ))

)

)

)

(CELL (CELLTYPE "X_LUT4")

(INSTANCE u_lut3)

(DELAY

(ABSOLUTE

(PORT ADR1 ( ))

(PORT ADR2 ( ))

(PORT ADR3 ( ))

(IOPATH ADR0 O ( ))

(IOPATH ADR1 O ( ))

(IOPATH ADR2 O ( ))

(IOPATH ADR3 O ( ))

)

)

)

(CELL (CELLTYPE "X_LUT4")

(INSTANCE u_lut1)

(DELAY

(ABSOLUTE

(PORT ADR0 ( ))

(PORT ADR2 ( ))

(PORT ADR3 ( ))

(IOPATH ADR0 O ( ))

(IOPATH ADR1 O ( ))

(IOPATH ADR2 O ( ))

(IOPATH ADR3 O ( ))

)

)

)

(CELL (CELLTYPE "X_BUF")

(INSTANCE clkout\/OUTPUT\/OFF\/OMUX)

(DELAY

(PATHPULSE ())

(ABSOLUTE

(IOPATH I O ( ))

)

)

)

)

顶层仿真文件

`timescale 1ns / 1ps

module tb_dly;

reg clk_in;

reg [:] sel_in;

wire clk_out;

lut_dly uut(

.fpga_clk (clk_in ),

.config_in (sel_in ),

.clkout(clk_out)

); initial

begin

clk_in =; #

sel_in = 'd32;

#

sel_in = 'd16;

#

sel_in = 'd8;

#

sel_in = 'd4;

#

sel_in = 'd2;

#

sel_in = 'd1; end always #(/) clk_in <= ~clk_in;

endmodule

do文件

vlib work

vlog +acc tb_dly.v vlog +acc lut_dly_timesim.v

vlog +acc C:/Xilinx/ISE/verilog/src/glbl.v

vsim -novopt -t 1ps -L UNISIMS_VER -L UNIMACRO_VER -L UNI9000_VER -L SIMPRIMS_VER -L XILINXCORELIB_VER -L SECUREIP -L AIM_VER -L CPLD_VER -L UNISIM -L UNIMACRO -L SIMPRIM -L XILINXCORELIB -L AIM -L PLS -L CPLD -lib work tb_dly glbl

log -r /*

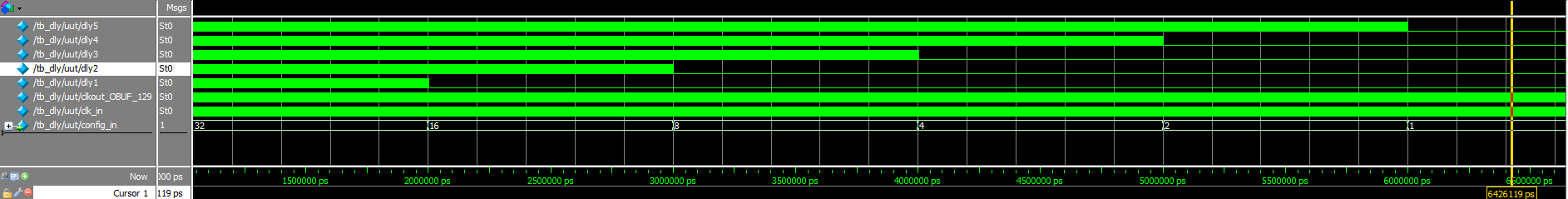

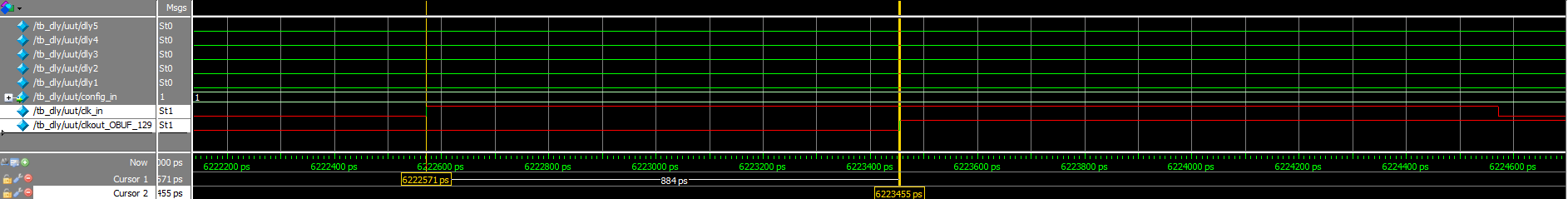

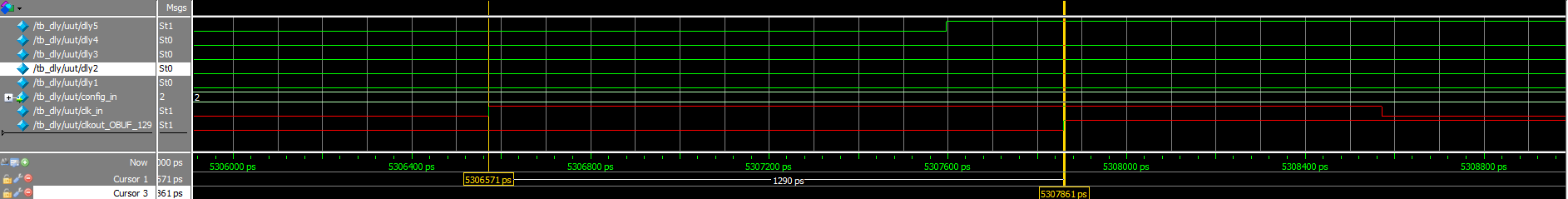

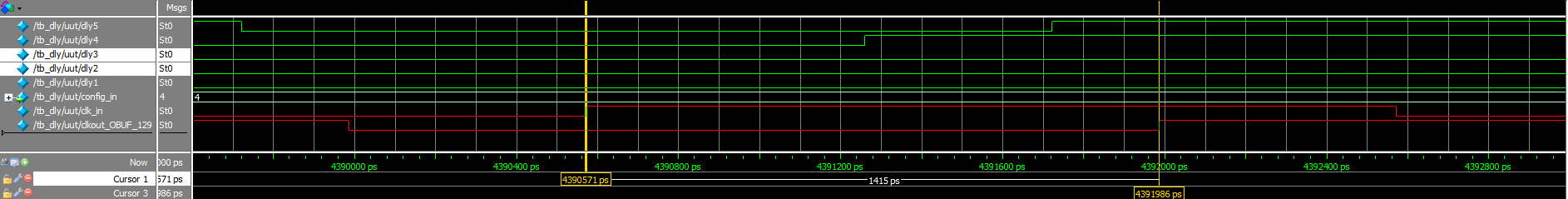

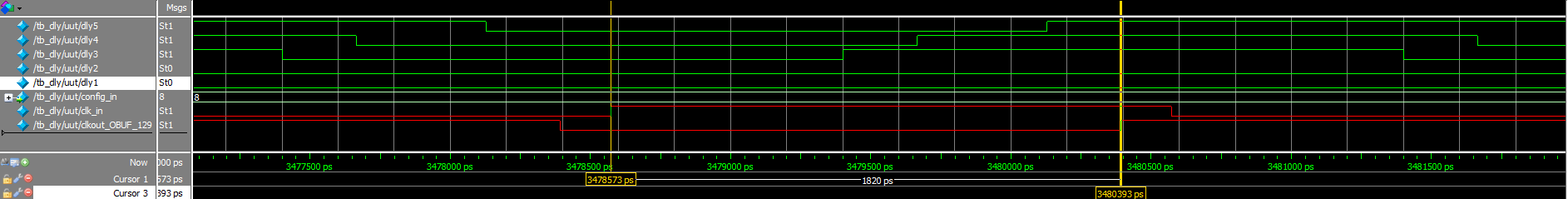

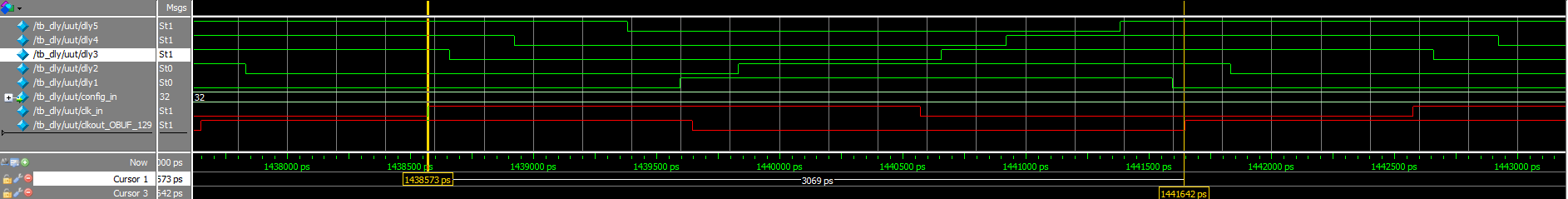

Modelsim仿真波形如下

[原创]Modelsim后仿真的更多相关文章

- ISE联合modelsim功能仿真和综合后仿真1

1.代码输入 (1).新建一个ISE工程,名字为count4. (2).新建一个verilog文件 (3).选择verilog module 输入file name为count4,单击next默认知道 ...

- ISE联合modelsim功能仿真和综合后仿真

1.代码输入 (1).新建一个ISE工程,名字为count4. (2).新建一个verilog文件 (3).选择verilog module 输入file name为count4,单击next默认知道 ...

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

- 【转】Quartus II调用modelsim无缝仿真

Quartus II调用modelsim无缝仿真 ★emouse 思·睿博客文章★ 原创文章转载请注明:http://emouse.cnblogs.com 本篇文章为转载,写的不错,最近在学mode ...

- ISE和Modelsim联合仿真(转)

相信很多人会遇到过这个问题,不知如何让ISE调用Modelsim进行仿真.我也迷糊了不少时间,查查找找,终于弄明白了,所以有了本文,和大家分享一下.我尽量讲得详细点儿,多多上图. 我的环境:Windo ...

- 基于脚本的modelsim自动化仿真笔记

这里记录一下基于脚本的modelsim自动化仿真的一些知识和模板,以后忘记了可以到这里查找.转载请标明出处:http://www.cnblogs.com/IClearner/ . 一.基本介绍 这里介 ...

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- Viavdo&ISE&Quartus II级联Modelsim级联仿真

博主一直致力寻找高效的工作方式,所以一直喜欢折腾软件,从刚开始只用软件IDE自带的编辑器,到Notepad++,再到后来的Vim,从用ISE14.7自带的Isim仿真,到发现更好的Modelsim,再 ...

- 搭建Modelsim SE仿真环境-使用do文件仿真

本章我们介绍仿真环境搭建是基于Modelsim SE的.Modelsim有很多版本,比如说Modelsim-Altera,但是笔者还是建议大家使用Modelsim-SE,Modelsim-Altera ...

随机推荐

- 使用apidoc生成项目文档

[1]npm install apidoc -g 全局安装apidoc [2]apidoc -v 查看是否安装成功 [3]apidoc.json apidoc的项目级配置文件,它必须位于整个工程目录顶 ...

- 【dp】摘花生

[题目描述] Hello Kitty想摘点花生送给她喜欢的米老鼠.她来到一片有网格状道路的矩形花生地(如下图),从西北角进去,东南角出来.地里每个道路的交叉点上都有种着一株花生苗,上面有若干颗花生,经 ...

- 【caffe】caffe在linux环境下的安装与编译

网上的caffe的安装教程繁杂而散乱,对初学者很不友好,尤其对该框架理解不深的童鞋.总的来说,caffe的安装不外乎几个固定的步骤,对每一步有了一定的理解,安装只是time-consuming的问题! ...

- Mac新手入门使用教程 - Finder 技巧

1,了解MAC电脑桌面. Finder:中间DOCK栏下最左边蓝白相间的图标. DOCK栏:包括Finder.前往应用程序.创建所有应用程序的快捷方式(google浏览器等).系统偏好设置.堆栈. ...

- 在线批量修改mysql中表结构

在线批量修改mysql中表结构 1.获取要修改的表的表名称登录mysql库,查询出所有表 show tables; 将需要修改表结构的表名称存放到b.txt文件中2.执行修改修改表引擎为InnoDB ...

- Hadoop记录-queue使用率

#!/bin/sh ip=xxx port=8088 export HADOOP_HOME=/app/hadoop/bin rmstate1=$($HADOOP_HOME/yarn rmadmin - ...

- Hadoop记录-切换NN

一.第一种方法 重启namenode(1.1.1.1 1.1.1.2)重启standby节点:1.1hadoop-daemon.sh stop zkfchadoop-daemon.sh stop na ...

- 【小白学Lua】之Lua变长参数和unpack函数

一.简介 Lua的变长参数和unpack函数在实际的开发中应用的还挺多的,比如在设计print函数的时候,需要支持对多个变量进行打印输出,这时我们就需要用到Lua中的变长参数和unpack函数了. 二 ...

- java连接jdbc

package com.dy.util; import java.sql.Connection; import java.sql.DriverManager; import java.sql.SQLE ...

- java 格式化字符串

Date 格式转化为字符串 SimpleDateFormat sdf=new SimpleDateFormat("yyyy-MM-dd"); java.util.Date date ...