DDR3(2):初始化

调取 DDR3 IP核后,是不能直接进行读写测试的,必须先进行初始化操作,对 IP 核进行校验。本篇采用 Modelsim 软件配合 DDR3 IP核生成的仿真模型,搭建出 IP核的初始化过程。

一、顶层文件

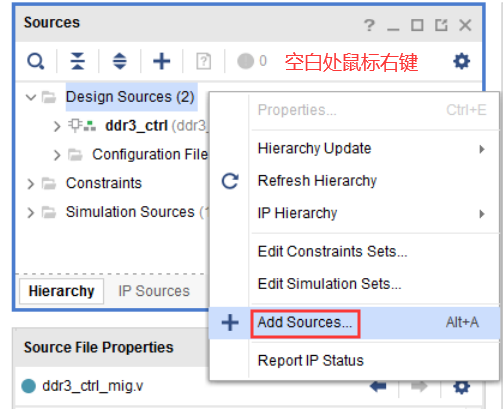

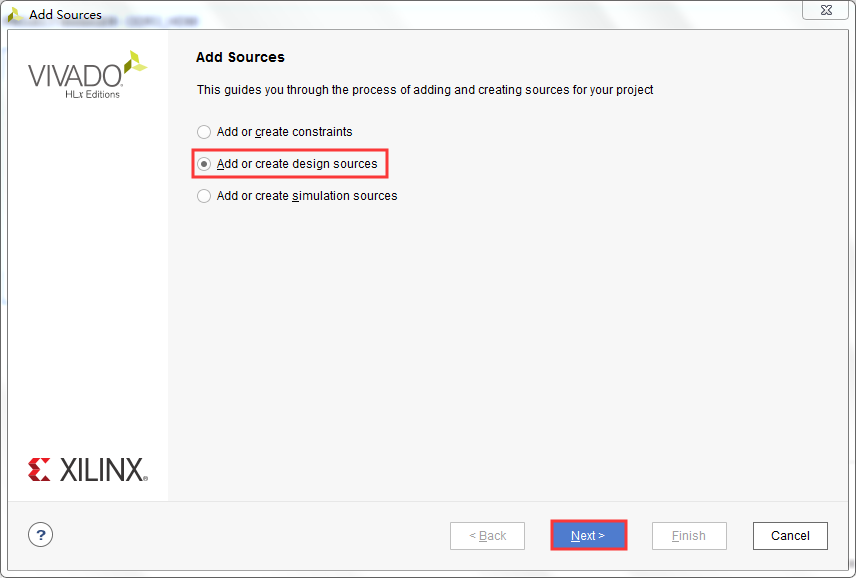

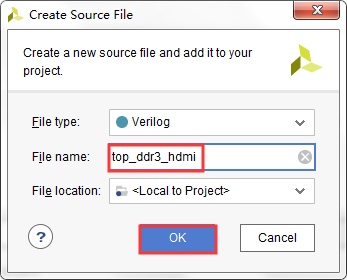

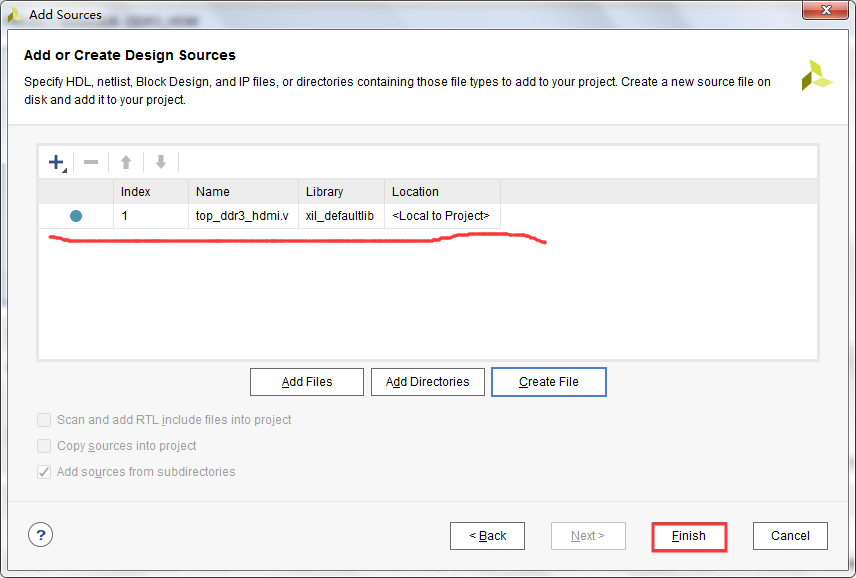

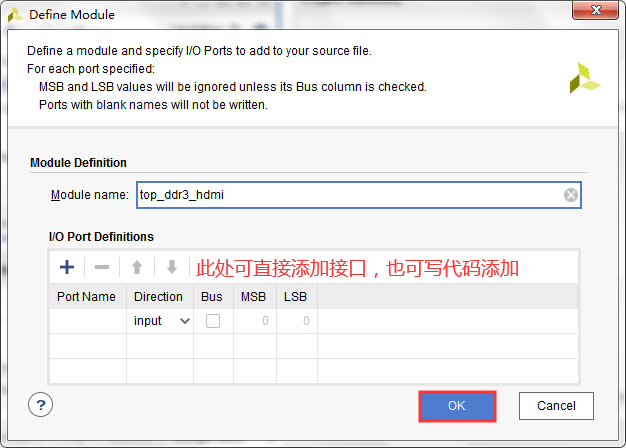

1、生成 DDR3 IP 核后,在 Source 界面空白处右键点击 Add Source,添加顶层文件。

2、在 DDR3_HDMI\DDR3_HDMI.srcs\sources_1\ip\ddr3_ctrl\ddr3_ctrl\user_design\rtl\ddr3_ctrl.v 可得到 top_ddr3_hdmi 需要的输入输出端口,将其复制过来。

//========================< 端口 >==========================================

(

//system ----------------------------------------

input wire sclkin , //50Mhz

input wire srst_n , //复位,低电平有效

//DDR3 ------------------------------------------

inout wire [:] ddr3_dq ,

inout wire [ :] ddr3_dqs_n ,

inout wire [ :] ddr3_dqs_p ,

output wire [:] ddr3_addr ,

output wire [ :] ddr3_ba ,

output wire ddr3_ras_n ,

output wire ddr3_cas_n ,

output wire ddr3_we_n ,

output wire ddr3_reset_n ,

output wire [ :] ddr3_ck_p ,

output wire [ :] ddr3_ck_n ,

output wire [ :] ddr3_cke ,

output wire [ :] ddr3_cs_n ,

output wire [ :] ddr3_dm ,

output wire [ :] ddr3_odt

);

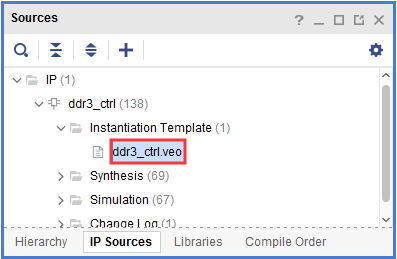

3、对顶层模块进行编写,可以进入 IP Source 的 ddr3_ctrl.veo文件找到接口复制过来例化,并根据需求更改部分信号,仿真时希望app接口不工作,所有输入接口连接为 0

//DDR3_IP核 -----------------------------------------------------------------

ddr3_ctrl u_ddr3_ctrl //输入为200Mhz,芯片需400Mhz,内部速率为4:1 = 100Mhz

(

// Memory interface ports ----------------------------------------

.ddr3_addr (ddr3_addr ), // output [13:0]

.ddr3_ba (ddr3_ba ), // output [ 2:0]

.ddr3_cas_n (ddr3_cas_n ), // output

.ddr3_ck_n (ddr3_ck_n ), // output

.ddr3_ck_p (ddr3_ck_p ), // output

.ddr3_cke (ddr3_cke ), // output

.ddr3_ras_n (ddr3_ras_n ), // output

.ddr3_reset_n (ddr3_reset_n ), // output

.ddr3_we_n (ddr3_we_n ), // output

.ddr3_dq (ddr3_dq ), // inout [15:0]

.ddr3_dqs_n (ddr3_dqs_n ), // inout [ 1:0]

.ddr3_dqs_p (ddr3_dqs_p ), // inout [ 1:0]

.init_calib_complete (init_calib_complete ), // output

.ddr3_cs_n (ddr3_cs_n ), // output

.ddr3_dm (ddr3_dm ), // output [ 1:0]

.ddr3_odt (ddr3_odt ), // output

// Application interface ports -----------------------------------

.app_addr ( ), // input [27:0]

.app_cmd ( ), // input [ 2:0]

.app_en ( ), // input

.app_wdf_data ( ), // input [127:0]

.app_wdf_end ( ), // input

.app_wdf_wren ( ), // input

.app_rd_data ( ), // output [127:0]

.app_rd_data_end ( ), // output

.app_rd_data_valid ( ), // output

.app_rdy ( ), // output

.app_wdf_rdy ( ), // output

.app_sr_req ( ), // input

.app_ref_req ( ), // input

.app_zq_req ( ), // input

.app_sr_active ( ), // output

.app_ref_ack ( ), // output

.app_zq_ack ( ), // output

.ui_clk ( ), // output 100Mhz

.ui_clk_sync_rst ( ), // output

.app_wdf_mask ( ), // input [15:0]

// System Clock Ports --------------------------------------------

.sys_clk_i (sysclk ), // input 200Mhz

.sys_rst (srst_n ) // input 系统复位

);

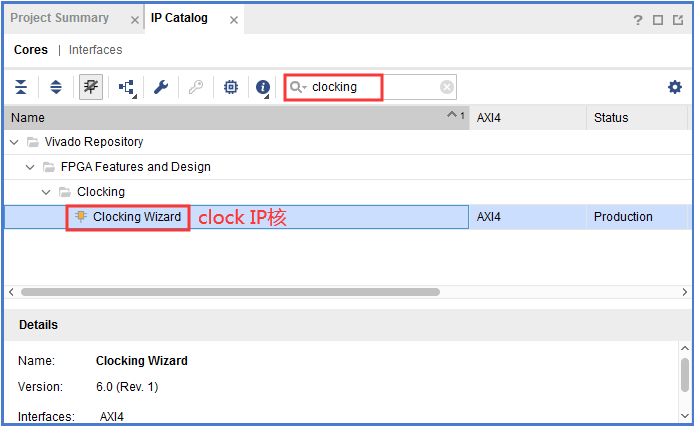

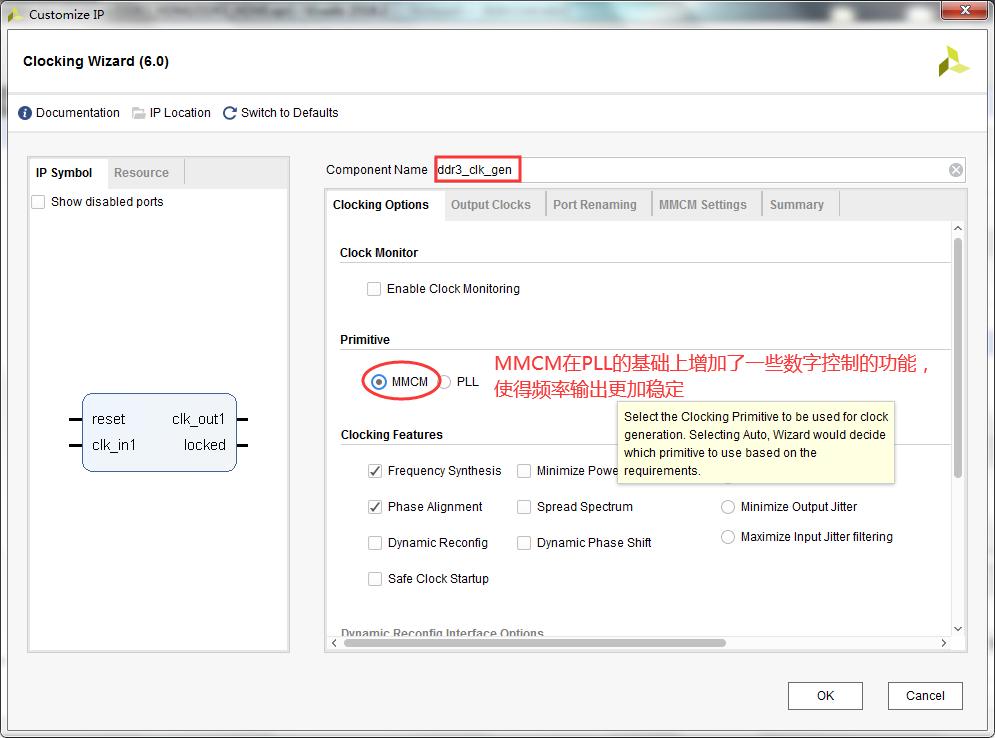

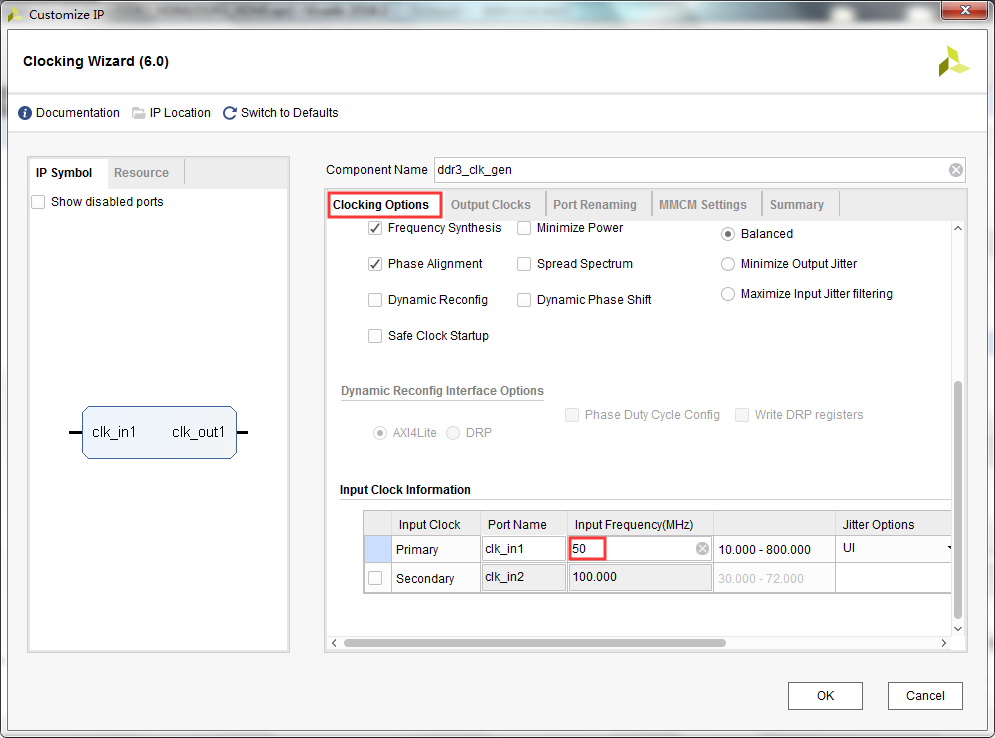

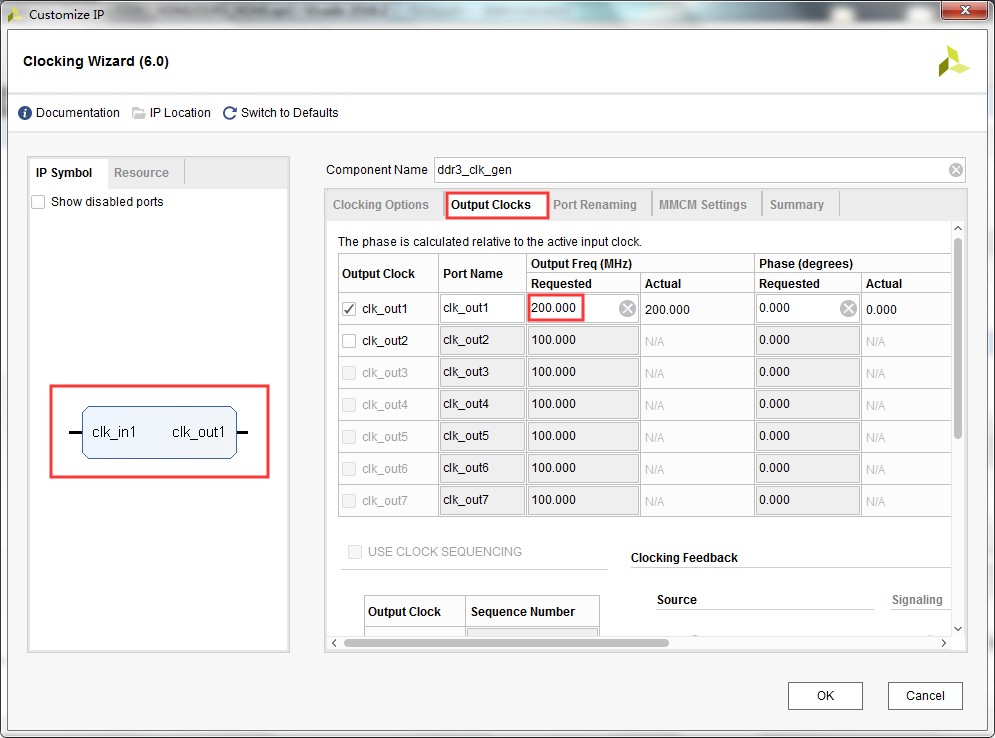

4、调取 DDR3 IP 核时,选择了对此 IP 核输入一个200 Mhz 的时钟,由于板卡晶振生成的时钟为 50Mhz,所以还得用一个 IP 核来生出 200 Mhz 时钟。

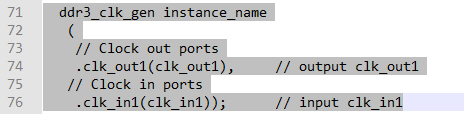

5、生成时钟后同样找到 .veo 文件接口复制过来例化。

//时钟_IP核 ----------------------------------------------------------------

ddr3_clk_gen u_ddr3_clk_gen

(

.clk_in1 (sclkin ), // input clk_in1

.clk_out1 (sysclk ) // output clk_out1

);

7、有几个信号是我们需要观察的,用 wire 引出来吧。

//========================< 连线 >==========================================

//PLL -------------------------------------------

wire sysclk ;

// ddr3 ip --------------------------------------

wire app_rdy ;

wire app_wdf_rdy ;

wire app_en ;

wire [:] app_addr ;

wire [ :] app_cmd ;

wire [:] app_wdf_mask ;

wire app_wdf_wren ;

wire [:] app_wdf_data ;

wire app_wdf_end ;

wire [:] app_rd_data ;

wire app_rd_data_valid ;

wire app_rd_data_end ;

wire ui_clk ;

wire ui_clk_sync_rst ;

wire init_calib_complete ;

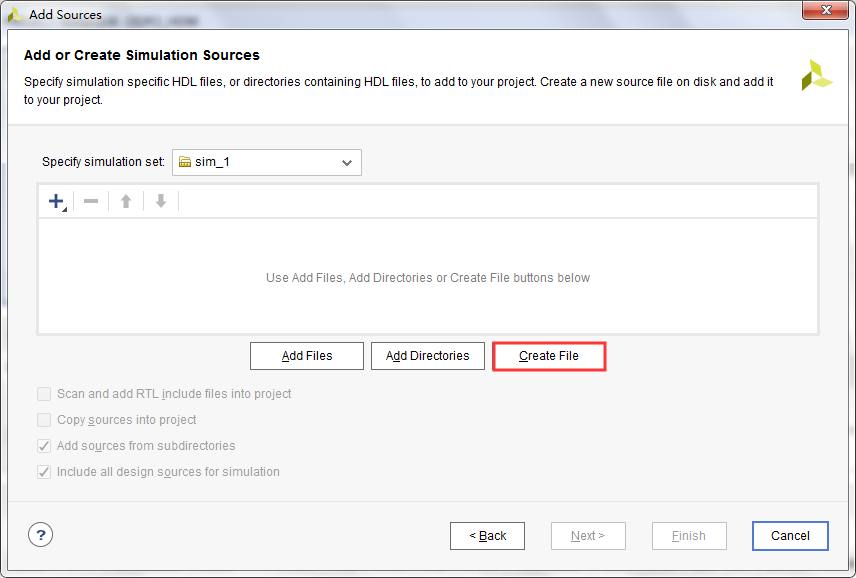

二、测试文件

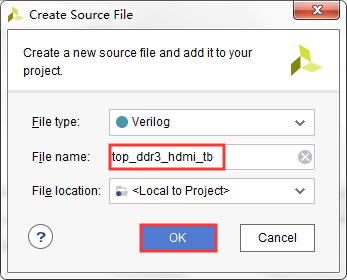

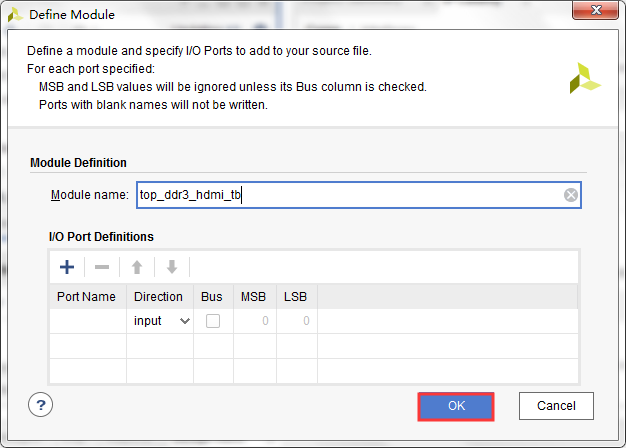

1、在 Simulation Sources 右键选择 Add Sources,创建 testbench 文件。

2、首先还是把输入输出接口和 top 模块接口在 testbench 中写好。

`timescale 1ns/1ps //时间精度

`define Clock //时钟周期 module top_ddr3_hdmi_tb;

//========================< 端口 >==========================================

reg clk ;

reg rst_n ;

wire [:] ddr3_dq ;

wire [ :] ddr3_dqs_n ;

wire [ :] ddr3_dqs_p ;

wire [:] ddr3_addr ;

wire [ :] ddr3_ba ;

wire ddr3_ras_n ;

wire ddr3_cas_n ;

wire ddr3_we_n ;

wire ddr3_reset_n ;

wire [ :] ddr3_ck_p ;

wire [ :] ddr3_ck_n ;

wire [ :] ddr3_cke ;

wire [ :] ddr3_cs_n ;

wire [ :] ddr3_dm ;

wire [ :] ddr3_odt ; //==========================================================================

//== 模块例化

//==========================================================================

//顶层模块

top_ddr3_hdmi u_top_ddr3_hdmi

(

.ddr3_dq (ddr3_dq ),

.ddr3_dqs_n (ddr3_dqs_n ),

.ddr3_dqs_p (ddr3_dqs_p ),

.ddr3_addr (ddr3_addr ),

.ddr3_ba (ddr3_ba ),

.ddr3_ras_n (ddr3_ras_n ),

.ddr3_cas_n (ddr3_cas_n ),

.ddr3_we_n (ddr3_we_n ),

.ddr3_reset_n (ddr3_reset_n ),

.ddr3_ck_p (ddr3_ck_p ),

.ddr3_ck_n (ddr3_ck_n ),

.ddr3_cke (ddr3_cke ),

.ddr3_cs_n (ddr3_cs_n ),

.ddr3_dm (ddr3_dm ),

.ddr3_odt (ddr3_odt ),

.sclkin (clk ),

.srst_n (rst_n )

);

3、DDR3 控制器非常复杂,手写 testbench 是非常困难的。我们上一讲调取 DDR3 IP 核时说过,它已经生成了仿真模型供我们测试。位置在 DDR3_HDMI\DDR3_HDMI.srcs\sources_1\ip\ddr3_ctrl\ddr3_ctrl\example_design\sim,ddr3_model.sv 和 ddr3_model_parameters.vh 即是我们需要的仿真模型,将其复制到 DDR3_HDMI\DDR3_HDMI.srcs\sim_1\new 中,和 top_ddr3_hdmi_tb 文件放在一起。此外还可以看到刚刚那个文件夹中有一个 sim_tb_top 文件,打开它翻到500多行,即可看到该仿真模型的接口模块,我们将其复制到 testbench 中,并根据此次设计情况,更改部分参数。

//仿真模型

ddr3_model u_ddr3_model

(

.rst_n (ddr3_reset_n ),

.ck (ddr3_ck_p ),

.ck_n (ddr3_ck_n ),

.cke (ddr3_cke ),

.cs_n (ddr3_cs_n ),

.ras_n (ddr3_ras_n ),

.cas_n (ddr3_cas_n ),

.we_n (ddr3_we_n ),

.dm_tdqs ({ddr3_dm[],ddr3_dm[]} ), //ddr3_dm为2位

.ba (ddr3_ba ),

.addr (ddr3_addr ),

.dq (ddr3_dq[:] ), //ddr3_dq为16位

.dqs ({ddr3_dqs_p[],ddr3_dqs_p[]} ), //ddr3_dqs_p为2位

.dqs_n ({ddr3_dqs_n[],ddr3_dqs_n[]} ), //ddr3_dqs_n为2位

.tdqs_n ( ),

.odt (ddr3_odt )

);

3、此外还需要产生一个 50 Mhz 时钟和低电平有效的复位信号。

//==========================================================================

//== 时钟信号和复位信号

//==========================================================================

initial begin

clk = ;

forever

#(`Clock/) clk = ~clk;

end initial begin

rst_n = ; #(`Clock*+);

rst_n = ;

end

4、回到 Vivado,发现仿真模型文件已经出现了,但是处于问号状态,我们选中它,右键 Add Sources,将 ddr3_model.sv 和 ddr3_model_parameters.vh 添加进来即可。

三、启动 Modelsim 验证 DDR3 IP核

1、使用 Modelsim 进行仿真前,需要先编译 Vivado 和 Modelsim 之间的关联库,具体步骤请另行搜索。

2、点击 Vivado 的 Setting 进行设置,Target simulator 选择 ModelSim Simulator,仿真顶层文件选择第二步的仿真文件,仿真库则自动定位好了。

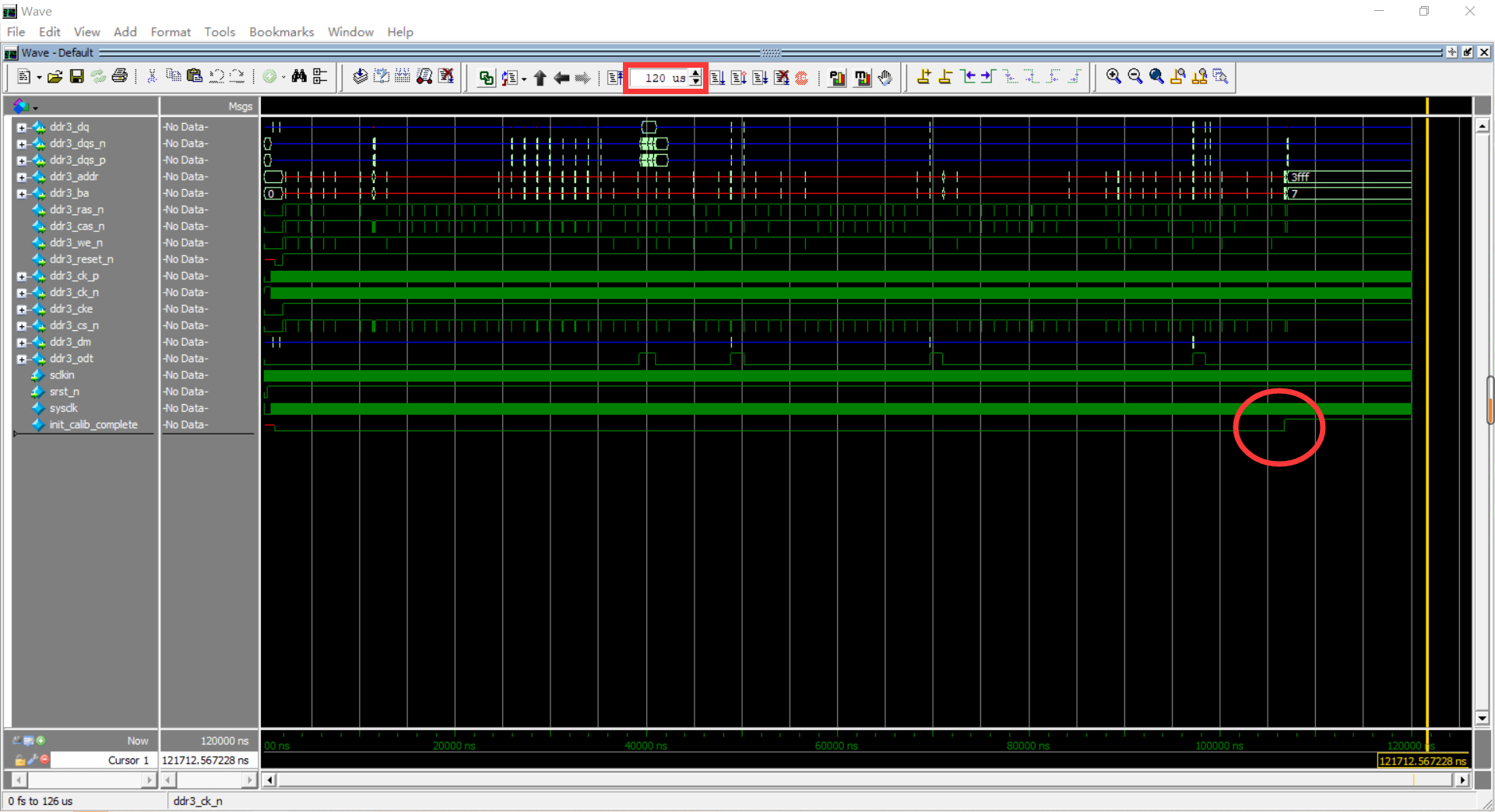

3、点击 Vivado 左侧菜单 Run Simulation --- Run Behavioral Simulation,Modelsim 就自动打开仿真了。

4、选取信号,跑一段时间,可以看到时钟信号和复位信号正常, init_calib_complete 信号在拉低一段时间后拉高,表面本次 DDR3 IP核验证成功。

以上。

参考资料:威三学院FPGA教程

DDR3(2):初始化的更多相关文章

- DDR3内存详解,存储器结构+时序+初始化过程

DDR3内存详解,存储器结构+时序+初始化过程 标签: DDR3存储器博客 2017-06-17 16:10 1943人阅读 评论(1) 收藏 举报 分类: 硬件开发基础(2) 转自:http:/ ...

- DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)

转自:http://www.360doc.com/content/14/0116/16/15528092_345730642.shtml 以及参考网络. 首先,我们先了解一下内存的大体结构工作流程,这 ...

- 【转】DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)

这两天正在学习FPGA如何控制DDR3的读写,找到一篇个人感觉比较有意义的文章,可以对DDR的内部结构有一个初步的了解.原文出处:http://blog.chinaunix.net/uid-28458 ...

- 【接口时序】8、DDR3驱动原理与FPGA实现(一、DDR的基本原理)

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:无 3.仿真工具:无 硬件平台: 1. FPGA型号:无 2. DDR3型号:无 二. 存储器的分类 存储器一 ...

- [求助] 关于DDR3的读写操作,看看我的流程对吗?

[求助] 关于DDR3的读写操作,看看我的流程对吗? 最近简单调了一下KC705开发板上面的DDR3,型号是MT8JTF12864HZ-1G6:有时候加载程序后,发现读出数据不是写进去的,在这将我的操 ...

- DDR3内存技术原理

随着AMD AM2平台CPU的上市,目前两大处理器巨头均提供了对DDR2内存的支持.不过,DDR2远不是内存技术发展的终点,CPU和内存厂商已经在着手进行DDR3内存的相应准备.DDR2内存的好日子还 ...

- DDR中的一些知识点说明(ODT,ZQ校准,OCT,TDQS)

ODT ( On-DieTermination ,片内终结)ODT 也是 DDR2 相对于 DDR1 的关键技术突破,所谓的终结(端接),就是让信号被电路的终端吸 收掉,而不会在电路上形成反射, 造成 ...

- 各个DDR对比

一.容量和封装相关 (1)逻辑Bank数量增加 DDR2 SDRAM中有4Bank和8Bank的设计,而DDR3起始的逻辑Bank是8个,另外还为未来的16个逻辑Bank做好了准备. (2)封装(Pa ...

- 转:DDR原理详解

首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其中所起到的作用.这部分的讲述运用DDR3的简化时序图. DDR3的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格 ...

- tiny4412 裸机程序 七、重定位代码到DRAM【转】

本文转载自:http://blog.csdn.net/eshing/article/details/37116637 一.关于DRAM 上一章我们讲解了如何对代码进行重定位,但是将代码重定位到只有25 ...

随机推荐

- 精益车间管理如何实现?让APS排程系统来帮忙

精益制造是企业全面的文化改变,它的主要目标是消灭任何形式的浪费.最明显的例子是在生产区域堆积的物料.在制品.等待客户来买的成品.它还可能包括员工不必的移动和不增值的许多流程,目标是在最小的库存,最短的 ...

- 盘点当下大热的7大Github机器学习创新项目

哪个平台有最新的机器学习发展现状和最先进的代码?没错——Github!本文将会分享近期发布的七大GitHub机器学习项目.这些项目广泛覆盖了机器学习的各个领域,包括自然语言处理(NLP).计算机视觉. ...

- NPOI.dll 在哪里?

一.问题 NPOI下载后找不到网上人家说的几个DLL https://bbs.csdn.net/topics/392510552 二.答案: 1.VS2015引用NPOI2.4.1和NuGet的安装方 ...

- 使用Deployment控制器创建Pods并使Service发布到外网可访问

由于NFS支持节点共同读取及写入,所以可使用Deployment控制器创建多个Pod,并且每一个Pod都共享同一个目录 k8s-master kubnet@hadoop2 volumes]$ vim ...

- Elasticsearch+x-pack认证license过期处理

介绍: x-pack是Elasticsearch中的一个plugin,主要功能是实现认证功能 报错: 类似下面这样的报错,是因为licese过期导致的 解决: 1.首先去Elasticsearch的官 ...

- Docker在Centos 7上的部署

Docker在Centos 7上的部署 方法1---开启centos 7上自带的 extras YUM源,然后 yum install docker来安装 安装前必须保证 Linux Kernel ...

- 团队第四次作业:alpha1发布成绩汇总

一.作业题目 团队第四次作业:alpha1发布 二.作业评分标准 博客评分规则(总分100)博客要求 给出开头和团队成员列表(10') 给出发布地址以及安装手册(20') 给出测试报告(40') 给出 ...

- Codeforces E. High Load(构造)

题目描述: High Load time limit per test 2 seconds memory limit per test 512 megabytes input standard inp ...

- django+sqlite进行web开发(二)

模板 前面的例子中,我们是直接将HTML写在了Python代码中,这种写法并不可取.我们需要使用模板技术将页面设计和Python代码分离. 模板通常用于产生HTML,但是Django的模板也能产生任何 ...

- django cookie,session,auth

一.最完美的auth auth_user 是用来存储的用户注册的username,password auth 首先需要引入模块 from django.contrib import auth 用户认证 ...