[I2C].I2C总线详解

转自:https://www.cnblogs.com/BitArt/archive/2013/05/27/3101037.html

一. 基本信息

1. 概述

I²C 是Inter-Integrated Circuit的缩写,发音为"eye-squared cee" or "eye-two-cee" , 它是一种两线接口。

I²C 只是用两条双向的线,一条 Serial Data Line (SDA) ,另一条Serial Clock (SCL),也因为有clk同步,所以是个同步总线,又因为只有一根数据线,要么主发从收,要么主收从发,所以是一个半双工总线。

SCL:上升沿将数据输入到每个I2C接口的EEPROM器件中;下降沿驱动EEPROM器件输出数据。(边沿触发)SDA:双向数据线,为OD门,与其它任意数量的OD与OC门成"线与"关系。

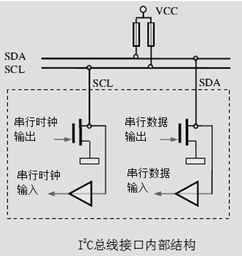

2. 输出级

每一个I2C总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。其中输出为漏极开路的场效应管,输入缓冲为一只高输入阻抗的同相器,这种电路具有两个特点:1)由于SDA、SCL为漏极开路结构(OD),因此它们必须接有上拉电阻,阻值的大小常为 1k8, 4k7 and 10k ,但1k8 时性能最好;当总线空闲时,两根线均为高电平。连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件的SDA及SCL都是线"与"关系。2)引脚在输出信号的同时还将引脚上的电平进行检测,检测是否与刚才输出一致,为"时钟同步"和"总线仲裁"提供了硬件基础(原理???)。

每一个I2C总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。其中输出为漏极开路的场效应管,输入缓冲为一只高输入阻抗的同相器,这种电路具有两个特点:1)由于SDA、SCL为漏极开路结构(OD),因此它们必须接有上拉电阻,阻值的大小常为 1k8, 4k7 and 10k ,但1k8 时性能最好;当总线空闲时,两根线均为高电平。连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件的SDA及SCL都是线"与"关系。2)引脚在输出信号的同时还将引脚上的电平进行检测,检测是否与刚才输出一致,为"时钟同步"和"总线仲裁"提供了硬件基础(原理???)。

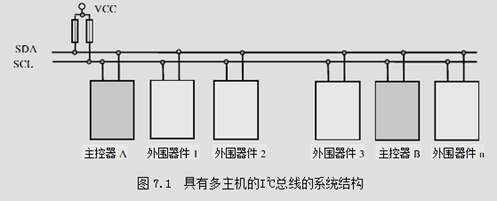

3. 主设备与从设备

系统中的所有外围器件都具有一个7位的"从器件专用地址码",其中高4位为器件类型,由生产厂家制定,低3位为器件引脚定义地址,由使用者定义。在使用中,地址字节中,还有1bit代表当前是读还是写。主控器件通过地址码建立多机通信的机制,因此I2C总线省去了外围器件的片选线,这样无论总线上挂接多少个器件,其系统仍然为简约的二线结构(区别于SPI, SPI也可以挂载多个,但是通过cs片选)。终端挂载在总线上,有主端和从端之分,主端必须是带有CPU的逻辑模块,在同一总线上同一时刻使能有一个主端,可以有多个从端,从端的数量受地址空间和总线的最大电容 400pF的限制。

- 主端主要用来驱动SCL line, 即clock由主发出;

- 从设备对主设备产生响应;

二者都可以传输数据,但是从设备不能发起传输,且传输是受到主设备控制的(I2C从设备不可以主动发数据,必须主发起,和485并不相同,485是可以通过协议实现从主动上报,常规I2C会这么设计吗???)。

4. 速率:

普通模式:100kHz;

快速模式:400kHz;

高速模式:3.4MHz;

没有任何必要使用高速SCL,将SCL保持在100k或以下,然后忘了它吧。

二.协议

1.空闲状态

I2C总线总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

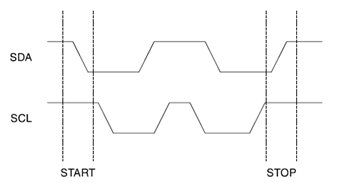

2.起始位与停止位的定义

- 起始信号:当SCL为高期间,SDA由高到低的跳变;启动信号是一种电平跳变时序信号(边沿),而不是一个电平信号。

- 停止信号:当SCL为高期间,SDA由低到高的跳变;停止信号也是一种电平跳变时序信号(边沿),而不是一个电平信号。

3.ACK

3.ACK

3. I2C的ACK和NACK机制

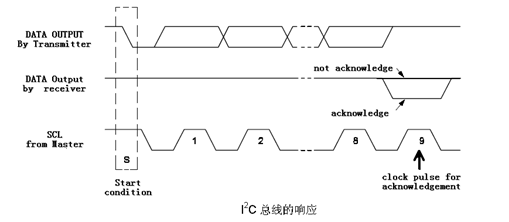

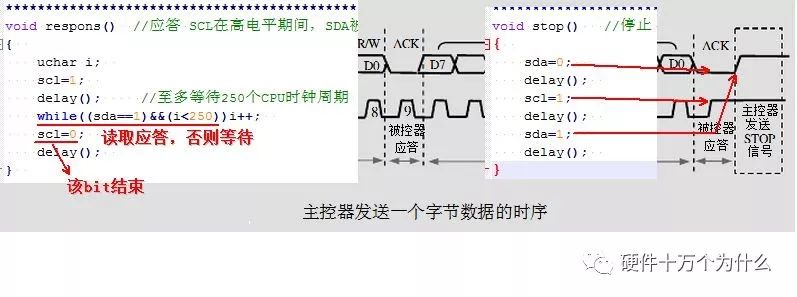

从设备在完整收到主设备的一个字节后,从设备拉低1bit的SDA数据线,通知主设备成功接收,即ACK。

发送器每发送一个字节,就在时钟脉冲9期间释放数据线,由接收器反馈一个应答信号,主的每个字节,从都对应有ACK或者NACK。 应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节;应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。 对于反馈有效应答位ACK的要求是,接收器在第9个时钟脉冲之前的低电平期间将SDA线拉低,并且确保在该时钟的高电平期间为稳定的低电平。 如果接收器是主控器,则在它收到最后一个字节后,发送一个NACK信号,以通知被控发送器结束数据发送,并释放SDA线,以便主控接收器发送一个停止信号P。

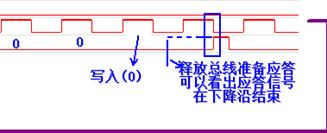

如下图逻辑分析仪的采样结果:释放总线后,如果没有应答信号,sda应该一直持续为高电平,但是如图中蓝色虚线部分所示,它被拉低为低电平,证明收到了应答信号。

这里面给我们的两个信息是:1)接收器在SCL的上升沿到来之前的低电平期间拉低SDA;2)应答信号一直保持到SCL的下降沿结束;正如前文红色标识所指出的那样。

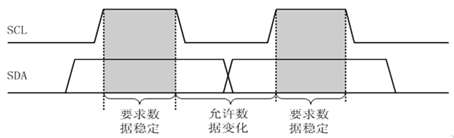

4.数据的有效性

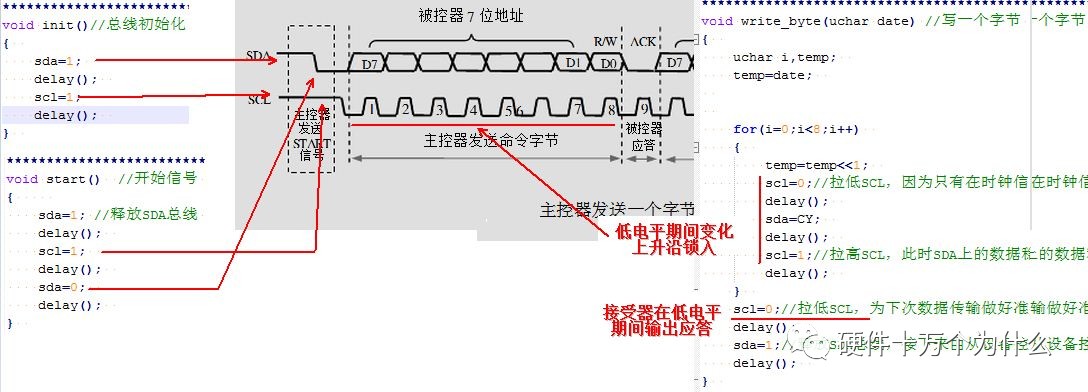

I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定(即clock高电平为采样时间),只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

我的理解:虽然只要求在高电平期间保持稳定,但是要有一个提前量,也就是数据在SCL的上升沿到来之前就需准备好,因为在前面I2C总线之(一)---概述一文中已经指出,数据是在SCL的上升沿打入到器件(EEPROM)中的。

5.数据的传送

在I2C总线上传送的每一位数据都有一个时钟脉冲相对应(或同步控制),即在SCL串行时钟的配合下,在SDA上逐位地串行传送每一位数据。数据位的传输是边沿触发。

三.工作过程

总线上的所有通信都是由主控器引发的。在一次通信中,主控器与被控器总是在扮演着两种不同的角色。

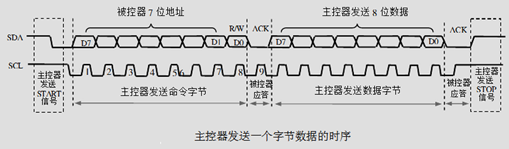

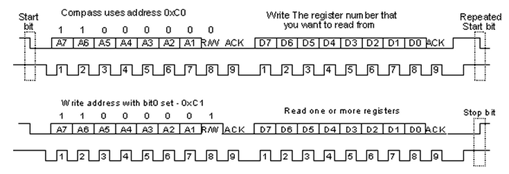

I2C的从机地址为7bit,剩余的一个bit代表本次是读还是写

如下面的写和读示例,能看出来,特别是读的时候,主先把从机地址+writebit+读寄存器地址发出去,然后再发出从机地址+readbit,最后等待接收;写的话直接从机地址+writebit+Data就可以。

1.主设备写入数据

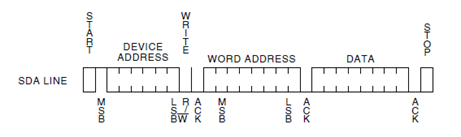

主设备发送起始位,这会通知总线上的所有设备传输开始了,接下来主机发送设备地址,与这一地址匹配的slave将继续这一传输过程,而其它slave将会忽略接下来的传输并等待下一次传输的开始(从器件属性来看,非地址器件丢掉其他数据包)。主设备寻址到从设备后,发送它所要读取或写入的从设备的内部寄存器地址; 之后,发送数据。数据发送完毕后,发送停止位:

I2C接口EEPROM写入过程如下:

- 发送起始位

- 发送从设备的地址+读/写选择位,从机ACK

- 发送想要写入的内部寄存器地址,从机ACK

- 发送数据,从机ACK

- 发送停止位

- 从设备收到停止信号后,进入到一个内部的写入周期,大概需要10ms(看来EEPROM的10ms是业内通用的???),此间任何操作都不会被从设备(如EEPROM)响应;(因此以这种方式的两次写入之间要插入一个延时,否则会导致失败,博主曾在这里小坑了一下)

详细:

需要说明的是:主控器通过发送地址码与对应的被控器建立了通信关系,而挂接在总线上的其它被控器虽然同时也收到了地址码,但因为与其自身的地址不相符合,因此提前退出与主控器的通信;

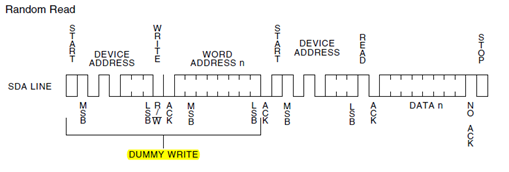

2.主控器读取数据

读的过程比较复杂,在从slave读出数据前,你必须先要告诉它哪个内部寄存器是你想要读取的,因此必须先对其进行写入(dummy write):

- 发送起始位

- 发送slave地址+write bit set,从机ACK

- 发送内部寄存器地址,从机ACK

- 重新发送起始位,即restart

- 重新发送slave地址+read bit set,从机ACK

- 读取数据,主机ACK

- 主机接收器在接收到最后一个字节后,也不会发出ACK信号。于是,从机发送器释放SDA线,以允许主机发出P信号结束传输。

- 发送停止位

详细:

为了加深对I2C总线的理解,用C语言模拟IIC总线,边看源代码边读波形:

如下图所示的写操作的时序图:

[I2C].I2C总线详解的更多相关文章

- I2C 基础原理详解

今天来学习下I2C通信~ I2C(Inter-Intergrated Circuit)指的是 IC(Intergrated Circuit)之间的(Inter) 通信方式.如上图所以有很多的周边设备都 ...

- 【转】AXI_Lite 总线详解

目录: · 1.前言 · 2.AXI总线与ZYNQ的关系 · 3 AXI 总线和 AXI 接口以及 AXI 协议 · 3.1 AXI 总线概述 · 3.2 AXI 接口介绍 ·3.3 AXI 协议概述 ...

- S02_CH12_ AXI_Lite 总线详解

S02_CH12_ AXI_Lite 总线详解 12.1前言 ZYNQ拥有ARM+FPGA这个神奇的架构,那么ARM和FPGA究竟是如何进行通信的呢?本章通过剖析AXI总线源码,来一探其中的秘密. 1 ...

- Linux设备驱动模型之platform(平台)总线详解

/********************************************************/ 内核版本:2.6.35.7 运行平台:三星s5pv210 /*********** ...

- [CAN].CAN总线详解

转自:https://blog.csdn.net/cheatscat/article/details/82886889 CAN(Controller Area Network)总线协议是由 BOSCH ...

- [LIN].LIN总线详解

转自:https://www.2cto.com/kf/201806/754227.html 参考:https://wenku.baidu.com/view/a9b08d786bd97f192379e9 ...

- [SDIO].SDIO总线详解

转自:https://blog.csdn.net/liuhan33025/article/details/51131848 SDIO接口是在SD内存卡接口的基础上发展起来的接口,SDIO接口兼容以前的 ...

- i2c总线,核心,驱动详解

Linux I2C驱动分析(一)----I2C架构和总线驱动 一.I2C总线原理 I2C是一种常用的串行总线,由串行数据线SDA 和串线时钟线SCL组成.I2C是一种多主机控制总线,它和USB总线不同 ...

- I2C总线驱动框架详解

一.I2C子系统总体架构 1.三大组成部分 (1)I2C核心(i2c-core):I2C核心提供了I2C总线驱动(适配器)和设备驱动的注册.注销方法,I2C通信方法(”algorithm”)上层的,与 ...

随机推荐

- Executors创建四种线程池

newCachedThreadPool创建一个可缓存线程池,如果线程池长度超过处理需要,可灵活回收空闲线程,若无可回收,则新建线程.newFixedThreadPool 创建一个定长线程池,可控制线程 ...

- 如何将本地jar包放入本地maven仓库和远程私服仓库

1.将本地jar包放入本地仓库.只需执行如下命令即可: mvn install:install-file -Dfile=D:/demo/fiber.jar -DgroupId=com.sure -Da ...

- 如何利用maven将本地jar包引入到工程之中

1.在个人开发模式下,可以将jar包放入项目的lib目录中,在pom.xml中做如下配置: <dependencies> <dependency> <groupId> ...

- mockito的用法

well,说来惭愧,之前一直知道有这么个东西,但总是看不进去.刚好趁着这次迭代间隙有些闲暇,认真看了下,大概明白是怎么回事了. 首先,mock是个概念,这个词的本意就是“虚假的”.“模仿的”.在测试的 ...

- ODAC 安裝 (11.2.4)

1.下载解压 下载ODCA 安装包,下载地址:http://www.oracle.com/technetwork/database/windows/downloads/index-090165.htm ...

- 你该怎么学习C++——思想层面

Javascript是世界上最受误解的语言,其实C++何尝不是.坊间流传的错误的C++学习方法一抓就是一大把.我自己在学习C++的过程中也走了许多弯路,浪费了不少时间. 为什么会存在这么多错误认识?原 ...

- nvarchar, varchar, nchar, char的差別

1. var,意思是可變動的,因為欄位長度可變動,所以會額外花費2Byte去儲存地址2. n,支援UNICODE UCS-2字元,因為萬國編碼(支援中文字),所以1字儲存2Byte nvarchar: ...

- IOS开发依赖管理工具CocoaPods

CocoaPods IOS开发依赖管理工具 CocoaPods is a dependency manager for Swift and Objective-C Cocoa projects. It ...

- IntelliJ IDEA重新打开后把字母隐藏怎么办

默认Font的字体melno不行,r会隐形 解决方案:更换idea字体,点击apply按钮即可正常显示 修改Font为的consoleas Size:16 line spacing:1.25

- LeetCode 394. 字符串解码(Decode String) 44

394. 字符串解码 394. Decode String 题目描述 给定一个经过编码的字符串,返回它解码后的字符串. 编码规则为: k[encoded_string],表示其中方括号内部的 enco ...