习题8 #第8章 Verilog有限状态机设计-2 #Verilog #Quartus #modelsim

2. 设计一个“1001”串行数据检测器,其输入、输出如下:

输入x:000 101 010 010 011 101 001 110 101

输出z:000 000 000 010 010 000 001 000 000

(1)设计思路:同前,规划状态,无它。

(2)1001序列检测电路源码:

1 //detect 1001

2 //2020-10-13

3 // by YongFengXie

4 module ex8_2(clk,rst_n,x,z);

5 input clk;

6 input rst_n;

7 input x;

8 output reg z;

9

10 reg [4:0] state;

11

12 parameter s0=5'b00001,

13 s1=5'b00010,

14 s2=5'b00100,

15 s3=5'b01000,

16 s4=5'b10000;

17

18 always @(posedge clk or negedge rst_n)

19 begin

20 if(!rst_n)

21 begin

22 state<=s0;

23 z<=1'b0;

24 end

25 else

26 case(state)

27 s0:begin

28 if(x==1'b0) //0

29 begin

30 state<=s0;

31 z<=1'b0;

32 end

33 else //1

34 begin

35 state<=s1;

36 z<=1'b0;

37 end

38 end

39 s1:begin

40 if(x==1'b0) //10

41 begin

42 state<=s2;

43 z<=1'b0;

44 end

45 else //11

46 begin

47 state<=s1;

48 z<=1'b0;

49 end

50 end

51 s2:begin

52 if(x==1'b0) //100

53 begin

54 state<=s3;

55 z<=1'b0;

56 end

57 else //101

58 begin

59 state<=s1;

60 z<=1'b0;

61 end

62 end

63 s3:begin

64 if(x==1'b0) //1000

65 begin

66 state<=s0;

67 z<=1'b0;

68 end

69 else //1001

70 begin

71 state<=s4;

72 z<=1'b1;

73 end

74 end

75 s4:begin

76 if(x==1'b0) //10010

77 begin

78 state<=s2;

79 z<=1'b0;

80 end

81 else //10011

82 begin

83 state<=s1;

84 z<=1'b0;

85 end

86 end

87 default:begin

88 state<=s0;

89 z<=1'b0;

90 end

91 endcase

92 end

93

94 endmodule

(3) 1001序列检测电路测试代码:

1 //ex8_2 testbench

2 //2020-10-13

3 // by YongFengXie

4 `timescale 1ns/1ns

5 module ex8_2tb;

6 reg clk;

7 reg rst_n;

8 reg x;

9 wire z;

10

11 ex8_2 ut(clk,rst_n,x,z);

12

13 initial begin

14 clk=1'b0;

15 rst_n=1'b0;

16 x=1'b0;

17 #40 rst_n=1'b1;

18 #10 x=1'b0;

19 #10 x=1'b0; //000

20 #10 x=1'b1;

21 #10 x=1'b0;

22 #10 x=1'b1; //000

23 #10 x=1'b0;

24 #10 x=1'b1;

25 #10 x=1'b0; //010

26 #10 x=1'b0;

27 #10 x=1'b1;

28 #10 x=1'b0; //010

29 #10 x=1'b0;

30 #10 x=1'b1;

31 #10 x=1'b1; //011

32 #10 x=1'b1;

33 #10 x=1'b0;

34 #10 x=1'b1; //101

35 #10 x=1'b0;

36 #10 x=1'b0;

37 #10 x=1'b1; //001

38 #10 x=1'b1;

39 #10 x=1'b1;

40 #10 x=1'b0; //110

41 #10 x=1'b1;

42 #10 x=1'b0;

43 #10 x=1'b1; //101

44 #300 $stop;

45 end

46

47 always #5 clk=~clk;

48

49 endmodule

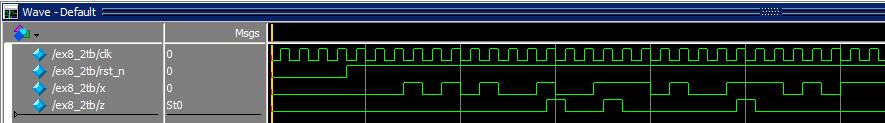

(4) 1001序列检测电路的仿真结果如图ex8_2_1所示:

图ex8_2_1 1001序列检测电路仿真结果

(5) 1001序列检测电路的状态转换如图ex8_2_2所示:

图ex8_2_2 1001序列检测电路状态转换图

(6)总结:跟习题8.1相比,无它,唯手熟尔。

习题8 #第8章 Verilog有限状态机设计-2 #Verilog #Quartus #modelsim的更多相关文章

- [Python学习笔记][第五章Python函数设计与使用]

2016/1/29学习内容 第四章 Python函数设计与使用 之前的几页忘记保存了 很伤心 变量作用域 -一个变量已在函数外定义,如果在函数内需要修改这个变量的值,并将这个赋值结果反映到函数之外,可 ...

- 《.NET 设计规范》第 5 章:成员设计

<.NET 设计规范>第 5 章:成员设计 5.1 成员设计的通用规范 要尽量用描述性的参数名来说明在较短的重载中使用的默认值. 避免在重载中随意地改变参数的名字.如果两个重载中的某个参数 ...

- MySQL性能调优与架构设计——第 18 章 高可用设计之 MySQL 监控

第 18 章 高可用设计之 MySQL 监控 前言: 一个经过高可用可扩展设计的 MySQL 数据库集群,如果没有一个足够精细足够强大的监控系统,同样可能会让之前在高可用设计方面所做的努力功亏一篑.一 ...

- MySQL性能调优与架构设计——第 17 章 高可用设计之思路及方案

第 17 章 高可用设计之思路及方案 前言: 数据库系统是一个应用系统的核心部分,要想系统整体可用性得到保证,数据库系统就不能出现任何问题.对于一个企业级的系统来说,数据库系统的可用性尤为重要.数据库 ...

- MySQL性能调优与架构设计——第12章 可扩展设计的基本原则

第12章 可扩展设计的基本原则 前言: 随着信息量的飞速增加,硬件设备的发展已经慢慢的无法跟上应用系统对处理能力的要求了.此时,我们如何来解决系统对性能的要求?只有一个办法,那就是通过改造系统的架构体 ...

- 《C++Primer》第五版习题答案--第三章【学习笔记】

[C++Primer]第五版[学习笔记]习题解答第三章 ps:答案是个人在学习过程中书写,可能存在错漏之处,仅作参考. 作者:cosefy Date: 2020/1/10 第三章:字符串,向量和数组 ...

- 《C++Primer》第五版习题解答--第四章【学习笔记】

[C++Primer]第五版习题解答--第四章[学习笔记] ps:答案是个人在学习过程中书写,可能存在错漏之处,仅作参考. 作者:cosefy Date: 2020/1/11 第四章:表达式 练习4. ...

- 《C++Primer》第五版习题答案--第五章【学习笔记】

<C++Primer>第五版习题答案--第五章[学习笔记] ps:答案是个人在学习过程中书写,可能存在错漏之处,仅作参考. 作者:cosefy Date: 2020/1/15 第五章:语句 ...

- 《C++Primer》第五版习题答案--第六章【学习笔记】

<C++Primer>第五版习题答案--第六章[学习笔记] ps:答案是个人在学习过程中书写,可能存在错漏之处,仅作参考. 作者:cosefy Date: 2020/1/16 第六章:函数 ...

- FPGA Prototyping By Verilog Examples第五章 状态机FSM设计

上升沿检测电路之Moore型FSM // Listing 5.3module edge_detect_moore ( input wire clk, reset, input wire level, ...

随机推荐

- layui select onchange事件处理

1.html代码如下,不要忘记 lay-filter属性 <div class="layui-input-block"> <select id=& ...

- KingbaseES 用户密码认证及加密算法

kingbaseES用户的口令被存储在sys_authid系统表中. 口令可以用SQL命令create user 和alter user 管理,例如 :create/alter user u1 wit ...

- 《MySQL技术内幕:InnoDB存储引擎》读书笔记

SQL语句优化策略 1.对查询进行优化,应尽量避免全表扫描,首先应考虑在 WHERE 及 ORDER BY 涉及的列上建立索引. 2.应尽量避免在 WHERE 子句中对字段进行 NULL 值判断,创建 ...

- 敏捷MVP面面观

在过去的十年中,软件开发经历了许多阶段.从使流程敏捷高效到使用DevOps简化IT服务,已经有了许多突破,MVP是对软件开发过程产生了根本性影响的进步之一.本文将深入探讨MVP在软件开发中怎样起作用. ...

- 【WCH以太网接口系列芯片】CH9121\20的使用和测试

本篇文章将介绍沁恒微电子的以太网转接芯片CH9121(CH9120和CH9121使用上没有区别,注意配置工具不一样,可以在沁恒微电子官网自行下载测试),该芯片支持网口和串口相互透传,可以通过串口AT指 ...

- #根号分治,动态规划#洛谷 5616 [MtOI2019]恶魔之树

题目传送门 分析 最小公倍数最终一定会被表示成若干个质数指数幂的情况(1的情况就直接乘上二的次幂) 然后每个数的加入相当于对每个质数的指数取最大值,但是如果将每个质数的次数都表示出来状态数很多, 考虑 ...

- #KMP,矩阵乘法#洛谷 3193 [HNOI2008]GT考试

题目 给定\(n,m,K\)和一个长度为\(m\)的数\(x\), 问有多少个\(n\)位数满足任意一段不与\(x\)完全相同,可含前导0 \(n\leq 10^9,m\leq 20\) 分析 设\( ...

- #计数,记忆化搜索#C 连边方案

分析 设\(dp[i][j][k][l]\)表示处理到\([i-l+1,i]\)的连边,二进制状态(奇点还是偶点)为\(k\)的方案数, 最后一维是为了避免算重,那么如果第\(i-l+1\)位是偶点可 ...

- C#只允许启动一个WinFrom进程

[STAThread] public static void Main() { bool ret; System.Threading.Mutex mutex = new System.Thread ...

- C语言 02 安装

C 语言的编译器有很多,其中最常用的是 GCC,这里以安装 GCC 为例. Windows 这里以 Windows 11 为例 官方下载地址:https://www.mingw-w64.org/ 选择 ...