verilog中always块延时总结

在上一篇博文中 verilog中连续性赋值中的延时中对assign的延时做了讨论,现在对always块中的延时做一个讨论。

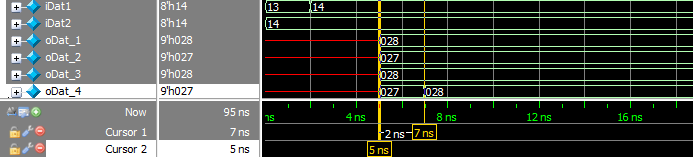

观测下面的程序,@0时刻,输入的数据分别是0x13,0x14 。

@2时刻,输入数据分别是0x14,,0x14 。

四个输出应该是什么样子呢?

- always @ (iDat1 or iDat2)

- # oDat_1 = iDat1 + iDat2;

- always @ (iDat1 or iDat2)

- oDat_2 = # iDat1 + iDat2;

- always @ (iDat1 or iDat2)

- # oDat_3 <= iDat1 + iDat2;

- always @(iDat1 or iDat2)

- oDat_4 <= # iDat1 + iDat2;

直接上图吧

作为阻塞性赋值语句,延时放在前面,就是先延时,再取值赋值。所以oData_1延时之后取了新值。

延时放在后面,就是先取值,再延时赋值。oData_2 是先取了旧值,再延时赋值,中间如果等号右边有变化,被阻塞了。所以oData_2是旧值 。

- always @ (iDat1 or iDat2)

- # oDat_1 = iDat1 + iDat2;

- always @ (iDat1 or iDat2)

- oDat_2 = # iDat1 + iDat2;

作为非阻塞性赋值语句,延时放在前面,就是先延时,再取值赋值。所以oData_3延时之后取了新值。

延时放在后面,就是先取值,再延时赋值。oData_4 是先取了旧值,再延时赋值,中间如果等号右边有变化,没有被阻塞,新建event,所以oData_2是旧值之后再更新为新值 。

- always @ (iDat1 or iDat2)

- # oDat_3 <= iDat1 + iDat2;

- always @(iDat1 or iDat2)

- oDat_4 <= # iDat1 + iDat2;

所以,这以后写TB的时候要慎重啊。

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884

verilog中always块延时总结的更多相关文章

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- 【转载】Verilog中的parameter

1. 概述 在Verilog中我们常常会遇到要将一个常量(算法中的某个参数)赋给很多个变量的情况,如: x = 10;y = 10;z = 10;如果此时10要改为9,就需要在代码中修改3个地方,非常 ...

- verilog中timescale

1. `timescale `timescale是Verilog中的预编译指令,指定位于它后边的module的时间单位和时间精度,直到遇到新的`timescale指令或者`resetall指令.它的语 ...

- Verilog中的$display和$write任务

$display(p1,p2, …,pn); $write(p1,p2, …,pn); 这两个函数和系统任务的作用都是用来输出信息,即将参数p2到pn按参数p1给定的格式输出.参数p1通常称为:“格式 ...

- Verilog中的阻塞与非阻塞

这篇文档值得阅读 按说阻塞与非阻塞是Verilog中最基本的东西,也是老生常谈.但是最近看到很多程序里用到阻塞语句竟然不是很明白,说到底是从来没有自己仔细分析过.当然一般情况程序中也是推荐用非阻塞的. ...

- 在verilog中调用VHDL模块

习惯了自己发现一些小问题,既然发现了,就记下来吧,不然又要忘了,这是多么悲痛的领悟. 今天在用vivado进行块设计时所生成的顶层模块居然是用VHDL语言描述的,这时郁闷了,表示只看过VHDL语法但没 ...

- 总结Verilog中always语句的使用

always语句包括的所有行为语句构成了一个always语句块.该always语句块从仿真0时刻开始执行其中的行为语句:最后一条执行完成后,再开始执行其中的第一条语句,如此往复循环,直到整个仿真结束. ...

- verilog中的timescale

`timescale是Verilog HDL 中的一种时间尺度预编译指令,它用来定义模块的仿真 时的时间单位和时间精度.格式如下: `timescale 仿真时间单位/时间精度 注意:,不能为其它的 ...

随机推荐

- IIS7.0/7.5 MVC3 实现伪静态

routes.MapRoute( "Default", "{controller}/{action}.html/{id}&qu ...

- 【原创】重绘winform的GroupBox

功能:重绘winform的GroupBox,以便调整边框颜色和边框宽度 using System; using System.Collections.Generic; using System.Com ...

- vs vsvim viemu vax 备忘

使用gt和gT往返标签 gd:到达光标所在处函数或者变量的定义处. *:读取光标处的字符串,并且移动光标到它再次出现的地方. #:和上面的类似,但是是往反方向寻找. /text:从当前光标处开始搜索字 ...

- C和C++运算符 (转)

这里是C和C++语言的运算符列表.所有列出的运算符皆含纳于C++:第三个栏目里的内容也使用C来描述.应当注意的是C不支持运算符重载. 下列运算符在两个语言中都是顺序点(运算符未重载时): && ...

- java 调用jdbc 实现excel和csv的导入和导出

jdbc 的连接 实体类 package com.gpdi.mdata.web.manage.database.data;public class DBQueryData {private Strin ...

- oracle中区分audit_file_dest, background_dump_dest, core_dump_dest, user_dump_dest

一般在$ORACLE_HOME\admin\{SID}目录下: audit_file_dest = /u01/app/oracle/admin/{SID}/adump ...

- Python中的isinstance函数

isinstance是Python中的一个内建函数 语法: isinstance(object, classinfo) 如果参数object是classinfo的实例,或者object是class ...

- [Java]利用栈判断括号是否完整配对

利用栈实现判断字符串中的括号是否都是配对的. 主要算法是依次读取字符串中的每一个字符,如果是左括号则将左括号压入栈中,如果是右括号则从栈中弹出最上面的字符,若两者不是同种括号或栈内已经没有字符就返回f ...

- oracle plsql 64位 32位连接未打开 无法解析各种错终极解决方案

首先取消登陆,进入pl/sql界面-工具-首选项 其次就需要你设置环境变量(加一个ORACLE_HOME和修改原先path里的路径这个不修改也行,主要是让大家知道为什么设置环境变量) 这些设置好,你在 ...

- delete了,析构函数却没有调用

析构函数在对象的生命结束时,会自动调用,大家所熟知的智能指针就是根据析构函数的这种特性而实现的,包括Qt的内存管理机制,也都是利用了析构函数的这一机制来实现的.c++创始人Bjarne Stroust ...