vivado 创建PL工程

参考来源

https://china.xilinx.com/video/hardware/i-and-o-planning-overview.html

前言

我Win10系统上的Xilinx Platform Studio打不开,无奈之下换用Vivado。这篇粗略地介绍Vivado创建FPGA工程的流程

使用Vivado

新建工程

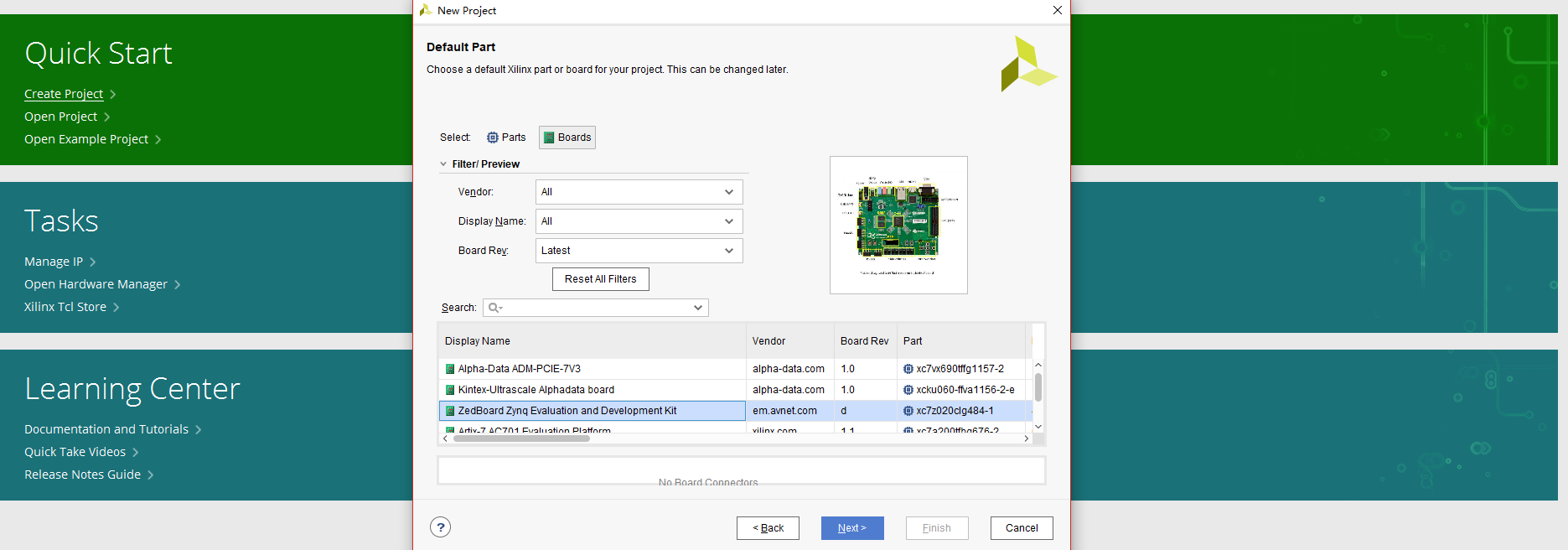

打开vivado,点New Project然后Create a New Vivado Project点next再填写工程名、工程路径点next

在Project Type选择 RTL 工程,单击 NEXT

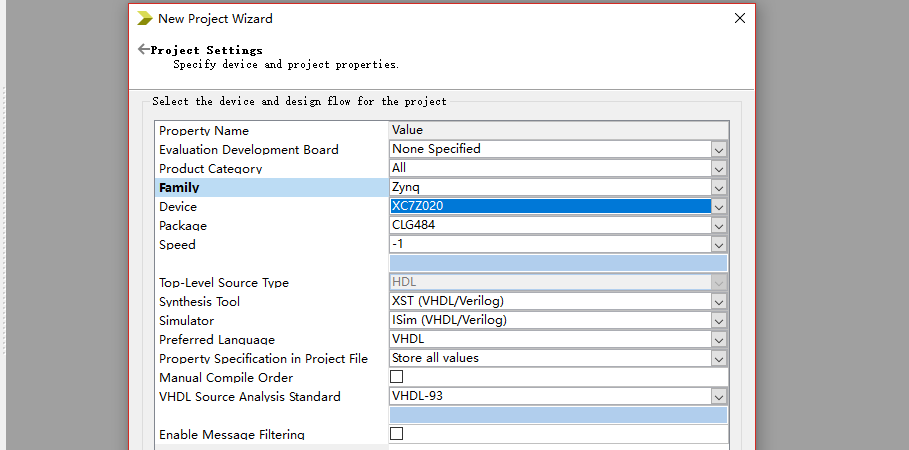

选择板子,我的是Zedboard,然后next-finish

设计输入

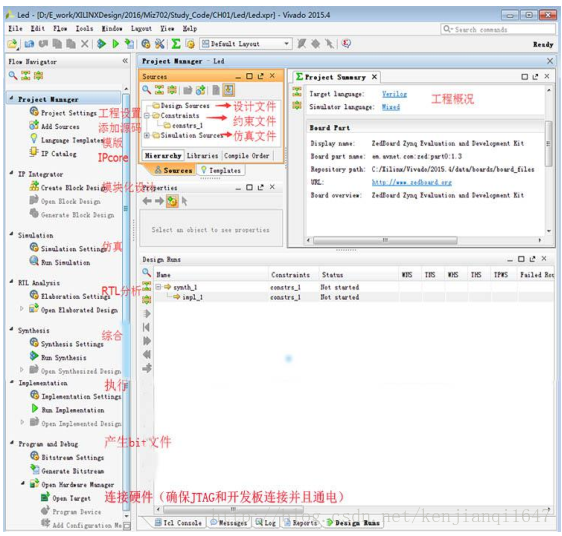

界面如下,图片来源https://blog.csdn.net/kenjianqi1647/article/details/79199657

代码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Flowing LED

-- 先分频再移位

entity LED is

port(

GCLK,BTNU:in std_logic;

LDS:out std_logic_vector(7 downto 0)

);

end LED;

architecture Behavioral of LED is

-- 计数

signal count:std_logic_vector(25 downto 0);

signal clk_temp:std_logic;

signal LDS_temp:std_logic_vector(7 downto 0):="00000001";

begin

process(GCLK,BTNU)

--分频系数

variable N :std_logic_vector(25 downto 0):="10111110101111000010000000";

begin

if BTNU='1' then

count<="00000000000000000000000001";

clk_temp<='1';

elsif (GCLK'EVENT and GCLK='1')then

if (count=N)then

count<="00000000000000000000000001";

clk_temp<='1';

else

count<=count+1;

clk_temp<='0';

end if;

end if;

end process;

--得到的clk_temp为2Hz,占空比1/50000000

process(clk_temp,BTNU)

begin

if BTNU='1' then

LDS_temp<="00000001";

elsif (clk_temp'EVENT and clk_temp='1')then

LDS_temp(0)<=LDS_temp(7);

LDS_temp(7 downto 1)<=LDS_temp(6 downto 0);

end if;

end process;

LDS<=LDS_temp;

end Behavioral;

引脚约束

NET "BTNU" IOSTANDARD = LVCMOS18;

NET "GCLK" IOSTANDARD = LVCMOS33;

NET "BTNU" LOC = T18;

NET "GCLK" LOC = Y9;

NET "LDS[7]" LOC = U14;

NET "LDS[6]" LOC = U19;

NET "LDS[5]" LOC = W22;

NET "LDS[4]" LOC = V22;

NET "LDS[3]" LOC = U21;

NET "LDS[2]" LOC = U22;

NET "LDS[0]" LOC = T22;

NET "LDS[1]" LOC = T21;

# PlanAhead Generated IO constraints

NET "LDS[7]" IOSTANDARD = LVCMOS33;

NET "LDS[6]" IOSTANDARD = LVCMOS33;

NET "LDS[5]" IOSTANDARD = LVCMOS33;

NET "LDS[4]" IOSTANDARD = LVCMOS33;

NET "LDS[3]" IOSTANDARD = LVCMOS33;

NET "LDS[2]" IOSTANDARD = LVCMOS33;

NET "LDS[1]" IOSTANDARD = LVCMOS33;

NET "LDS[0]" IOSTANDARD = LVCMOS33;

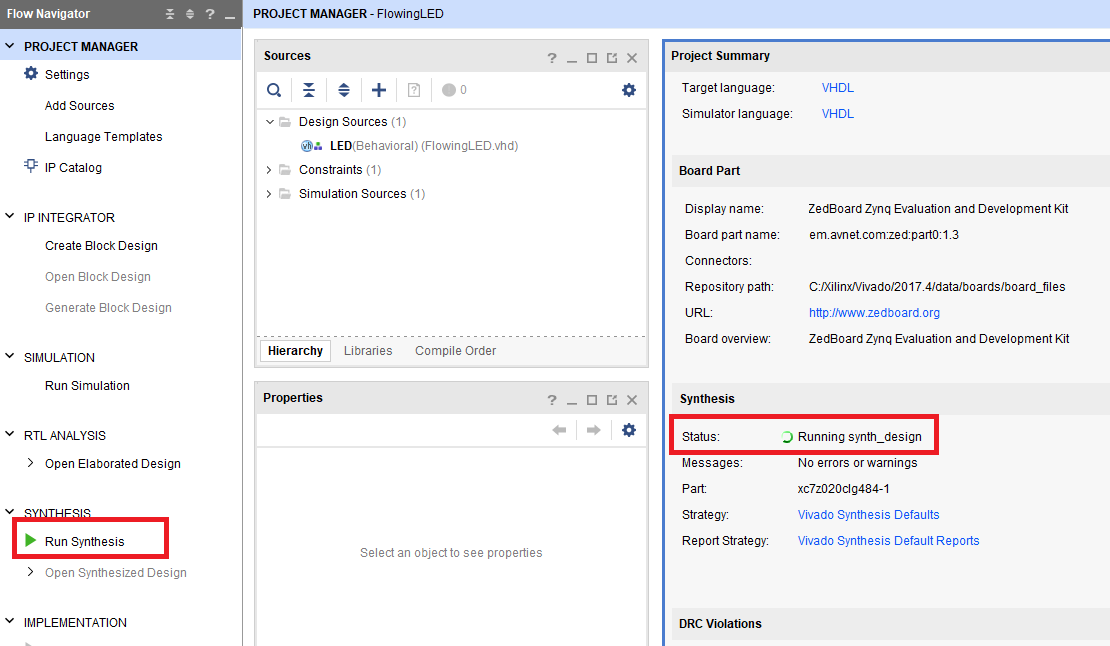

设计综合

设计综合过程会完成语法检查,编译,映射等步骤

点击Run Synthesis,可以在Project Summary 查看状态

综合完毕后

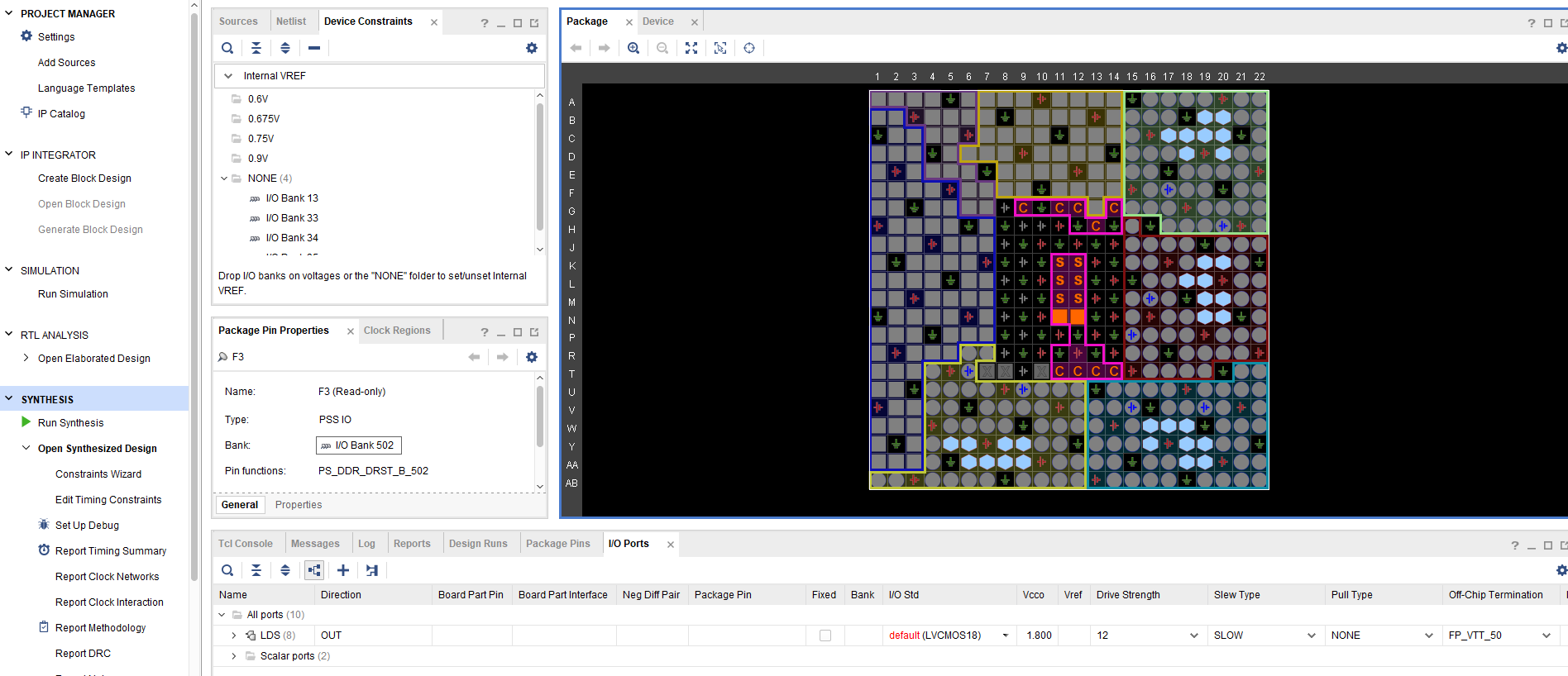

点击open synthesized design打开synthesized design,此时点击菜单栏的window-I/O ports 即可规划管脚。点击菜单栏Layout-I/O planning打开Package

设计实现

点击Run Implementation,完成后点击Generate Bitstream,生成比特文件

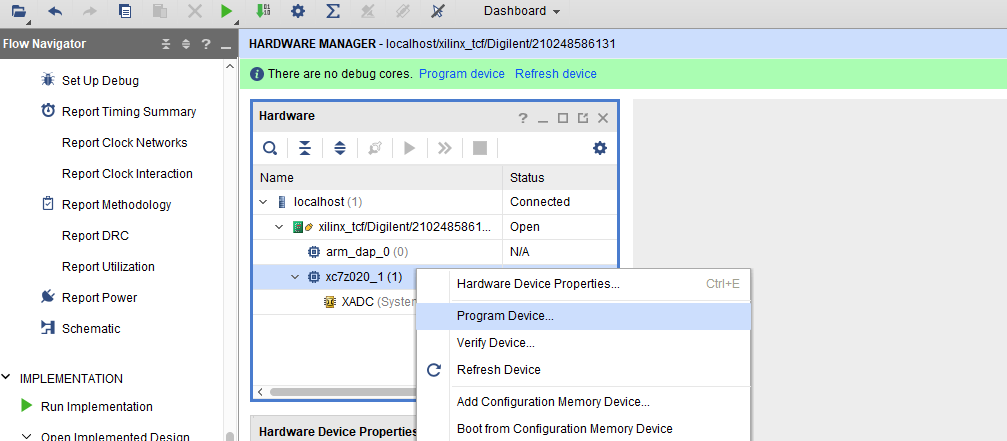

下载执行

将开发板通电并连接到电脑,点击Hardware Manager ,在fpga芯片上右键program,

现象

8个LED从右到左流水点亮,如果按BTNU从LED0开始重新流水点亮

使用ISE

流程:创建工程、设计输入、引脚约束、设计综合、设计实现、生成比特文件、下载执行

开发工具

ISE

硬件连接

Zedboard 的8个LED共阴极,置高电平点亮

100MHz时钟源接入GCLK引脚

BTNU按钮按下时是高电平,可用于高电平复位

器件属性配置

代码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Flowing LED

-- 先分频再移位

entity LED is

port(

GCLK,BTNU:in std_logic;

LDS:out std_logic_vector(7 downto 0)

);

end LED;

architecture Behavioral of LED is

-- 计数

signal count:std_logic_vector(25 downto 0);

signal clk_temp:std_logic;

signal LDS_temp:std_logic_vector(7 downto 0):="00000001";

begin

process(GCLK,BTNU)

--分频系数

variable N :std_logic_vector(25 downto 0):="10111110101111000010000000";

begin

if BTNU='1' then

count<="00000000000000000000000001";

clk_temp<='1';

elsif (GCLK'EVENT and GCLK='1')then

if (count=N)then

count<="00000000000000000000000001";

clk_temp<='1';

else

count<=count+1;

clk_temp<='0';

end if;

end if;

end process;

--得到的clk_temp为2Hz,占空比1/50000000

process(clk_temp,BTNU)

begin

if BTNU='1' then

LDS_temp<="00000001";

elsif (clk_temp'EVENT and clk_temp='1')then

LDS_temp(0)<=LDS_temp(7);

LDS_temp(7 downto 1)<=LDS_temp(6 downto 0);

end if;

end process;

LDS<=LDS_temp;

end Behavioral;

引脚约束

NET "BTNU" IOSTANDARD = LVCMOS18;

NET "GCLK" IOSTANDARD = LVCMOS33;

NET "BTNU" LOC = T18;

NET "GCLK" LOC = Y9;

NET "LDS[7]" LOC = U14;

NET "LDS[6]" LOC = U19;

NET "LDS[5]" LOC = W22;

NET "LDS[4]" LOC = V22;

NET "LDS[3]" LOC = U21;

NET "LDS[2]" LOC = U22;

NET "LDS[0]" LOC = T22;

NET "LDS[1]" LOC = T21;

# PlanAhead Generated IO constraints

NET "LDS[7]" IOSTANDARD = LVCMOS33;

NET "LDS[6]" IOSTANDARD = LVCMOS33;

NET "LDS[5]" IOSTANDARD = LVCMOS33;

NET "LDS[4]" IOSTANDARD = LVCMOS33;

NET "LDS[3]" IOSTANDARD = LVCMOS33;

NET "LDS[2]" IOSTANDARD = LVCMOS33;

NET "LDS[1]" IOSTANDARD = LVCMOS33;

NET "LDS[0]" IOSTANDARD = LVCMOS33;

现象

8个LED从右到左流水点亮,如果按BTNU从LED0开始重新流水点亮

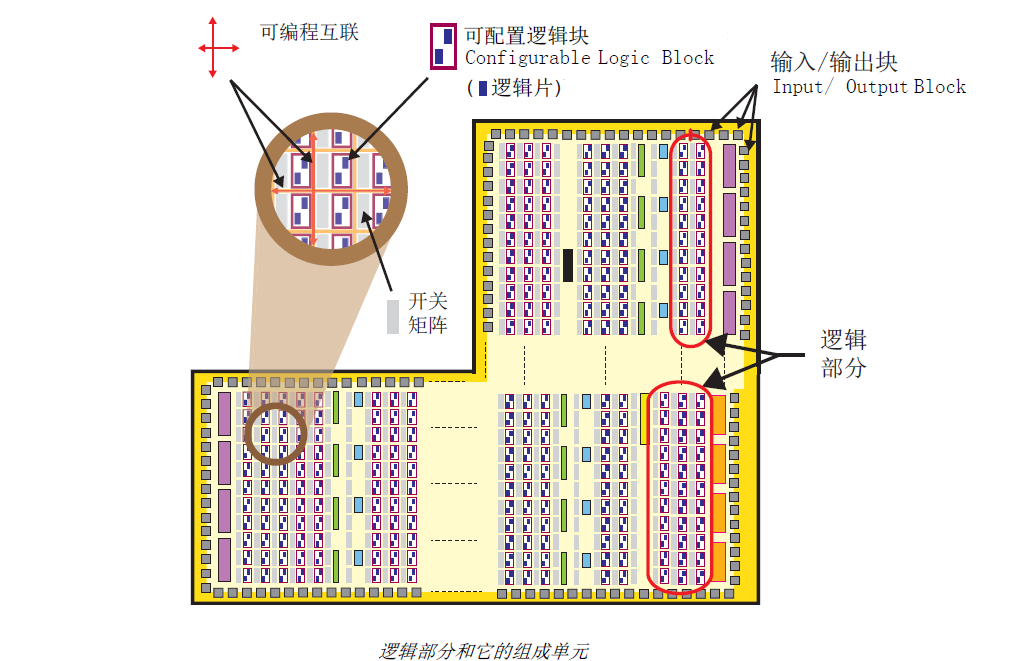

关于逻辑部分

通用FPGA逻辑部分如下所示

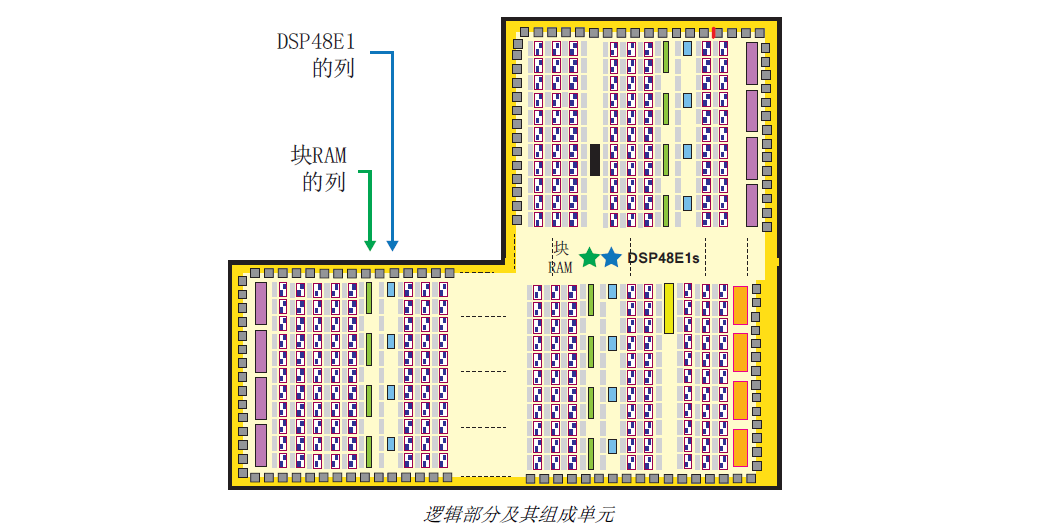

zynq的PL部分的特殊资源包括满足密集存储的块RAM和用于高速算术的DSP48E1。当然逻辑资源也可以用来搭建RAM,但是块RAM是经过优化的,使用很小的物理空间就可以存储大量数据;逻辑资源的查找表(LUT)也可以用来算术运算,但是会占用很多逻辑资源,DSP48E1是专用于长字长信号的高速算术运算的逻辑块。

其他硬IP部件

- GTX收发器实现与独立的外部芯片的连接,支持PCI Express和SATA等接口

- XDAC块,两个独立的12位ADC,采样速率达到1Msps,使用PS控制

- 独立的时钟

- JTAG实现配置和调试

vivado 创建PL工程的更多相关文章

- vivado 创建PS工程

前言 本文简要介绍在vivado中创建PS工程.单纯使用zynq芯片的PS部分就像使用普通ARM芯片一样,只是多了建立Zynq硬件系统这一个步骤.vivado创建PL工程参见此处 新建工程 与viva ...

- Vivado SDK 2014.2 创建新工程后,BSP版本不对的解决办法

问题描述如下: 1. 使用Vivado SDK 2014.2已经创建了工程,但是此时,hdf文件增加了外设,需要重新创建工程以更新SDK中的外设描述: 2. 使用新的hdf创建工程后,发现system ...

- Eclipse创建Maven工程报错

问题 用Eclipse创建maven工程的时候,总是会报错,例如提示: Unable to create project from archetype [org.apache.maven.archet ...

- MyEclipse创建Maven工程

先要在MyEclipse中对Maven进行设置:

- 关于Xcode6创建的工程在Xcode5打开

Xcode6创建的工程在Xcode5打开- 4.0只显示3.5大小的问题 只需要在工程里添加Default-568h@2x.png,即可以解决

- windows下无法创建django工程的问题

环境:python2.7 django1.7 安装好django后,将C:\Python27\Lib\site-packages\Django-1.7.7-py2.7.egg\django\bin; ...

- 在VS2015 RC打开CTP中创建的工程

VS2015终于出了RC了!小伙伴们快来安装试用吧,地址在这里,还有新的Windows 10开发工具哦,要不然是开发不了Universal Windows App的,安装前记得卸载CTP版本. 新的R ...

- iOS创建子工程

实际开发中,我们可能会同时开发好几个端,比如楼主目前开发的家教平台,需要老师端,家长端,助教端三个端.有很多工具方法,或者封装的自定义控件都是可以复用的.我们就可以把公用的代码抽取出去,新建一个工程, ...

- Myeclipse中创建Maven工程的时候没有 webapp-javaee6

1. http://mvnrepository.com/artifact/org.codehaus.mojo.archetypes/webapp-javaee6/1.5 中有描述

随机推荐

- phpmyadmin新姿势getshell

旁白:在一个有WAF.并且mysql中的Into outfile禁用的情况下,我该如何getshell? 作者:倾旋email:payloads@aliyun.com投稿联系:service@cora ...

- 25.redux回顾,redux中的action函数异步

回顾:Redux: 类似于 Vuex 概念:store/reducer/action action:动作 {type,.....} 一定要有type 其他属性不做限制 reducer:通过计算产生st ...

- 【C++ 继承与派生/知识梳理】

为什么引入继承派生 代码重用扩充 软件的复用 层次分类 派生类的语法定义 class 派生类名(1):继承方式(2) 基类名(3){ 派生成员声明:} *(1)一个派生类——>多个基类,多继 ...

- asp.net session锁导致ajax请求阻塞

问:为了可以顺序访问Session的状态值,Session是否提供了锁定机制?答:Session实现了Reader/Writer的锁机制:当页面对Session具有可写功能(即页面有<%@Pag ...

- 文件内容统计:对任意给定的.txt文件进行内容的字符数、行数、单词数进行统计

项目源码地址:https://gitee.com/xjtsh/projects 功能实现: wc.exe -c file.c //返回文件 file.c 的字符数 wc.exe -w file ...

- python--列表,元组,字符串互相转换

列表,元组和字符串python中有三个内建函数:,他们之间的互相转换使用三个函数,str(),tuple()和list(),具体示例如下所示 >>> s = "xxxxx& ...

- 图->最短路径->多源最短路径(弗洛伊德算法Floyd)

文字描述 求每一对顶点间的最短路径,可以每次以一个顶点为源点,重复执行迪杰斯特拉算法n次.这样,便可求得每一对顶点之间的最短路径.总的执行时间为n^3.但是还有另外一种求每一对顶点间最短路径的方法,就 ...

- ajax中的同步与异步修改数据的问题

这次项目中因为前端有事儿,项目紧急加个新需求,于是自己硬着头皮上去看了下前端的逻辑后便开始动手了,但是为了简单起见就直接自己写了个ajax调服务来获取数据,然后修改前端定义的全局数据 //ajax来请 ...

- FPGA总结——杂谈

数字设计 一.关于组合逻辑 竞争冒险:一个逻辑门的多个输入信号同时跳变(路径时延不同,使得状态改变的时刻有先有后).这种现象叫做竞争,引起的结果称为冒险. 消除毛刺(冒险):(1)增加冗余项:(2 ...

- 《linux就该这么学》第四节课笔记,三章和四章开始!

第三章 (根据课本和在线培训视频排版总结,借鉴请改动) 右键可打开终端练习 3.1:输入输出重定向 输入重定向:符号 "<" ,是一种 ...