《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新《FPGA全程进阶---实战演练》内容,此电子书是笔者三年所做过的一些项目总结,又有擅长记录的习惯,于是整理成博客。

过些天会更新的内容有C++学习初步,友晶科技 DE1-Soc板卡学习笔记,Altium Designer画板技巧,在去下一家之前尽量更新完毕。

今天讲一下Signal Tap II的使用。

1 基础知识讲解

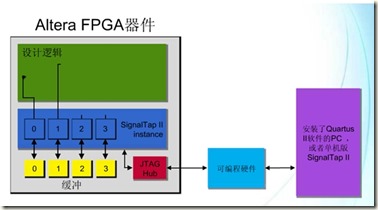

本章主要是讲解signal tap II的使用,signal tap II是quartus II 软件内部自带的一个逻辑分析仪,对于多通道数字信号的使用,一般都采用逻辑分析仪来操作。

Quartus II软件可以选择要捕获的信号,开始捕获的时间,以及要捕获多少的数据样本,还可以选择直接从器件的存储器块通过JTAG端口传送至STP II,并且有单次采样或者连续采样模式,捕获实时数据,方便工程的调试与开发。

对于signal tap II而言,是在工程中引入宏功能,以预先设定的时钟采样实时数据,并存储于FPGA中的RAM中,所以可见,使用STP II也要使用一定的代价,那就是占用FPGA内部资源,如果工程资源余量充足,况且可以使用,紧张的时候不建议采用STP II ,可以改用外部的逻辑分析仪操作。

还有一点注意的是,在全编译工程时,尽量不要把STP的文件也加载进来,因为STP本身占用一定的存储空间,这样会使编译速度减慢,而且还会消耗内部资源。

图32.1 signal tap II 采集原理

2 操作实例

在使用STP II之前,先把工程中的各引脚及其他设置设置好,然后全编译,编译完之后,再执行下述操作。

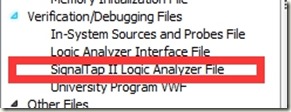

1. 新建stp文件。

2. 点击file---save as,然后输入你想设定的名字,然后点击yes。

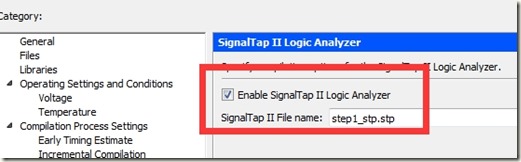

这里需要注意一下,就是如果你不想使用stp文件,或者使用其他的stp文件,可以在assignments---signaltap ii logic analyzer中设置。

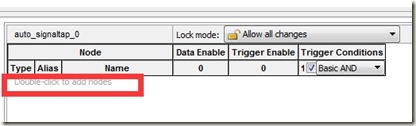

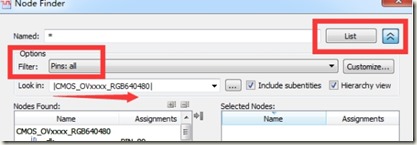

3. 接下来,我们要双击如下图所示的位置,调出节点发现器。

然后现在filter中选择pins:all,再点击list按钮,实现把所有的节点列出来。

对于上图中的filter选项中,当然还有其他的模式选择,比如前适配和后适配等,对于输入或输出信号,我们选择pins:all,这个选项,捕获模块接口(两个模块之间的沟通)信号则选择signal tap ii:pre-synthesis 选项,这是前适配,没有经过综合和适配的,其他模式一般不常用。

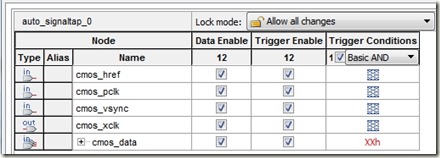

添加完之后的信号。

4. 设置采样时钟和采样深度

采样时钟决定了显示信号波形的分辨率,它的频率要大于被测信号的最高频率,否则无法正确反映被测信号波形的变化。采样时钟必须为采样信号的2倍及以上。SignalTap II在时钟的上升沿采样,可以使用设计系统中的任何信号作为采样时钟,根据Altera公司的建议最好使用同步系统全局时钟作为采样时钟。但是在实际应用中,多数使用独立的采样时钟,这样能采样到被测系统中的慢速信号,故需将系统时钟进行分频。

指定采样深度,在“Sample depth”处选择采样深度,即信号能看多长,它是根据设计中剩余的RAM块容量和待测信号的个数决定的。该值受FPGA芯片内置存储器大小的限制,设的过长,编译会通不过。

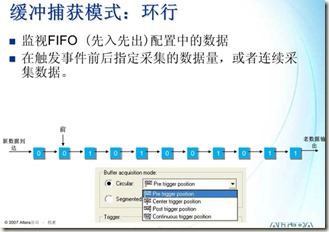

触发位置的设定,有前,后,中间,连续触发方式。

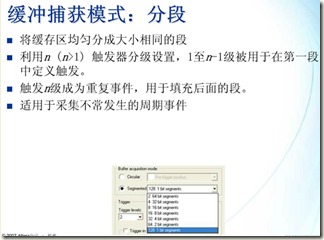

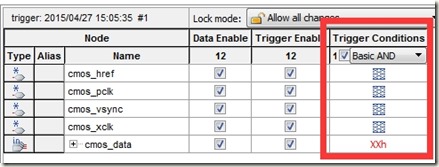

对于上图中的trigger conditions中可以设置多段式,如下图所示。

这种包括前触发方式(采样的数据12%为触发前,88%为触发后),中心触发方式(采样的数据50%为触发前,50%为触发后),后触发方式(采样的数据88%为触发前,12%为触发后),以及连续触发方式,前触发方式是来自于触发后的数据,中心触发来自于前触发和后触发,后触发来自于前触发的数据。连续触发方式将保存新数据,与触发器的位置无关,直到signal tap ii 停止工作。

上图中是设置触发的方式,有高电平,低电平,任意电平,不关心等等选项,可以根据所选用的信号进行设置触发方式。

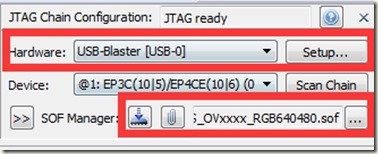

设置好上处的各个参数后,开始重新编译整个工程,然后将整个程序下载到FPGA开发板上面。当然也可以不用去下载到开发板上面,可以利用如下图的形式。

指定JTAG接口,然后将JTAG chain 加载进来,然后再把SOF文件也加载进来,再点击下载按钮。

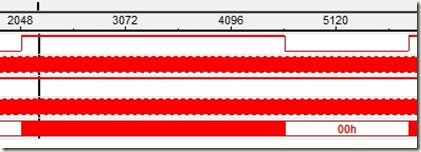

采集回来的数据如下图所示。

可以看出href的宽度为2560,但是由于我们的输入时钟为24MHz,采样时钟为48MHz,所以一个数据被采样了两次。那么每行输出的数据个数应该是2560/2 = 1280。由于输出的格式是RGB565格式,所以每个时钟输出两个数据,所以一行要输出640X2 = 1280个数据,可见和预期是一致的。

注意:xclk和pclk没有直接的关系,每次复位都会有不同的效果。

注意:对于帧频的输出,OV7725手册中规定是输出30Hz,可能有时候检测到25Hz,这个是因为若设置成50Hz的自动避免时,帧率只能输出到25Hz,但若设置成60Hz的自动避免时,帧率能输出到30Hz;

STP II 中的高级设置

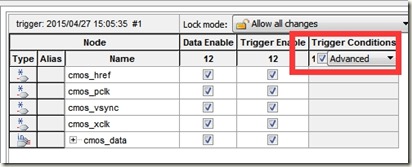

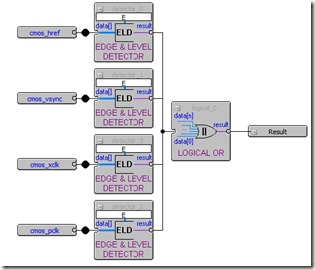

高级设置利用友好的GUI界面,可以方便地进行拖拽到指定的界面,然后设置相关的触发方式,如下图所示是一个简单的例子,还是针对上述的模块。

如上图所示,这个图形化的设置方式,是通过把触发方式设置成高级触发方式来设定的,其中E表示一旦有边沿变化,就会有高电平输出,然后经过组合逻辑或运算,输出结果。大家可自行尝试。

/****************************************************************

//===============================================================

上述内容如果有侵犯到您的权利,请及时与本作者联系,会在第一时间处理联系方式:

Email :tiegen123@126.com

QQ :770811496

QQ交流群:298095983(FPGA&硬件学习交流群)

个人博客:http://www.raymontec.com/

其他博客:http://www.cnblogs.com/raymon-tec由于作者水平有限,文中难免有疏漏或常识性错误,劳烦各位尽情指出。

欢迎大家一同讨论技术,交流设计过程中的经验,共同进步,共同学习。

//===============================================================

****************************************************************/

《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例的更多相关文章

- 《FPGA全程进阶---实战演练》第十二章 二进制码与格雷码PK

大家在写程序的时候,可能会听闻,什么独热码,什么格雷码,什么二进制码等等,本节意在解释这几种编码之间的区别和优势以及用verilog怎么去实现,下面先介绍这几种编码的区别. 1 基础理论部分 1.1 ...

- 《FPGA全程进阶---实战演练》第十四章 蜂鸣器操作

1 基础理论部分 本实验主要是实现蜂鸣器的操作,蜂鸣器的操作是非常简单的,只有把简单的事情做好,方可谈其他复杂的事.本实验部分会利用verilog一些宏定义语句,其实在VGA实验部分已经出现过,这里为 ...

- Gradle 1.12用户指南翻译——第三十二章. JDepend 插件

本文由CSDN博客万一博主翻译,其他章节的翻译请参见: http://blog.csdn.net/column/details/gradle-translation.html 翻译项目请关注Githu ...

- “全栈2019”Java多线程第三十二章:显式锁Lock等待唤醒机制详解

难度 初级 学习时间 10分钟 适合人群 零基础 开发语言 Java 开发环境 JDK v11 IntelliJ IDEA v2018.3 文章原文链接 "全栈2019"Java多 ...

- “全栈2019”Java第三十二章:增强for循环Foreach语法

难度 初级 学习时间 10分钟 适合人群 零基础 开发语言 Java 开发环境 JDK v11 IntelliJ IDEA v2018.3 文章原文链接 "全栈2019"Java第 ...

- 【小梅哥FPGA进阶教程】第十二章 数字密码锁设计

十二.数字密码锁设计 本文由山东大学研友袁卓贡献,特此感谢 实验目的 实现数字密码锁设计,要求矩阵按键输出且数码管显示输入密码,密码输入正确与否均会有相应标志信号产生. 实验平台 芯航线FPGA核心板 ...

- 《FPGA全程进阶---实战演练》第二章之焊接板子及调试注意事项

1.若是读者第一次做板子,强烈建议画完PCB板后将PCB图打印出来,然后对照你买的芯片将芯片放置对 应的位置,然后查看所有的封装格式适不适合,否则等你做出板子来后再试,为时晚矣.笔者虽然知道要这么 做 ...

- 《FPGA全程进阶---实战演练》第三章之接地设计

信号回路的电位基准点,(直流电源的负极或者零伏点)在单板上可以分为数字地和模拟地.理想的工作地是电路参考点的等电位平面,然而在实际中,工作地被认为信号电流的低阻抗回路和电源的供电回路,这样就会有三个方 ...

- 《FPGA全程进阶---实战演练》第三章之PCB叠层

1.双面板 在双层板设计layout时,最好不要不成梳状结构,因为这样构成的电路,回路面积较大,但是只要对较重要的信号加以地保护,布线完成之后将空的地方敷上地铜皮,并在多个过孔将两个地连接起来,可以弥 ...

随机推荐

- LeetCode之旅

14. 最长公共前缀 编写一个函数来查找字符串数组中的最长公共前缀. 如果不存在公共前缀,返回空字符串 "". 示例 1: 输入: ["flower",&quo ...

- php 将时间格式 转为时间戳

<?php $gte = "2018-08-08"; $year=((int)substr($gte,0,4));//取得年份: $month=((int)substr($g ...

- mysql case when then else end 的用法

case when then end 改语句的执行过程是:将case后面表达式的值与各when子句中的值进行比较,如果两者相等,则返回then后的表达式的值,然后跳出case语 句,否则返回else子 ...

- 超详细Gitlab Runner环境配置中文教程

配置GitlabRunner环境 GitLab Runner 是一个开源项目, 它用来运行你定制的任务(jobs)并把结果返回给 GitLab. GitLab Runner 配合GitLab CI(G ...

- [BZOJ3038]遥远的国度

Description: 给定一棵树,每次询问u节点在以v为根时的子树权值最大值 Hint: \(n \le 10^5\) Solution: 这个模型还是很重要的 考虑树剖 以1节点为根建树 当\( ...

- error :expected initializer before

很可能头文件或者前面的某个定义少了个:

- ES6 模板字面量

模板字面量 解决的问题 1.多行字符串 一个正式的多行字符串的概念 2.基本的字符串格式化 将变量的值嵌入字符串的能力 3.HTML转义 向HTML插入安全转换后的字符串的能力 (1)基础语法 相当于 ...

- sublime Text3 插件

sublime Text3 插件大全以及使用方法 参考网址: https://www.cnblogs.com/qqing/p/6872195.html

- keepalived+mysql backup服务器可ping通过vip但telnet vip+3306失败问题

环境: OS:CentOS 7_X64 数据库:mysql-5.7 MASTER:192.168.119.23 BACKUP:192.168.119.24 VIP:192.168.119.138 ke ...

- Java第一课

1.引入Java虚拟机原因?过程:源文件--编译器(使用javac命令)-----二进制的字节码文件(平台无关)--解释器(使用Java命令)-----可执行文件结论:Java中的跨平台是通过[JVM ...