【FPGA】Verilog实现交通信号灯

更新:

其余各部分代码已公布。

-------------------------------------------------------------------------------------------------------

大二数字电路的课程设计中,有一份日常作业使用Xilinx FPGA实现简易交通信号灯,但很可惜当时时间有限,没能最终完成。正好在这一学期选修SOPC设计课程,同样采用了Xilinx FPGA,故打算重新完成交通信号灯的相关内容。

本项目采用Digilent公司生产的BASYS3开发板,基于Xilinx FPGA,该板子目前可以在马云家买到,不过价格偏贵,在校学生可在digilent官网申请以更低价格买入。

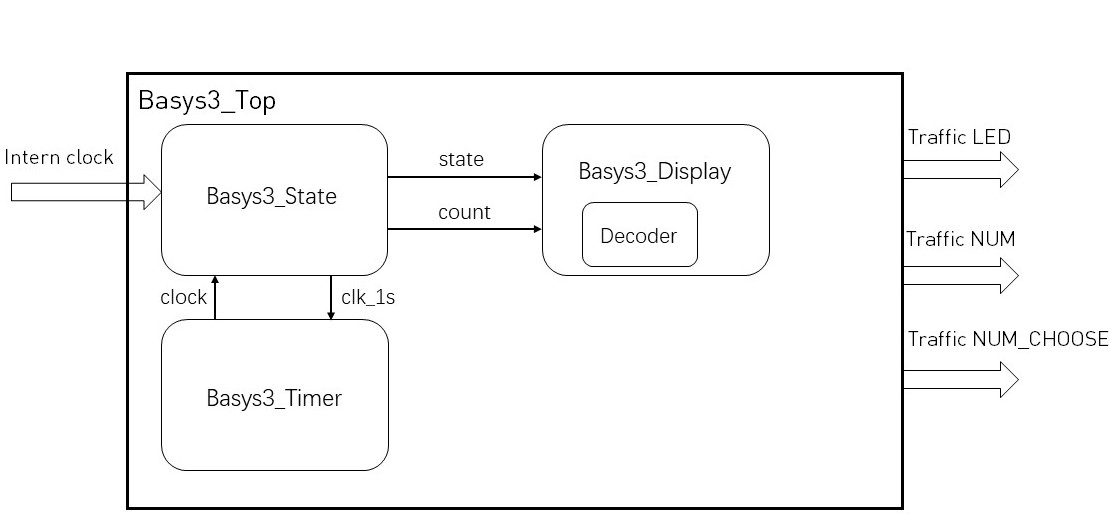

大致的框架如下,只是个构思,还很不完善,后续会进行修改。比如现在我目前并没有把计时功能完全从State模块中摘出来,只是用Timer实例化了一个1s计时器在里面,并且用count计数。

TOP代码

module BASYS_BIGPROJECT_Top

(

input clk,

output wire[:]Trans_light,

output wire[:]Num_choose,

output wire[:]Num_data

); wire [:]state_connect;

wire [:]count_connect;

//wire [6:0]Num_data_connect;

BASYS_BIGPROJECT_State state(

.clk(clk),

.state(state_connect),

.count(count_connect)

); BASYS_BIGPROJECT_Display display(

.clk(clk),

.count(count_connect),

.state(state_connect),

.Trans_light(Trans_light),

.Num_choose(Num_choose),

.Num_data(Num_data)

); endmodule

State代码

module BASYS_BIGPROJECT_State(

input clk,

output [:]state,

output [:]count

); reg [:]reg_state = ;

reg [:]reg_count = ;

wire cnt_connect; Freq_divider clk_1s(

.clk(clk),

.rst(),

.count(cnt_connect)

); //states for lights

parameter MR_BG = 'b00;

parameter MR_BY = 'b01;

parameter MG_BR = 'b11;

parameter MY_BR = 'b10; //green led for 4s, yellow led for 2s

always@(posedge cnt_connect)

begin

case(reg_state)

MR_BG:begin //main red, branch green

if(reg_count<) begin

reg_state <= MR_BG;

reg_count <= reg_count + ;

end

else begin

reg_state <= MR_BY;

reg_count <= 'b000;

end

end

MR_BY:begin //main red, branch yellow

if(reg_count<) begin

reg_state <= MR_BY;

reg_count <= reg_count + ;

end

else begin

reg_state <= MG_BR;

reg_count <= 'b000;

end

end

MG_BR:begin //main green, branch red

if(reg_count<) begin

reg_state <= MG_BR;

reg_count <= reg_count + ;

end

else begin

reg_state <= MY_BR;

reg_count <= 'b000;

end

end

MY_BR:begin //main yellow, branch red

if(reg_count<) begin

reg_state <= MY_BR;

reg_count <= reg_count + ;

end

else begin

reg_state <= MR_BG;

reg_count <= 'b000;

end

end

endcase

end

assign state = reg_state;

assign count = reg_count; endmodule

Display代码

module BASYS_BIGPROJECT_Display

(

input clk,

input [:]state,

input [:]count,

output [:]Trans_light,

output [:]Num_choose,

output [:]Num_data

); reg [:]reg_light = ;

reg [:]reg_Num_digit = ;

reg [:]reg_Num_choose = 'b1110;

wire [:]Num_data_connect;

wire refresh; reg [:]Data_Main = ;

reg [:]Data_Branch = ;

//divider for refresh

Freq_divider #()play(

.clk(clk),

.rst('b0),

.count(refresh)

);

//Decode the digit

Digital_decode decoder(

.clk(clk),

.data(reg_Num_digit),

.Trans_num(Num_data_connect)

); //switch the light

always @(posedge clk)

begin

case(state)

'b00:begin

reg_light <= 'b100001;

Data_Main <= - count;

Data_Branch <= - count;

end

'b01:begin

reg_light <= 'b100010;

Data_Main <= - count;

Data_Branch <= - count;

end

'b11:begin

reg_light <= 'b001100;

Data_Main <= - count;

Data_Branch <= - count;

end

'b10:begin

reg_light <= 'b010100;

Data_Main <= - count;

Data_Branch <= - count;

end

endcase

end //Scanned display for digit

always @(posedge refresh)

begin

if(reg_Num_choose == 'b1110)

begin

reg_Num_choose <= 'b1011;

reg_Num_digit <= Data_Main;

end

else

begin

reg_Num_choose <= 'b1110;

reg_Num_digit <= Data_Branch;

end

end assign Trans_light = reg_light;

assign Num_choose = reg_Num_choose;

assign Num_data = Num_data_connect;

endmodule

Tools代码

module Freq_divider

#(parameter N = )

(

input clk,

input rst,

output [N-:]freq_div,

output count

);

reg [N-:]regN = ;

always@(posedge clk)

begin

if(rst)

regN <= ;

else

regN <= regN+;

end

assign freq_div = regN;

assign count = (regN == **N-)?'b1:1'b0;

endmodule module Digital_decode

(

input clk,

input [:]data,

output [:]Trans_num

); reg [:]reg_Trans_num = ; always@(posedge clk)

begin

case(data)

'd0: reg_Trans_num <= 8'b0000_0011;

'd1: reg_Trans_num <= 8'b1001_1111;

'd2: reg_Trans_num <= 8'b0010_0101;

'd3: reg_Trans_num <= 8'b0000_1101;

'd4: reg_Trans_num <= 8'b1001_1001;

'd5: reg_Trans_num <= 8'b0100_1001;

'd6: reg_Trans_num <= 8'b0100_0001;

'd7: reg_Trans_num <= 8'b0001_1111;

'd8: reg_Trans_num <= 8'b0000_0001;

'd9: reg_Trans_num <= 8'b0000_1001;

default: reg_Trans_num <= 'b0001_0001;

endcase

end

assign Trans_num = reg_Trans_num;

endmodule

【FPGA】Verilog实现交通信号灯的更多相关文章

- FPGA Verilog HDL 系列实例--------步进电机驱动控制

[连载] FPGA Verilog HDL 系列实例 Verilog HDL 之 步进电机驱动控制 步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心.那么,下面我 ...

- 用Micro:bit做交通信号灯

交通信号灯项目在控制技术中,有点像"Hello world!" 是一个入门级的范例. 对于孩子来说,交通灯跟日常生活息息相关,他们都熟悉,充分知道需要做什么这是一个让孩子开始的好项 ...

- WPF用Blend写的交通信号灯

原文:WPF用Blend写的交通信号灯 版权声明:本文为博主原创文章,未经博主允许不得转载. https://blog.csdn.net/yangyisen0713/article/details/1 ...

- [FPGA]Verilog 60s秒表计时器(最大可计时间长达9min)

[FPGA]Verilog 60s秒表计时器 1.引述 这次的实验来自于本人本科课程数电结课时的自选题目.由于这次上传是后知后觉,学校已将小脚丫板子回收,所以在这篇文章中没法贴出代码结果的效果图了,但 ...

- [FPGA] Verilog 燃气灶控制器的设计与实现

燃气灶控制器的设计与实现 一.引述 本次实验所用可编程器件型号为MAXII EPM1270T144C5(其引脚表见本人另一博文:可编程实验板EPM1270T144C5使用说明),通过可编程实验板实现一 ...

- xilinx 赛灵思fpga verilog hdl 教程

http://www.eefocus.com/article/08-03/37231s.html http://wenku.baidu.com/link?url=5mdkMmm4BGGi7gRdgSk ...

- [FPGA]Verilog实现JK触发器组成的8421BCD码十进制计数器

目录 概述 电路分析 代码实现 参考文献 概述 本文以异步时序计数器为例,用Verilog实现以\(JK\)触发器组成的8421BCD码十进制异步计数器,并用ModelSim软件进行仿真验证. 电路分 ...

- [FPGA]Verilog实现可自定义的倒计时器(24秒为例)

目录 想说的话... 样例_边沿检测计数器 代码讲解 仿真演示 拓展_自定义倒计时数和倒计时间隔 代码讲解 仿真演示 总结 实例_24秒倒计时器 想说的话... 本次实现的是一个24秒倒计时器,功能顾 ...

- [FPGA]Verilog实现8位串并转换器HC595

目录 想说的话... 正文 IC介绍_HC595 电路连接图 功能表 逻辑图 代码实现 代码已经更新,新的代码按照电路编写,忠实于原电路的逻辑,已注于文末(11/16) 修复并行输出数据出错的bug, ...

随机推荐

- JavaScript Date 日期属性和方法

JavaScript 日期(Date) Date对象用于处理日期和时间.使用对象new Date()创建日期.实例化日期有四种方式: var d1 = new Date(); var d2 = new ...

- Java基础之 集合体系结构(Collection、List、ArrayList、LinkedList、Vector)

Java基础之 集合体系结构详细笔记(Collection.List.ArrayList.LinkedList.Vector) 集合是JavaSE的重要组成部分,其与数据结构的知识密切相联,集合体系就 ...

- install和cp

在Makefile里会用到install,其他地方会用cp命令 主要区别: 如果目标文件存在,cp会先清空文件后往里写入新文件,而install则会先删除掉原先的文件然后写入新文件.这是因为往正在 使 ...

- 转:Oracle的列转行函数:LISTAGG()

先看示例代码: with temp as( select 'China' nation ,'Guangzhou' city from dual union all select 'China' nat ...

- [TCP/IP] TCP报文长度是由什么确定的

MTU:最大传输单元,以太网的MTU为1500Bytes MSS:最大分解大小,为每次TCP数据包每次传输的最大数据的分段大小,由发送端通知接收端,发送大于MTU就会被分片 TCP最小数据长度为146 ...

- v8 编译 时长3小时

- 初识V4L2(三)-------分析vivi.c 虚拟视频驱动

1.分配video_device结构体 2.设置 3.注册 video_register_device 分析vivi.c: vivi_init( )//入口函数 vivi_create_instan ...

- 201871010111-刘佳华《面向对象程序设计(java)》第二周学习总结

201871010111-刘佳华<面向对象程序设计(java)>第二周学习总结 项目 内容 这个作业属于哪个课程 <https://www.cnblogs.com/nwnu-daiz ...

- 201871010112-梁丽珍《面向对象程序设计(java)》第二周学习总结

项目 内容 这个作业属于哪个课程 <任课教师博客主页链接>https://www.cnblogs.com/nwnu-daizh/ 这个作业的要求在哪里 <作业链接地址>http ...

- 循环控制语句if 、for、case、while

if 循环控制(单分支与多分支) (1)单个判断(单分支循环): if [ 条件判断 ]; then 执行动作 fi if [ 条件判断 ]; then 执行动作 else 执行动作 fi 写入tes ...