Test Design Techniques - STATE BASED TESTING

Test Design Techniques - STATE BASED TESTING

-Test note of “Essential Software Test Design”

2015-08-19

Content:

13.1 The Model

13.1.1 The ATM Machine

13.2 Creating Base Test Cases

13.2.1 Ways of Covering the Graph

13.2.2 Coverage According to Chow

13.2.3 Creating Test Cases

13.2.4 Transition Pairs

13.2.4.1 Expanding the Table by one Column

13.2.4.2 Creating a Dual Graph

13.2.5 Transition Triples and More

A STATE GRAPH, or state transition testing, is a model-based technique for compiling test cases. It works with event-driven systems, often in real time, and is common in areas like digital technology and electronics in hardware.

13.1 The Model

2 type:

- Mealy Graphs, where the state is represented by nodes and the links between the nodes represent transitions.

- Moore Graphs, where the events are represented by nodes.

Mealy Graphs are simpler to work with since they:

- More closely resemble what happens on their actual implementation

- Have fewer states, and since;

- The states are stable

- You can repeat events more easily without the graph becoming more complex

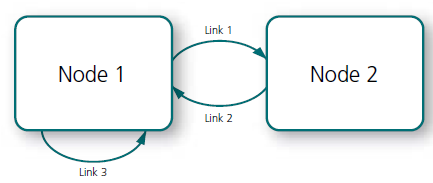

We call the states nodes, and call connections between the nodes links.

Figure 13.1: State Graphs consist of nodes and links. An arc is also called a transition. Links which start and end at the same node denote that an event does not lead to a transition, but it still undergoes some form of process.

Steps compile a graph:

- Compile the different states an object can find itself in

- Compile the transitions between the different states

- Identify the events which cause a transition to occur

- Define what happens during each transition

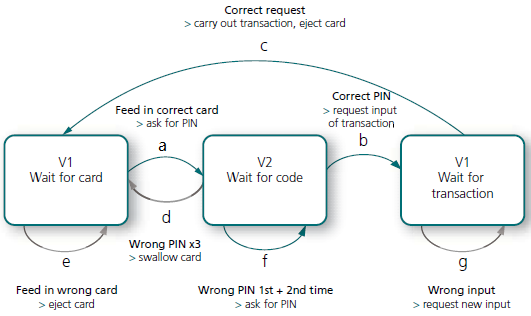

13.1.1 The ATM Machine

1. The different states are as follows:

a) Standby – nobody has inserted a card into the machine yet

b) Card inserted, request for PIN

c) PIN accepted – waiting for transaction

2. Draw arrows for the transitions according to the function descriptions

3. Events causing transition are:

a) Insert card

b) Enter correct PIN

c) Enter incorrect PIN

d) Enter correct transaction

e) Enter incorrect transaction

f) Choose to abort

4. What is carried out during transition is:

a) Request new PIN

b) Request new card

c) Request transaction

d) Eject money, card and receipt (execute transaction)

You have now created the picture below and the difficult work is complete.

Figure 13.2: Very simple state graph for an ATM. In reality, there are more states and events that are interesting to test and should be present in a complete graph.

13.2 Creating Base Test Cases

13.2.1 Ways of Covering the Graph

There are a number of variants of how to fill in the graph you have drawn up, besides the one described above. Some of them are:

- Typical routes. The most credible combinations

- The travelling salesman’s route. All different states in one test case.

- The Chinese Postman’s route. All transitions in the same test case, if there is that possibility.

- Risk-based. Routes where you think that a particular combination of transitions can cause problems.

- All routes a certain length. From shortest to longest until you have covered all combinations. This is suited to automation, since it repeats many combinations and takes a long time to carry out.

- All ways of leaving a state. For example, via a menu, function key, hot key, button and so on.

- All events which should not produce a transition. Verifies the system’s robustness.

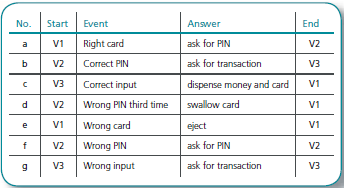

13.2.2 Coverage According to Chow

One method is to cover, firstly, all transitions, then all transitions pairs, triples etc. This was originally presented by Chow.

When you generate the test cases, there are different levels in the degree of coverage. Covering every individual transition is often called Chow’s 0-switch coverage. This can be visualized in a simple table.

Figure 13.3: Table of the different transitions in the state graph for the ATM. The simplest form of test coverage is to test all the rows in the table.

13.2.3 Creating Test Cases

The next step is to generate the test cases and, in parallel with this, mark off the transitions you are covering.

Test Case 1 (transitions a, f, b, g and c are covered)

- Insert right card (a)

- Enter wrong PIN (f)

- Enter correct PIN (b)

- Enter wrong input (g)

- Enter correct input (c)

- Take eject money, card and receipt

Test Case 2 (transition e is covered)

- Insert wrong card (e)

- Take ejected card

Test Case 3 (transition a, f, d is covered)

- Insert right card (a)

- Enter wrong code (f)

- Enter wrong code (f)

- Enter wrong code (d)

- Card is swallowed and you are back at the starting point

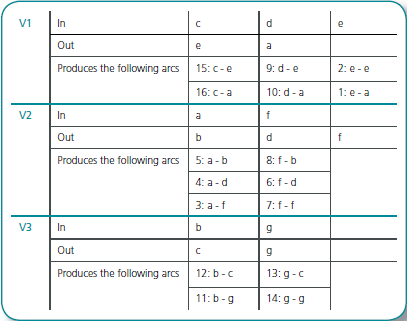

13.2.4 Transition Pairs

In order to achieve better coverage, you can use what we call transition pairs, involving two transitions in a row. The idea is that the result of an event in the system depends on what has happened in the preceding event. Sometimes, you will see the term 1-switch coverage.

13.2.4.1 Expanding the Table by one Column

There are two different ways of solving this, the first being to start with the first table and adding one additional column.

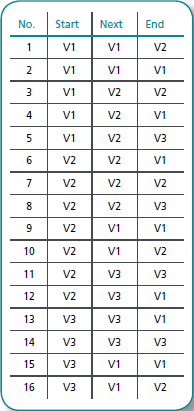

Analysis of our ATM produces the following 16 links:

Figure 13.5: Table showing development of transition pairs for the state graph ATM. We obtain all pairs by combining all routes into a node with all routes out of it. Even self-transactions, where we stay on the same node after transition, are counted.

The consolidated table is below, but columns showing event/answer have been taken out in order to simplify the table

Figure 13.6: Consolidated table of transition pairs for ATM state graph. A more accurate form of coverage is to test all combinations of two transitions. Obviously, this requires more test cases.

13.2.4.2 Creating a Dual Graph

You can also generate a dual graph, where the transitions represented earlier by links are substituted by nodes: in other words, a Moore graph. This way of testing all paired transitions is called the de Bruijn algorithm. To generate a dual graph, you do the following:

- Generate a graph where the links in the original have been changed to nodes.

- Everywhere in the original graph where arc 1 comes into a node, and arc 2 goes out of it, draw an arc between node 1 and node 2. Every arc will now represent a transition pair.

- Cover all links now with test cases.

Figure 13.7: Original and dual graph for the ATM. An alternative to developing the table of transition pairs is to create a Moore graph, where each transition represents a transition pair in the Mealy graph.

13.2.5 Transition Triples and More

You can proceed to more stringent requirements by setting up transition triples and quadruples, by adding another column in the table of transition pairs. The problem is that the number of test cases grows very quickly, so it is often difficult to test all of the pairs without automating the tests. It is common to use at least transition pairs and, if you find many defects, to press on, with more advanced tests in certain areas.

Test Design Techniques - STATE BASED TESTING的更多相关文章

- TEST DESIGN TECHNIQUES: AN OVERVIEW

TEST DESIGN TECHNIQUES: AN OVERVIEW -Test note of “Essential Software Test Design” 2015-11-16 目录: 7. ...

- Spock - Document -04- Interaction Based Testing

Interaction Based Testing Peter Niederwieser, The Spock Framework TeamVersion 1.1 Interaction-based ...

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 FSM Coding Goals

1.the fsm coding style should be easily modifiable to change state encoding and FSM styles. FSM 的的 状 ...

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之onehot coding styles(index-parameter style with registered outputs)

case语句中,对于state/next 矢量仅仅做了1-bit比较. parameter 值不是表示FSM的状态编码,而是表示state/next变量的索引.

- paper:synthesizable finite state machine design techniques using the new systemverilog 3.0 enhancements 之 standard verilog FSM conding styles(二段式)

1.Two always block style with combinational outputs(Good Style) 对应的代码如下: 2段式总结: (1)the combinational ...

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm summary

主要是1.不要用1段式写FSM 2.不要用状态编码写one-hot FSM ,要用索引编码写one-hot FSM.

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之全0/1/z/x的SV写法

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之enhanced coding styles

1.ANSI style 的代码比较紧凑. 下面规范推荐,比较好. 下面是带有parameter的module header的完整规范 一般1bit ,大家都是wire signal1 = gen_s ...

- paper:synthesizable finit state machine design techniques using the new systemverilog 3.0 enhancements之fsm1各种style的timing/area比较

整体说,一般还是用2段式,再加上output encodecd/default -X技巧.

随机推荐

- WinForm中DataGridView导出为Excel(快速版)

public static void ExportExcel(DataGridView myDGV, string fileName) { string saveFileName = fileName ...

- BZOJ.3620.似乎在梦中见过的样子(KMP)

题目链接 /* 896kb 6816ms A+B+A是KMP的形式,于是固定左端点,对于每个位置i,若fail[i]所能到的点k中(k=fail[fail[fail[...]]]),有满足len(l~ ...

- php创建udp Server

<?php//服务器信息$server = 'udp://127.0.0.1:7002';//----UDP Server$msgEof = "\n";$socket = s ...

- [HDU1392]Surround the Trees

思路: 凸包模板题. 注意n=1和n=2的情况. 当n=1时,不需要绳子. 当n=2时,绳子长度为两棵树之间距离. 当n≥e时,Graham求凸包即可.最后将凸包上的所有相邻点距离求和. #inclu ...

- JavaScript_几种继承方式(2017-07-04)

原型链继承 核心: 将父类的实例作为子类的原型 //父类 function SuperType() { this.property = true; } SuperType.prototype.ge ...

- 【洛谷】1600:天天爱跑步【LCA】【开桶】【容斥】【推式子】

P1600 天天爱跑步 题目描述 小c同学认为跑步非常有趣,于是决定制作一款叫做<天天爱跑步>的游戏.<天天爱跑步>是一个养成类游戏,需要玩家每天按时上线,完成打卡任务. 这个 ...

- Linux学习笔记13—Vi编辑器的学习

文本编辑工具vim.vi1. vim与vi的最大区别是vim编辑的时候是带颜色显示的.Vi不带颜色显示.2. yum install -y vim-enhanced 如果没有安装VIM 使用上面的命令 ...

- Windows平台交叉编译Arm Linux平台的QT5.7库

1.准备交叉编译环境 环境说明:Windows 7 64位 此过程需要: (1)Qt库开源代码,我使用的是5.7.0版本: (2)Perl语言环境5.12版本以上: (3)Python语言环境 2.7 ...

- 吴伯凡:VUCA时代的自我迭代

吴伯凡:VUCA时代的自我迭代 https://mp.weixin.qq.com/s?src=3×tamp=1506588223&ver=1&signature=nv ...

- android_双击退出

/** * 设置高速双击退出程序 */ @Override public boolean onKeyDown(int keyCode, KeyEvent event) { // TODO Auto-g ...