FPGA的时钟质量对设计的影响

小梅哥编写,未经许可严禁用于任何商业用途

近期,一直在调试使用Verilog编写的以太网发送摄像头数据到电脑的工程(以下简称以太网图传)。该工程基于今年设计的一款FPGA教学板AC620。AC620上有一个百兆以太网接口和一个通用CMOS摄像头接口,因此非常适合实现以太网图传功能。CMOS摄像头接口没有什么好说的,就是IO而已,这里先重点介绍下以太网接口。

以太网接口使用了一片10/100M自适应以太网收发器(PHY),型号为RTL8201。该芯片和FPGA采用标准的MII接口进行连接。什么是MII接口呢?这里暂不做任何介绍,因为今天要介绍的主角不是他。关于MII接口等以太网知识,可以关注小梅哥的FPGA以太网系列连载博客。简单点说,对于以太网发送数据来说,有一个发送时钟、一个发送使能信号和4位并行的数据发送信号,对于以太网接收数据,有一个接收时钟、一个接收数据有效信号和4位并行的数据接收信号。在发送时,发送使能信号有效,则每个字节的数据被拆分成2个4位的数据然后通过4位的数据信号,通过两个周期的时钟信号,依次传递到以太网PHY芯片,再由PHY进行并串转换,串行编码等工作后,将数据通过网络变压器加载到传输媒介(网线)上。在这里,以太网发送时钟是由以太网PHY芯片产生,然后送给FPGA使用的。该时钟信号一般叫做mii_tx_clk,当以太网速率为100Mbps时,该时钟信号为25MHz。而在FPGA侧,为了保证数据和控制信号的传输能够高度的同步于该以太网发送时钟信号,因此往往直接使用该以太网发送时钟信号作为相关时序逻辑的时钟信号。也因为这个要求,问题随之产生——该以太网时钟信号作为众多时序逻辑的时钟信号,其时钟质量和到达各个寄存器的时间最好也没有大的偏差,这样才能够保证时序收敛,从而使得设计的逻辑运行稳定。

在AC620 FPGA开发板上,该以太网发送时钟信号连接在了EP4CE10F17型FPGA的D11引脚上。而D11只是一个普通的FPGA输入输出管脚,非时钟输入管脚。因此从该引脚接入的信号如果不经过任何处理,将无法像专用时钟输入管脚上输入的信号一样被连接到全局时钟资源上。那么该时钟信号在FPGA片上进行走线时,只能使用片上的长线和短线布线资源,有时候甚至要通过LUT连接,才能到达各个寄存器。那么这里,问题就出现了,个人感觉的主要问题最起码有2点(不足的欢迎大家补充):

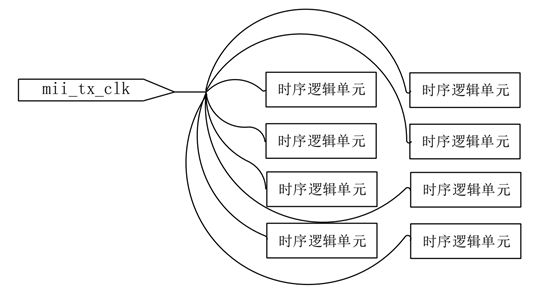

1、由于该时钟信号是通过各种长短布线资源,甚至经过LUT连接才能到达其驱动的各个寄存器,因此该时钟信号从进入FPGA管脚,到传递到各个寄存器的时钟输入端,其时间是很难保持相同的,距离的远近直接决定了该时钟信号的传输延迟。而这个传输延迟的差值,可能达到几纳秒甚至十几纳秒。这个差值,将直接影响数据的建立和保持时间,造成时序无法收敛,从而导致设计失败。我们可以通过下图更加直观的分析这个问题。

- CLK认为是时钟输入脚输入的时钟信号。REG1是数据源,REG2是数据接收寄存器。REG1的输出端Q经过一段组合逻辑后连接到REG2的输入端D上。

- REG1.CLK为CLK到达REG1的波形,相对于CLK,有一个延迟,设为Tclk1.

- REG1.Q为REG1的输出端数据值,其值开始稳定下来时,相对于REG1.CLK,有一个延迟,设为Tco。

- REG2.D为REG2的输入端D端口上的数据波形,该信号由REG1.Q经过组合逻辑传递后到达,因此REG1.Q到达REG2.D这个时间是数据传输时间,设为Tdata.

- RERG2.CLK(OK)是使用全局时钟资源时理想的波形,这种情况下,认为CLK到达REG1和REG2的时间差很小。

- RERG2.CLK(ERROR)是使用非全局时钟资源时的波形,这种情况下,认为CLK到达REG1和REG2的时间差可能较大,设这个差值为Tclk2。

由于REG2.D端口上的数据将在REG2.CLK的上升沿被采样,那么。当使用全局时钟资源时可以看到,在REG2.CLK的上升沿前后一段时间,数据是保持稳定的。而使用非全局时钟资源的时候,由于时钟走线的延迟,REG2.CLK到达REG2的时间将会有一个较大的差值,在这种情况下。在REG2.CLK的上升沿前后,REG2.D上的数据可能已经不稳定甚至变化了。因此导致数据接收失败。

2、使用非全局布线资源,时钟信号在布线的过程中更容易受到周围信号的干扰。导致时钟质量变差。什么意思呢?打个比方,一只小鸟和一只兔子共同穿越一个满是灰尘的工地。工地上到处都是灰尘。小鸟从空中飞过,不直接与灰尘接触,因此基本不会沾到灰尘,因为它有自己独立的路线和空间。而兔子因为不会飞,因此只能跑着从工地中穿过,那么,不可避免的,兔子的脚上会沾上灰尘。导致当兔子穿过这个工地的时候,早已由小白兔变成了小灰兔。时钟信号也是如此,全局时钟资源有专门的时钟路径,在自己的空间走线,不穿过或很少穿过各种高速翻转的逻辑区域,因此很少受到污染。而非全局时钟资源没有专门的时钟路径,只能使用通用布线资源,而这些布线不可避免的会穿过很多高速翻转的逻辑区域。从而受到这些逻辑的翻转噪声的污染。最终时钟信号变的很差。例如边沿上升和下降更慢,占空比发送变化,时钟抖动增大等。

好了,回到问题的开头,由于AC620开发板上以太网PHY芯片的mii_tx_clk是连接到了FPGA的普通IO口上,因此如果不经过处理,该时钟信号将不能走全局时钟资源,因此只能通过普通布线资源走线,从而导致到达各个寄存器的时间差别很大,而且受到各个高速翻转逻辑的噪声影响也很大,时钟抖动严重。所以,当该时钟信号驱动的逻辑过多时,势必导致整个设计时序无法收敛,然后就会出现各种各样的问题。

接下分析下我所编写的以太网发送逻辑。由于该逻辑主要为讲解以太网的各种协议而设计,而以太网协议最典型的特征就是数据是分层打包的。因此我在设计该逻辑的时候也严格按照以太网分层的方式进行。分别为MAC层、IP层、UDP层和用户数据层。在MAC层、IP层和UDP层,我都使用了PHY提供的这个时钟信号,所以导致该时钟信号的扇出非常的高。

从Quartus II软件的编译报告可以看出,该时钟信号的扇出为193个。是所有非全局信号中扇出最高的。这么高扇出的一个信号,还是时钟,可以想象该时钟到达这193个位置的路径有多少种可能,要经过多少布线链接。可想而知该时钟信号有多差。所以,我在调试时候出现的问题就是——不做任何修改,将该工程编译多次,有的时候编译得到的sof文件下载进芯片后能跑一整夜不宕机,而有的时候编译得到的sof文件下载进入芯片后几秒钟内就宕机了。

为了解决这个问题,需要将mii_tx_clk这个时钟信号分配到全局时钟资源上。这样该时钟信号就能走全局时钟资源,扇出再多,也能差不多同时到达各个寄存器。也有了自己的专线,不用从灰尘里滚爬,不怕小白兔变小灰兔。

首先看下全局资源的使用情况,如下图。

可以看到,PLL的4个输出,复位输入,以及晶振输入的50M时钟(clk)都被分配到了全局时钟资源上,尤其是clk信号,扇出高达1018个。

那么怎样才能让我们普通IO输入的时钟信号mii_tx_clk信号也能进入全局时钟资源呢?在Cyclone IV E器件中,有这样的专用缓冲器,该缓冲器可以将普通IO或者寄存器产生的时钟信号分配到全局时钟资源上。该缓冲器对用户以IP的形式提供,在IP列表的IO分组中,名称叫做ALTCLKCTRL,如下图所示。

设置也非常简单只需选择该时钟控制器的用途,我们这里设置为"For global clock"。另外在输入数量那里选择相应的值即可,我们这里只需将mii_tx_clk接入全局时钟资源,不需要做多时钟切换,因此数量选择1,设置完成后点击finish即可。

将该IP例化到我们的设计中,先定义一个mii_tx_clk_g,代表走全局时钟资源的mii_tx_clk信号。然后将输入的mii_tx_clk信号连接到这个缓冲器的输入,将缓冲器的输出连接到mii_tx_clk_g上即可,再由mii_tx_clk_g作为时钟信号驱动之前的所有时序逻辑。如下图所示。

|

wire mii_tx_clk_g; clk_ctrl clk_ctrl( .inclk(mii_tx_clk), .outclk(mii_tx_clk_g) ); |

通过该缓冲器,将mii_tx_clk信号连接到了全局时钟资源上,再通过全局时钟资源去连接到各个寄存器,则时钟延迟和时钟抖动都变的很小,使得时序易于收敛,设计出来的系统就更加稳定了。下图为通过该缓冲器将mii_tx_clk分配到全局时钟信号上后的全局资源使用图,可以看到,mii_tx_clk信号已经被分配到了全局时钟资源上。再由此方式编译得到的sof文件,烧写到AC620开发板中,能持续稳定运行。再次编译工程,再下载测试,都能稳定运行,问题得以解决。

下图为使用AC620开发板进行以太网图传的实际照片。

总之,还是那句话:学无止境,治学严谨,学以致用。我是小梅哥,欢迎大家关注我,一起学习FPGA技术。

小梅哥

2017年7月8日星期六

武汉.光谷

FPGA的时钟质量对设计的影响的更多相关文章

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

- FPGA跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- 基于FPGA的XPT2046触摸控制器设计

基于FPGA的XPT2046触摸控制器设计 小梅哥编写,未经许可,文章内容和所涉及代码不得用于其他商业销售的板卡 本实例所涉及代码均可通过向 xiaomeige_fpga@foxmail.com 发 ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

- 基于FPGA的SPI FLASH控制器设计

1.SPI FLASH的基本特征 本文实现用FPGA来设计SPI FLASH,FLASH型号为W25Q128BV.支持3种通信方式,SPI.Dual SPI和Quad SPI.FLASH的存储单元无法 ...

- FPGA跨时钟域握手信号的结构

FPGA跨时钟数据传输,是我们经常遇到的问题的,下面给出一种跨时钟握手操作的电路结构.先上图 先对与其他人的结构,这个结构最大的特点是使用 req 从低到高或者高到低的变化 来表示DIN数据有效并开始 ...

- Xilinx FPGA控制器的Everspin STT-DDR4设计指南

自旋转移扭矩磁阻随机存取存储器(STT-MRAM)是一种持久性存储技术,可利用各种工业标准接口提供性能,持久性和耐用性. Everspin推出了STT-MRAM产品,该产品利用称为JE-DDR4的JE ...

随机推荐

- Django 模型层(2)

多表操作: 创建模型: 作者模型:把作者的详情放到详情表,包含生日,手机号,家庭住址等信息.作者详情模型和作者模型之间是一对一的关系(one-to-one) 出版商模型:出版商有名称,所在城市以及em ...

- REST理解

内容摘自:<Spring REST> REST是什么:REST是一种软件架构风格,它由建立规模可扩展的web服务的最佳实践和指南构成. 资源: 一切可被访问和操作的东西.资源标识:URI( ...

- python写个Hack Scan

前言: 之前逛SAFEING极客社区的时候 发现一款黑市卖2000多的软件,后面下载了 打不开.发现config文件里面有些不错的东西.总结了一下 有了以下的脚本. 脚本用处: [1]探测CMS(不敢 ...

- SVN版本控制系统最佳实践

第1章SVN介绍及应用场景 1.1什么是SVN(Subversion) Svn(subversion)是近年来崛起非常优秀的版本管理工具,与CVS管理工具一样,SVN是一个跨平台的开源的版本控制系统. ...

- git之生成SSH key

git之生成SSH key SSH 为 Secure Shell 的缩写,由 IETF 的网络小组(Network Working Group)所制定.利用 SSH 协议可以有效防止远程管理过程中的信 ...

- vue组件之echarts报表

vue组件之echarts报表 将echarts报表封装成组件,动态传入数据,显示图表. 1.饼状图 父组件: <MPie :datas="piedata"></ ...

- TextBox 设置数据源的自动补全输入字符串功能

这个东西首先说明是不是自己原创,但是比较简单.所以讲起分享如下.主要是用到TextBox的自动补全属性,这个东西虽然自己以前经常用TextBox,但是补全从没接触过. 关键代码是在窗体载入时加载如下代 ...

- notepad++正则表达式删除所有行某字符开始之前或者之后所有字符

删除S 之后的所有字符用:s.*$ 删除S 之前的所有字符用:^.*s

- jxl导出excel的问题

jxl导出excel,通常浏览器会提示excel导出完成情况及默认保存路径,或让用户自定义选择保存路径,要达到这种效果,有些要做下修改,如:response是jsp的内置对象,在jsp中使用时不用声明 ...

- 前端开发之CSS入门篇

一.CSS介绍和语法 二.CSS引入方式 三.基本选择器 四.高级选择器 五.伪类选择器 六.伪元素选择器 1️⃣ CSS介绍和语法 1. CSS的介绍 (1)为什么需要CSS? 使用css的目的就 ...