Bringing up the Avnet MicroZed with Vivado

Bringing up the Avnet MicroZed with Vivado

I recently received the Adam Taylor Edition of Avnet's Zynq-based MicroZed board, which was sent by the very kind people at Xilinx. I have been writing about the ZedBoard for a while now over on All Programmable Planet. For the original ZedBoard, I used the more traditional PlanAhead, Xilinx Platform Studio, and Software Design Kit (SDK) flow. With that in mind, I decided that for the MicroZed I would implement the system using the Xilinx Vivado Design Suite, which turned out to be surprisingly easy. My aim is to progress with the MicroZed in a similar manner to the ZedBoard: looking at creating the system, using the on-chip XADC, boot-loading the MicroZed, adding my own peripheral, and finally adding an operating system. I expect this will progress rapidly expect due to my familiarity with the ZedBoard.

The first step is to download the MicroZed board definition and configuration, which are available at http://www.zedboard.org/documentation/1519. The first file to download is the MicroZed board definition file, which should be extracted to your Xilinx implementation directory. In my case, the directory is loacated at C:\Xilinx\Vivado\2013.2\data\boards\zynq. This file provides the Vivado Design Suite with MicroZed configuration information. The second file you'll need is a TCL file containing the necessary preset information for the MicroZed. We'll run this TCL file once we have created a project.

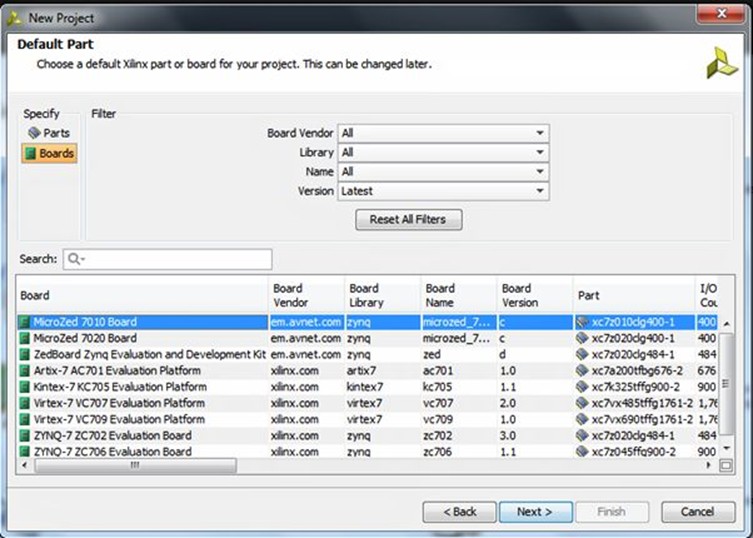

After starting Vivado, the first step is to create a new project. My first MicroZed project will be an RTL project and will not contain any initial source code. The next step is to select the MicroZed 7010 board as a default target using the definition file just downloaded.

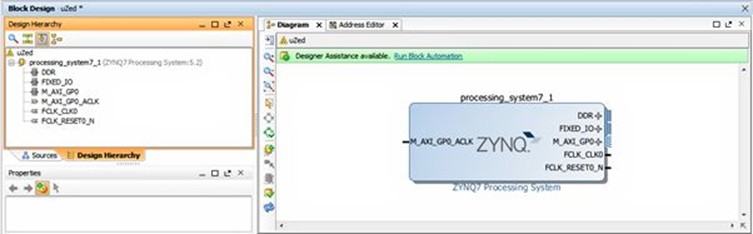

Now that the project is created, we need to add the Zynq SoC's processing system (PS). The best way to do this is to create a new block diagram and add in the Zynq PS from the IP library in Vivado. We can then create a block diagram by selecting the option under the flow-control window on the left-hand side of the Vivado screen.

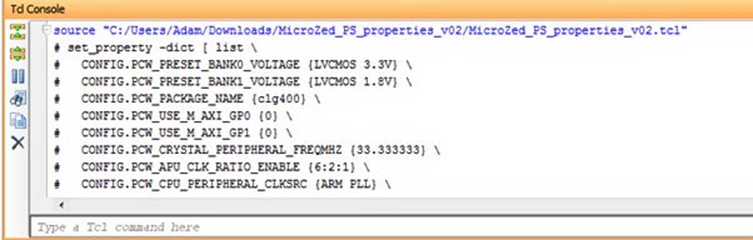

With the PS now added to the block diagram, we need to define the system. We could do this by hand (as would be the case for a custom board). Rather helpfully, the MicroZed people have created a TCL file that defines the MicroZed system. It's the preset file we downloaded at the start. This TCL file defines the PS bank voltages, buses, clocks, fabric clocks, DDR3 settings, external peripherals, and the MIO configuration.

Note: Remember to use linux style forward separators:

"C:/Users/Adam/Downloads/MicroZed_PS_properties_v02/MicroZed_PS_properties_v02.tcl"

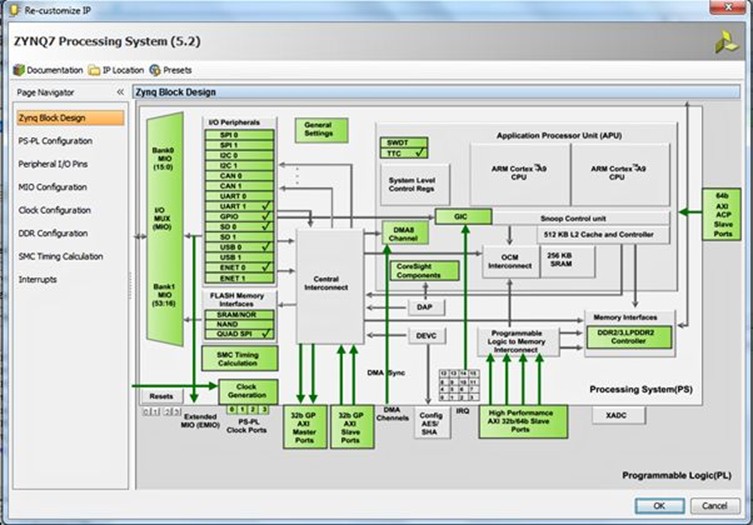

Having applied this file, we then double click on the system and we see the Zynq PS design. Notice that this definition ties up with the capabilities of the MicroZed board's Ethernet, USB, DDR3 etc.

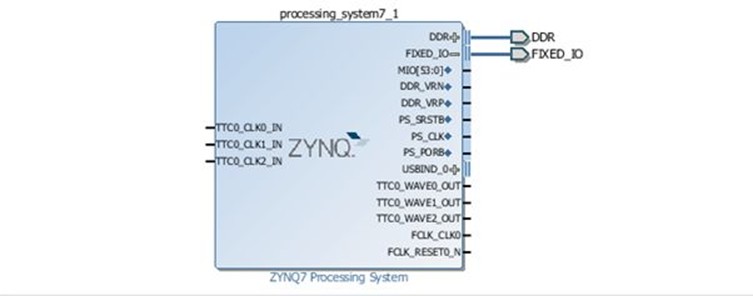

Once we're happy with the PS configuration, we need to declare the system's external I/O. In this case, we want to declare the DDR and the fixed I/O. Within the Zynq PS, the fixed I/O includes the MIO, clocks, and resets along with the DDR3 reference voltages. As these are fixed, no UCF file is required because we are not working with the programmable logic (PL) side of the Zynq. We will need to create UCFs later when we use the Zynq's PL side.

To add these external I/O declarations, you click on the "run design automation" option that appears at the top of the diagram. This will generate a warning. Clicking on "OK" allows you to proceed and you will then see outputs added to the fixed IO and the DDR within the block diagram.

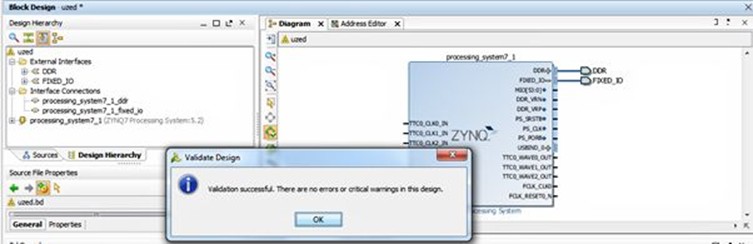

Now we're nearly ready to proceed to build the system. However, we must first validate the design to ensure that it is valid and contains no errors by selecting the "validate design" button on the left side of the Vivado screen.

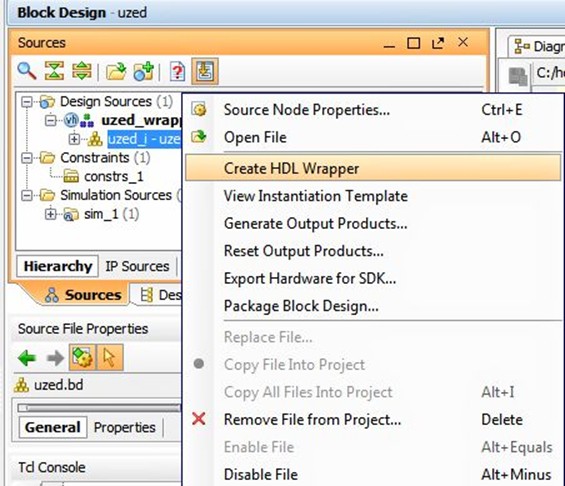

Having created a valid block diagram we will want to save this before we proceed. Once you have saved the design, the next step is to generate the files needed to implement the system, starting with the creation of the HDL wrapper. But first, we need to determine which language we're going to work in (VHDL or Verilog). We select the HDL via the Tools->Project Settings Menu.

Once we've selected our preferred language, we right click on the uzed.bd file under "sources" and select "Create HDL Wrapper" to generate the wrapper.

We can also create the necessary synthesis and place-and-route files by selecting the "Generate Output Products…" option from the same menu that we used to generate the HDL wrapper.

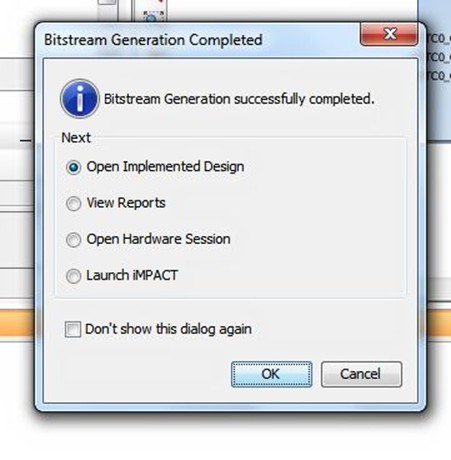

Once these files have been created, it's time to generate the bitstream by selecting the "Generate Bitstream" option in the flow navigator on the left of the Vivado screen. When the bitstream generation completes, you will see:

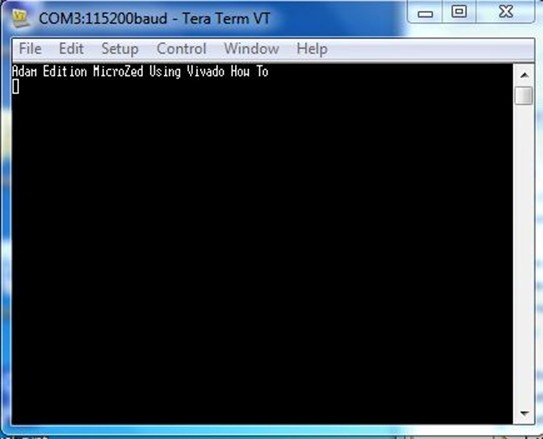

With the bitstream created, we then export the data into SDK. Then we're ready to write the software to run on the MicroZed's Zynq SoC. I'll discuss this process in my next blog, but a sneak peak of where we are headed appears below.

I spent an afternoon bringing up the MicroZed and really enjoyed the experience. My next blog post will wrap up SDK project creation and boot loading with the MicroZed.

Note: Please do not be concerned if you see an error in Vivado version 2013.2 which reports "Failed to get a license:Internal Bit stream." This is a bug in the current version. You can check in the implementation log to make sure that the license was in fact obtained.

Bringing up the Avnet MicroZed with Vivado的更多相关文章

- MiZ702学习笔记9——XADC采集片上数据PS版

这次借助zynq的内嵌的XADC来采集zynq内部的一些参数: •VCCINT:内部PL核心电压 •VCCAUX:辅助PL电压 •VREFP:XADC正参考电压 •VREFN:XADC负参考电压 •V ...

- 第九章 ZYNQ-MIZ701 片上ADC的使用

9.0难度系数★☆☆☆☆☆☆ 9.1实验概述 这次借助zynq的内嵌的XADC来采集zynq内部的一些参数: •VCCINT:内部PL核心电压 •VCCAUX:辅助PL电压 •VREFP:XADC ...

- 第九章 MIZ702 ZYNQ片上ADC的使用

9.0难度系数★☆☆☆☆☆☆ 9.1实验概述 这次借助zynq的内嵌的XADC来采集zynq内部的一些参数: •VCCINT:内部PL核心电压 •VCCAUX:辅助PL电压 •VREFP:XADC ...

- XADC

XADC实验 1.XADC概述 Xilinx7系列内部自带一个双通道12位分辨率的高速(1MSPS 1M sample per second)采样速率的模拟混合信号处理模块,双通道的ADC支持单极和差 ...

- 71.Adam Taylor玩转MicroZed系列第82部分:简单通信接口第2部分

By Adam Taylor 从上周的博客开始,我们已经进入到Zedboard(而不是MicroZed)板上的OLED显示模块的编程了.然而在正式进入具体的OLED编程之前,我认为有必要验证我们是否已 ...

- Vivado SDK 2014.2 创建新工程后,BSP版本不对的解决办法

问题描述如下: 1. 使用Vivado SDK 2014.2已经创建了工程,但是此时,hdf文件增加了外设,需要重新创建工程以更新SDK中的外设描述: 2. 使用新的hdf创建工程后,发现system ...

- notepad++与vivado关联

notepad++与vivado关联 打开vivado软件,选择菜单栏“Tools——>Options…”,在弹出的对话框中,选择General选项卡,如图1所示. 图1 选择General选 ...

- [转载]Vivado轻松实现IP封装

Vivado轻松实现IP封装 1.新建一个测试工程 工程化的设计方法是离不开工程的,第一步往往都是新建工程,后面我会学习去工程化的开发方法,可能会更加高效. 2.利用向导完成IP封装 2.1.启动IP ...

- 在vivado中使用attribute

之前最常用的一个attribute就是mark_debug了,语法如下:(*mark_debug="ture"*). 今天又学到几个新的,原文在这里:http://china.xi ...

随机推荐

- 13.QT多窗口切换list

Dialog::Dialog(QWidget *parent) : QDialog(parent), ui(new Ui::Dialog) { ui->setupUi(this); list = ...

- easyui 之表单验证

/** * 扩展easyui的validator插件rules,支持更多类型验证 */ $.extend($.fn.validatebox.defaults.rules, { minLength : ...

- Flask_URL和视图

1.Flask_URL和视图 1.1.第一个flask程序 from flask import Flask #创建一个Flask对象,传递__name__参数进去 app = Flask(__na ...

- Redis学习笔记(九) 命令进阶:Pub/Sub(发布/订阅)操作

原文链接:http://doc.redisfans.com/pub_sub/index.html Redis的Pub/Sub模型可以应对工作中的一些简单应用,涉及到复杂应用还是推荐使用诸如Rabbit ...

- 将百度百科的机器学习词条中的一段关于机器学习的demo改用Java写了一遍

这是引用的百度百科中关于机器学习的一段示例,讲述了通过环境影响来进行学习的例子. 下面是代码: import java.io.BufferedReader; import java.io.IOExce ...

- Python 之 入门须知

1.Python2.0不支持中文,3.0支持 2.版本问题

- RabbitMQ学习笔记(1)----RabbitMQ简介与安装

·1. 什么是RabbitMQ? RabbitMQ是流行的开源消息队列系统,用erlang语言开发.RabbitMQ是AMQP(高级消息队列协议)的标准实现. 而AMQP协议则是指:即Advanced ...

- 如何在使用layer.prompt在输入值为空的情况下点击确定继续执行逻辑?

突然发现在使用LayUI时,用到弹出层layer.prompt时,如果文本框输入值是空的话点击确定没有反应,不能向下执行. 但是我又需要在这种情况下去继续执行判断或逻辑时该怎么做?? 示例:原代码如下 ...

- zabbix-server端监控MySQL服务

Zabbix 监控MySQL数据库 为server.zabbix,com 添加服务模块 创建MySQL服务图形 Server.zabbix.com 服务器操作 [root@server ~]# cd ...

- Codeforces 679A Bear and Prime 100

链接:传送门 题意:给你一个隐藏数,这个隐藏数在[2,100]之间,现在最多可以询问20次,每次询问的是这个数是不是隐藏数的底数,是为yes,不是为no,每次询问后都需要flush一下输出缓冲区,最后 ...