Intel 8086 CPU

一、8086概述

Intel8086拥有四个16位的通用寄存器,也能够当作八个8位寄存器来存取,以及四个16位索引寄存器(包含了堆栈指标)。资料寄存器通常由指令隐含地使用,针对暂存值需要复杂的寄存器配置。它提供64K8位元的输出输入(或32K16位元),以及固定的向量中断。大部分的指令只能够存取一个内存位址,所以其中一个操作数必须是一个寄存器。运算结果会储存在操作数中的一个寄存器。

Intel8086有四个内存区段(segment)寄存器,可以从索引寄存器来设定。区段寄存器可以让CPU利用特殊的方式存取1MB内存。8086把段地址左移4位然后把它加上偏移地址。大部分的人都认为这是一个很不好的设计,因为这样的结果是会让各分段有重叠。尽管这样对组合语言而言大部分被接受(也甚至有用),可以完全地控制分段,使在编程中使用指针(如C编程语言)变得困难。它导致指针的高效率表示变得困难,且有可能产生两个指向同一个地方的指针拥有不同的地址。更坏的是,这种方式产生要让内存扩充到大于1MB的困难。而8086的寻址方式改变让内存扩充较有效率。

8086处理器的时钟频率介于4.77MHz(在原先的IBMPC频率)和10MHz之间。8086没有包含浮点指令部分(FPU),但是可以通过外接数学辅助处理器来增强浮点计算能力。Intel8087是标准版本。

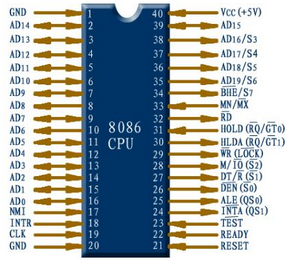

二、8086引脚图及功能

⑴AD15~AD0(addressdatabus):地址/数据总线,双向,三态。

这是一组采用分时的方法传送地址或数据的复用引脚。根据不同时钟周期的要求,决定当前是传送要访问的存储单元或I/O端口的低16位地址,还是传送16位数据,或是处于高阻状态。

⑵A19/S6~A16/S3(address/status):地址/状态信号,输出,三态。

这是采用分时的方法传送地址或状态的复用引脚。其中A19~A16为20位地址总线的高4位地址,S6~S3是状态信号。S6表示CPU与总线连接的情况,S5指示当前中断允许标志IF的状态。S4,S3的代码组合用来指明当前正在使用的段寄存器。S4,S3的代码组合及对应段寄存器的情况。

⑶BHE(低)/S7(bushighenable/status):允许总线高8位数据传送/状态信号,输出,三态。

为总线高8位数据允许信号,当低电平有效时,表明在高8位数据总线D15~D8上传送1个字节的数据。S7为设备的状态信号。

⑷RD/(read):读信号,输出,三态,低电平有效。

信号低电平有效时,表示CPU正在进行读存储器或读I/O端口的操作。

⑸READY(ready):准备就绪信号,输入,高电平有效。

READY信号用来实现CPU与存储器或I/O端口之间的时序匹配。当READY信号高电平有效时,表示CPU要访问的存储器或I/O端口已经作好了输入/输出数据的准备工作,CPU可以进行读/写操作。当READY信号为低电平时,则表示存储器或I/O端口还未准备就绪,CPU需要插入若干个“TW状态”进行等待。

⑹INTR(interruptrequest):可屏蔽中断请求信号,输入,高电平有效。

8086CPU在每条指令执行到最后一个时钟周期时,都要检测INTR引脚信号。INTR为高电平时,表明有I/O设备向CPU申请中断,若IF=1,CPU则会响应中断,停止当前的操作,为申请中断的I/O设备服务。

⑺TEST/(test):等待测试控制信号,输入,低电平有效。

信号用来支持构成多处理器系统,实现8086CPU与协处理器之间同步协调的功能,只有当CPU执行WAIT指令时才使用。

⑻NMI(non-maskableinterrupt):非屏蔽中断请求信号,输入,高电平有效。

当NMI引脚上有一个上升沿有效的触发信号时,表明CPU内部或I/O设备提出了非屏蔽的中断请求,CPU会在结束当前所执行的指令后,立即响应中断请求。

⑼RESET(reset):复位信号,输入,高电平有效。

RESET信号有效时,CPU立即结束现行操作,处于复位状态,初始化所有的内部寄存器。复位后各内部寄存器的状态,当RESET信号由高电平变为低电平时,CPU从FFFF0H地址开始重新启动执行程序。

⑽CLK(clock):时钟信号,输入。

CLK为CPU提供基本的定时脉冲信号。8086CPU一般使用时钟发生器8284A来产生时钟信号,时钟频率为5MHz~8MHz,占空比为1:3。

⑾VCC电源输入引脚。

8086CPU采用单一+5V电源供电。

⑿GND:接地引脚。

⒀MN/MX/(minimum/maximum):最小/最大模式输入控制信号。

引脚用来设置8086CPU的工作模式。当为高电平(接+5V)时,CPU工作在最小模式;当为低电平(接地)时,CPU工作在最大模式。

三、8086工作模式

1、最小模式

用于由8086单一微处理器构成的小系统。在这种方式下,由8086CPU直接产生小系统所需要的全部控制信号。器系统特点是:总线控制逻辑直接由8086CPU产生和控制。若有CPU以外的其他模块想占用总线,则可以向CPU提出请求,在CPU允许并响应的情况下,该模块才可以获得总线控制权,使用完后,又将总线控制权还给CPU。

当引脚接高电平时,CPU工作于最小模式。此时,引脚信号24~31的含义及其功能如下。

⑴M/IO/(memoryI/Oselect):存储器、I/O端口选择控制信号。

信号指明当前CPU是选择访问存储器还是访问I/O端口。为高电平时,访问存储器,表示当前要进行CPU与存储器之间的数据传送。为低电平时,访问I/O端口,表示当前要进行CPU与I/O端口之间的数据传送。

⑵WR/(write):写信号,输出,低电平有效。

信号有效时,表明CPU正在执行写总线周期,同时由信号决定是对存储器还是对I/O端口执行写操作。

⑶INTA/(interruptacknowledge):可屏蔽中断响应信号,输出,低电平有效。

CPU通过信号对外设提出的可屏蔽中断请求做出响应。为低电平时,表示CPU已经响应外设的中断请求,即将执行中断服务程序。

⑷ALE(addresslockenable):地址锁存允许信号,输出,高电平有效。

CPU利用ALE信号可以把AD15~AD0地址/数据、A19/S6~A16/S3地址/状态线上的地址信息锁存在地址锁存器中。

⑸DT/(datatransmitorreceive):数据发送/接收信号,输出,三态。

DT/信号用来控制数据传送的方向。DT/为高电平时,CPU发送数据到存储器或I/O端口;DT/为低电平时,CPU接收来自存储器或I/O端口的数据。

⑹DEN/(dataenable):数据允许控制信号,输出,三态,低电平有效。

信号用作总线收发器的选通控制信号。当为低电平时,表明CPU进行数据的读/写操作。

⑺HOLD(busholdrequest):总线保持请求信号,输入,高电平有效。

在DMA数据传送方式中,由总线控制器8237A发出一个高电平有效的总线请求信号,通过HOLD引脚输入到CPU,请求CPU让出总线控制权。

⑻HLDA(holdacknowledge):总线保持响应信号,输出,高电平有效。

HLDA是与HOLD配合使用的联络信号。在HLDA有效期间,HLDA引脚输出一个高电平有效的响应信号,同时总线将处于浮空状态,CPU让出对总线的控制权,将其交付给申请使用总线的8237A控制器使用,总线使用完后,会使HOLD信号变为低电平,CPU又重新获得对总线的控制权。

2、最大模式

用于实现多处理机系统,其中,8086CPU被称为主处理器,其他处理器被称为协处理器。在这种方式下,8086CPU不直接提供用于存储器或I/O读写的读写命令等控制信号,而是将当前要执行的传送操作类型编码为3个状态位输出,由总线控制器8288对状态信号进行译码产生相应控制信号。最大模式系统的特点是:总线控制逻辑由总线控制器8288产生和控制,即8288将主处理器的状态和信号转换成系统总线命令和控制信号。协处理器只是协助主处理器完成某些辅助工作,即被动的接受并执行来自主处理器的命令。和8086配套使用的协处理器有两个:一个是专用于数值计算的协处理器8087,另一个是专用于输入输出操作的协处理器8089。8087通过硬件实现高精度整数浮点数运算。8089有其自身的一套专门用于输入输出操作的命令系统,还可带局部存储器,可以直接为输入输出设备服务。增加协处理器,使得浮点运算和输入输出操作不再占用8086时间,从而大大提高了系统的运行效率。

当引脚接低电平时,CPU工作于最大模式。此时,引脚信号24~31的含义及其功能如下。

⑴S2,S1,S0(statussignals):总线周期状态信号,输出,低电平有效。

⑵RQ/,GT/(request/grant):总线请求允许信号输入/总线请求允许输出信号,双向,低电平有效。

该信号用以取代最小模式时的HOLD/HLDA两个信号的功能,是特意为多处理器系统而设计的。当系统中某一部件要求获得总线控制权时,就通过此信号线向8086CPU发出总线请求信号,若CPU响应总线请求,就通过同一引脚发回响应信号,允许总线请求,表明8086CPU已放弃对总线的控制权,将总线控制权交给提出总线请求的部件使用。RQ/GT0优先级高于RQ/GT1。

⑶LOCK/(lock)总线封锁信号,输出,低电平有效。

信号有效时,表示此时8086CPU不允许其他总线部件占用总线。

⑷QS1,QS0(queuestatus):指令队列状态信号,输出。

QS1和QS0信号的组合可以指示总线接口部件BIU中指令队列的状态,以便其他处理器监视、跟踪指令队列的状态。

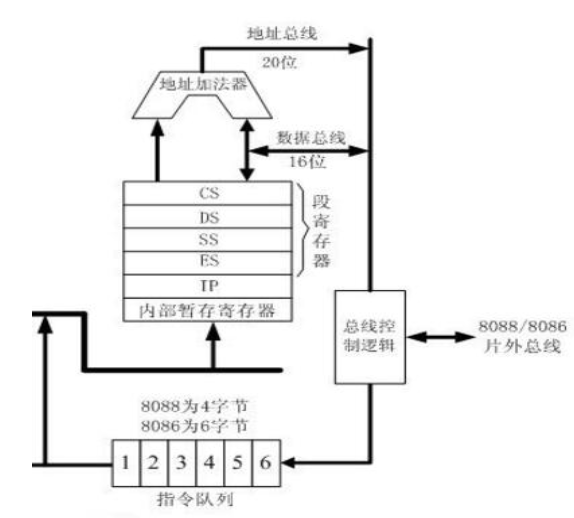

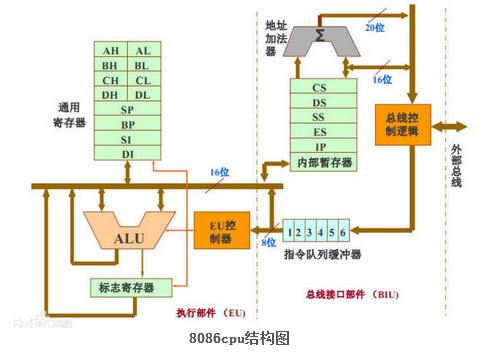

四、8086结构

总线接口单元(BIUbusinterfaceunit)

总线接口部件由下列各部分组成

⑴4个段地址寄存器:

CS(codesegment)——16位的代码段寄存器;

DS(datasegment)——16位的数据段寄存器;

ES(extrasegment)——16位的扩展段寄存器;

SS(stacksegment)——16位的堆栈段寄存器;

⑵16位的指令指针寄存器IP;

⑶20位的地址加法器;

⑷6字节的指令队列缓冲器。

执行单元

执行部件由下列几个部分组成:

⑴8个通用寄存器:即AX、BX、CX、DX,BP,SP,SI,DI;

其中,4个数据寄存器:AX、BX、CX、DX;

2个地址指针寄存器:BP(basepointer),SP(stackpointer);

2个变址寄存器:SI(sourceindex),DI(destinationindex)[2];

⑵标志寄存器FR(flagsregister);

⑶算术逻辑单元ALU(arithmeticlogicunit)。

EU负责全部指令的执行,同时向BIU输出数据(操作结果),并对寄存器和标志寄存器进行管理。在ALU中进行16位运算,数据传送和处理均在EU控制下执行。

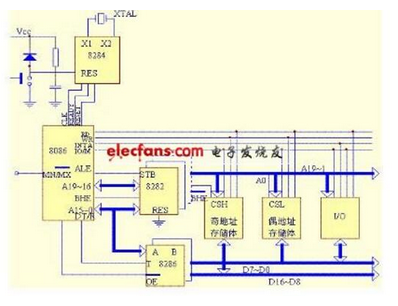

五、8086系统组成

8086是一种微处理器,再加上必须的支持芯片,如时钟发生器,地址锁存器,总线驱动器,存储器和I/O接口等,才能构成一台完整的微型计算机。根据外部设备的数量和系统复杂程度,8086可以选用两种系统构成模式,最小模式和最大模式。最小模式是单CPU系统,在这种系统中,8086的MN/MX引脚接高电平,系统全部的控制信号都直接由CPU提供。最大模式是多CPU系统,此时MN/MX引脚接低电平,必须通过8288总线控制器对CPU的状态信息进行译码才能产生系统必须的控制信号。

最小模式系统构成如图所示。这时8086的MN/MX引脚接至VCC,它直接产生存储器和I/O端口的读写命令,如IO/M,RD,WR,INTA,直接产生地址锁定信号ALE,控制数据收发器的控制信号DT/R,DEN.

1.地址锁存

8086的AD15~~AD0是地址/数据复用线,即CPU与存储器进行信息交换时,首先在T1状态,先由CPU送出访问存储单元的地址信息到AD15~~AD0上,随后又用在些线来传送数据所以在数据送上总线以前,必须先将地址锁存起来。可用8282或74LS373锁存8086的单向地址AD15~~AD0.图7-9中使用三片8282,这是因为8282只具有8位锁存功能,而8086具有20位地址和一根BHE信号。若系统存储器容量较小,使用不到20位地址信息,也可只用2片8282.图中OE端接地,使锁存器永远处于允许输出状态。引脚STB接8086的ALE输出。在总线周期T1状态,ALE上出现正脉冲,它的下降沿将8282输入端的地址信息存入锁存器,并由输出端送入地址总线。

2.双向数据总线驱动器

CPU可以直接将数据发送到数据总线上。而无需锁存。为了增加总线负载能力,CPU数据总线一般要加上驱动器,且要求双向驱动器,一般采用8位双向驱动器8286或74LS245.由于8086数据总线是16位的,所以要用2片8286.8286的Ai引脚接CPU的ADi,其Di引脚接到系统数据总线D1上,并将8086的DT/R接8286的T引脚,当DT/R为高电平時,数据从CPU发送到数据总线上.DT/R为低电平時,CPU从数据总线上接收数据.8286的OE脚接8086的DEN脚。当8086的DEN为低电平时,才允许数据输入或输出。

3.时钟发生器/驱动器

8086所需时钟脉冲CLK由8284提供.8284输出时钟CLK的频率,取决X1,X2跨接石英晶体的频率。除此以外,8284还向8086提供定时和宽度符合要求的RESET复位信号及符合要求的READY信号。

4.存储器部件

8086能直接寻址1MB存储空间。这个存储空间分为两个512KB存储体。一个存储體由奇地址单元组成,用于存储16数据的高字节,另一个存储体由偶地址单元组成,用于存储16位数据低字节。前者称为奇地址存储器,后者称为偶地址存储体。偶地址存储体的8位数据总线接CPU的数据总线D7~~D0,而奇地址存储体8位数据线接数据总线D15~~D8.地址线A19~~A1同时接到两个存储体,而A0作为偶地址选中信号即A0=0时,选中偶存储体.BHE作为奇地址片选信号,BHE=0时选中奇存储体。所以两个存储体可以同时读出或写入,也可单独选中一个存储体。

5.I/O端口

一个完整的微机系统必须有I/O设备.I/O设备都有端口地址号.CPU通过地址总线发出端口地址,经过端口地址译码器输出,送到端口的片选引脚而选定指定的端口.8086根据执行命令是访问存储器指令还是输入输出指令,来使M/IO控制信号是高电平或是低电平,以区分地址总线上的地址是访问存储器还是访问外设.

六、8086的内存管理

8086CPU有20为地址线,那么它能寻址的范围220B=1048576B=1024KB=1MB。但是在CPU内部的总线是十六位的,它是如何管理1M的空间的呢?秘密在BIU区域存在一个地址加法器,地址线经过这个加法器之后从16位变成了20位。那么这个过程是如何实现的呢?

CPU内部的数据总线和段寄存器都是16位的,用它们做地址寄存器只能寻址64KB单元,但是8086的实际物理地址有1MB,如何解决这个问题呢?采用分段技术。什么是分段技术?将1MB的内存空间分成若干段,每一段的第一个地址称为段首址,并且用段首址来表示这一段的内存地址。段首址必须要能被16整除,为什么呢?这样的话,段首址就可以用16位来保存,低4位全部为零,高16位可放在段寄存器中。

介绍几个概念:

逻辑地址:逻辑地址是一对,包括段首址和偏移地址,如代码段表示为CS:IP。

偏移地址:相对于段首址的偏移量,放在 IP 寄存器里面。

物理地址:实际的内存地址,用20bit表示。

段首址用段寄存器来表示,包括CS(代码段)、DS(数据段)、SS(堆栈段)和ES(附加段)。偏移地址用 IP 来表示。如上图所示。

举个例子:如果一个内存地址(物理地址)为:2304AH,段首址为2304H。那么逻辑地址为:2304H:000AH。这一段内存的实际长度可以用偏移量表示,大小为0000H ~ FFFFH,也就是64KB。

那么逻辑地址是如何变成物理地址呢?这也就是前言中提到的问题。公式如下:

物理地址 = 对应寄存器 * 10H + 段内偏移量

还是刚刚那个例子,2304H * 10H = 23040H

23040H + 0000AH = 2304AH

结论

地址加法器就是进行这样一个运算:物理地址 = 对应寄存器 * 10H + 段内偏移量

对应寄存器指的是:CS、DS、SS、ES 寄存器里面的值,段内偏移量指的是IP寄存器里面的值。如此16的CPU可以寻址1MB的内存空间。

Intel 8086 CPU的更多相关文章

- 8086 CPU 寄存器简介

转载:http://www.cnblogs.com/BoyXiao/archive/2010/11/20/1882716.html 引子 打算写几篇稍近底层或者说是基础的博文,浅要介绍或者说是回顾一些 ...

- [转帖]8086 CPU 寄存器简介

8086 CPU 寄存器简介 https://www.cnblogs.com/BoyXiao/archive/2010/11/20/1882716.html 哎 没看完 感觉好复杂. 引子 打算写几篇 ...

- linux 内核源代码情景分析——Intel X86 CPU 系列的寻址方式

当我们说一个CPU是"16位"或"32"位时,指的是处理器中"算数逻辑单元"(ALU)的宽度.数据总线通常与ALU具有相同的宽度.当Inte ...

- Intel系列CPU的流水线技术的发展

Intel系列CPU的流水线技术的发展 CPU(Central processing Unit),又称“微处理器(Microprocessor)”,是现代计算机的核心部件.对于PC而言,CPU的规格与 ...

- ARM CPU与Intel x86 CPU性能比较

Qualcomm ARM CPU与Intel x86 CPU性能比较 随着移动互联网时代的到来,Qualcomm(高通).Texas Instruments(德州仪器)等基于ARM架构的CPU受到越来 ...

- 8086 cpu为什么要把段地址*16+偏移量形成物理地址呢?

8086 cpu为什么要把段地址*16+偏移量形成物理地址呢? 这是因为,8086地址线是20位,段寄存器是16位,将段寄存器*16实际上就是向左移动4位,形成20位和8086的二十位地址线匹配. I ...

- 8086 CPU 寻址方式

8086 CPU 寻址方式灵活.有以下几种 idata 表示常量 1. [ idata ] 用一个常量来表示地址,可用于直接定位内存单元,但是在 MASM中要显实在的说明 ds 段寄存器, 比如 ...

- AMD和Intel的CPU对比

http://www.lotpc.com/yjzs/5825.html 推荐文章:小白看AMD与intel的cpu架构,AMD慢的原因 CPU核心的发展方向是更低的电压.更低的功耗.更先进的制造工艺. ...

- Intel X86 CPU 系列的寻址方式

Intel X86 CPU 系列的寻址方式 数据总线和地址总线要尽量相同,这个是一个地址就是一个指针.

随机推荐

- 字符串类型日期时间转换为Date类型解析转换异常java.text.ParseException: Unparseable date: “2019-09-27T18:31:31+08:00”

错误的写法: SimpleDateFormat format = new SimpleDateFormat("yyyy-MM-dd HH:mm:ss"); //这里的格式也可以是别 ...

- Linux中添加用户与删除用户

注意:添加用户和删除用户需要root来执行. 添加用户 用useradd命令,例如: # useradd -d/home/tom -s/bin/bash -u1000 tom 这样就添加了新用户to ...

- Online Hard Example Mining 理解

Definition: Online Hard Example Mining (OHEM) is a way to pick hard examples with reduced computatio ...

- DataGrip License server

之前用 Resharper 使用 http://xidea.online 来激活 今天下载一个DataGrip 发现不能使用这个地址,不知道是被封杀了还是不能跟 Resharper 的共用 在网上找到 ...

- 【洛谷 P1641】 [SCOI2010]生成字符串(Catalan数)

题目链接 可以看成在坐标系中从\((0,0)\)用\(n+m\)步走到\((n+m,n-m)\)的方案数,只能向右上\((1)\)或者右下\((0)\)走,而且不能走到\(y=-1\)这条直线上. 不 ...

- border-radius圆角属性

border-radius圆角 当盒子的宽高一样时,设置盒子的border-radius为50%,得到一个圆形 border-radius: 20px 30px 200px 200px; 只写一个值: ...

- 信号的有效值(RMS)估计

% Root Mean Square Value function [retval] = rms1(sig) N = 20; for k = 1 : length(sig)/N - 1 sig_sum ...

- 【转】如何使用jupyter编写数学公式(译)

[1.如何使用jupyter编写数学公式(译)][1] [1]: https://www.jianshu.com/p/93ccc63e5a1b

- phpmyadmin教程

phpmyadmin教程 管理页进入phpmyadmin 打开C:\wamp\apps\phpmyadmin3.5.1下的配置文件:config.inc 修改密码创建与修改数据库.数据表 字段类型 I ...

- 数据库PDO简介

php简介,php历史,php后端工程师职业前景,php技术方向,php后端工程师职业体系介绍. php是世界上使用最广泛的web开发语言,是超文本预处理器,是一种通用的开源脚本语言,语法吸收了c语言 ...