STM32 逐次逼近寄存器型(SAR)模拟数字转换器(ADC)

是采样速率低于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构。

SAR ADC的分辨率一般为8位至16位,具有低功耗、小尺寸等特点。

这些特点使该类型ADC具有很宽的应用范围,例如便携/电池供电仪表、笔输入量化器、工业控制和数据/信号采集等。

顾名思义,SAR ADC实质上是实现一种二进制搜索算法。

所以,当内部电路运行在数兆赫兹(MHz)时,由于逐次逼近算法的缘故,ADC采样速率仅是该数值的几分之一。

SAR ADC的架构

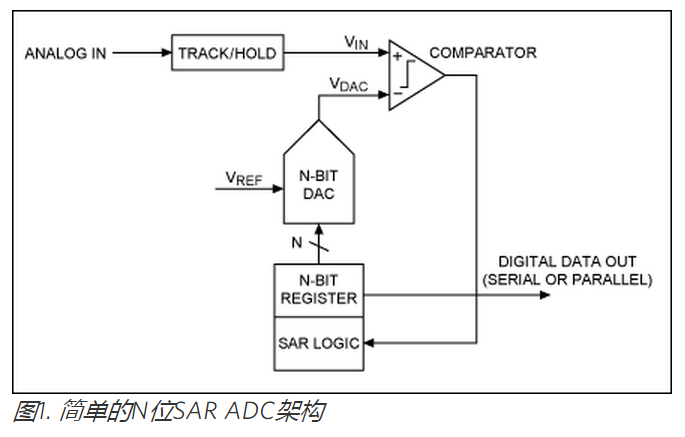

尽管实现SAR ADC的方式千差万别,但其基本结构非常简单(见图1)。

模拟输入电压(VIN)由采样/保持电路保持。

为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100... .00,MSB设置为1)。

这样,DAC输出(VDAC)被设为VREF/2,VREF是提供给ADC的基准电压。

然后,比较判断VIN是小于还是大于VDAC。

如果VIN大于VDAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。

相反,如果VIN小于VDAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。

随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。

这个过程一直持续到LSB。上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内。

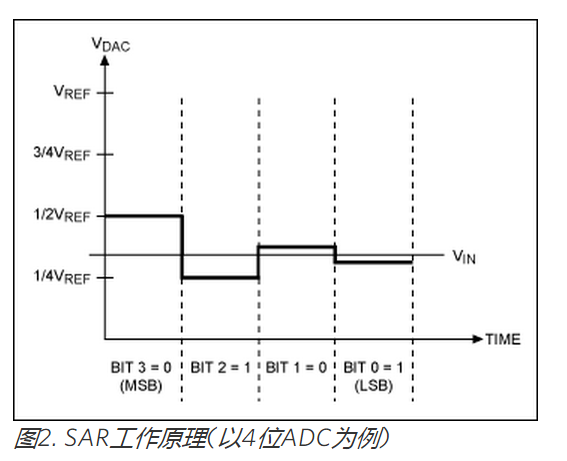

图2给出了一个4位转换示例,y轴(和图中的粗线)表示DAC的输出电压。

本例中,第一次比较表明VIN < VDAC。所以,位3置为0。

然后DAC被置为0100,并执行第二次比较。由于VIN > VDAC,位2保持为1。

DAC置为0110,执行第三次比较。根据比较结果,位1置0,

DAC又设置为0101,执行最后一次比较。

最后,由于VIN > VDAC,位0确定为1。

注意,对于4位ADC需要四个比较周期。

通常,N位SAR ADC需要N个比较周期,在前一位转换完成之前不得进入下一次转换。

由此可以看出,该类ADC能够有效降低功耗和空间,当然,也正是由于这个原因,

分辨率在14位至16位,速率高于几Msps (每秒百万次采样)的逐次逼近ADC极其少见。

SAR ADC的另一个显著的特点是:功耗随采样速率而改变。

这一点与闪速ADC或流水线ADC不同,后者在不同的采样速率下具有固定的功耗。

这种可变功耗特性对于低功耗应用或者不需要连续采集数据的应用非常有利(例如,用于PDA 数字转换器)。

SAR的深入分析

SAR ADC的两个重要部件是比较器和DAC,稍后我们可以看到,

图1中采样/保持电路可以嵌入到DAC内,不作为一个独立的电路。

SAR ADC的速度受限于:

- DAC的建立时间,在这段时间内必须稳定在整个转换器的分辨率以内(如:½ LSB)

- 比较器,必须在规定的时间内能够分辨VIN与VDAC的微小差异

- 逻辑开销

DAC

DAC的最大建立时间通常取决于其MSB的建立时间,原因很简单,MSB的变化代表了DAC输出的最大偏移。

另外,ADC的线性也受DAC线性指标的限制。因此,由于元件固有匹配度的限制,

分辨率高于12位的SAR ADC常常需要调理或校准,以改善其线性指标。

虽然这在某种程度上取决于处理工艺和设计,但在实际的DAC设计中,元件的匹配度将线性指标限制在12位左右。

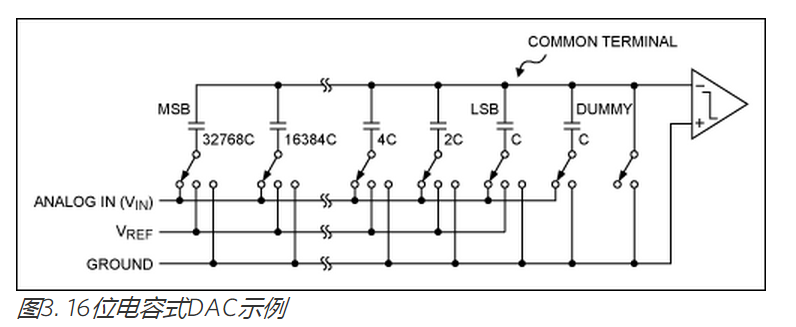

许多SAR ADC采用具有固有采样/保持功能的电容式DAC。

电容式DAC根据电荷再分配的原理产生模拟输出电压,由于这种类型的DAC在SAR ADC中很常用,所以,我们最好讨论一下它们的工作原理。

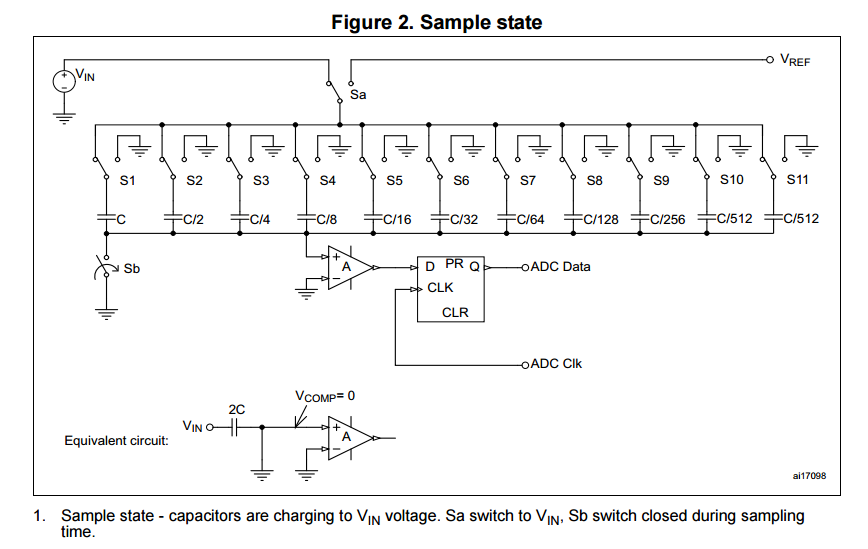

电容式DAC包括一个由N个按照二进制加权排列的电容和一个“空LSB”电容组成的阵列。

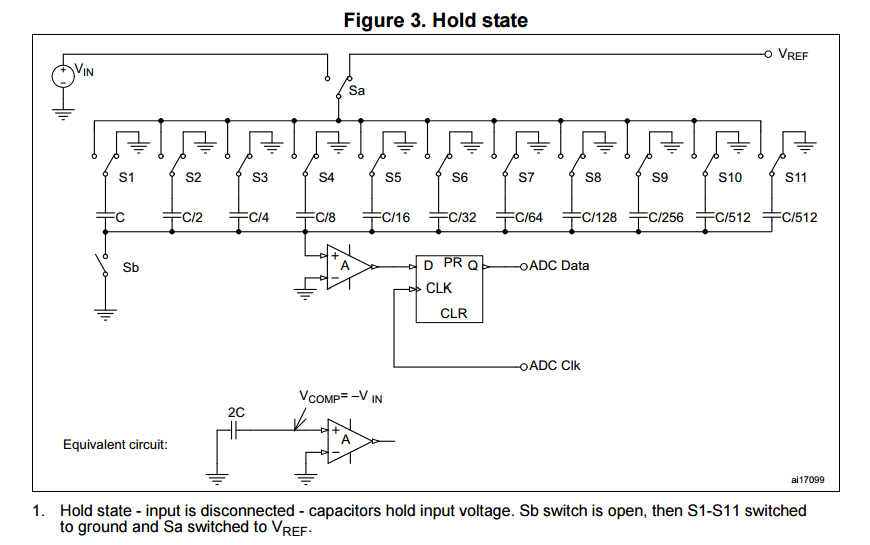

图3是一个16位电容式DAC与比较器相连接的范例。采样阶段,阵列的公共端(所有电容连接的公共点,见图3)接地,

所有自由端连接到输入信号(模拟输入或VIN)。采样后,公共端与地断开,自由端与VIN断开,在电容阵列上有效地获得了与输入电压成比例的电荷量。

然后,将所有电容的自由端接地,驱动公共端至一个负压-VIN。

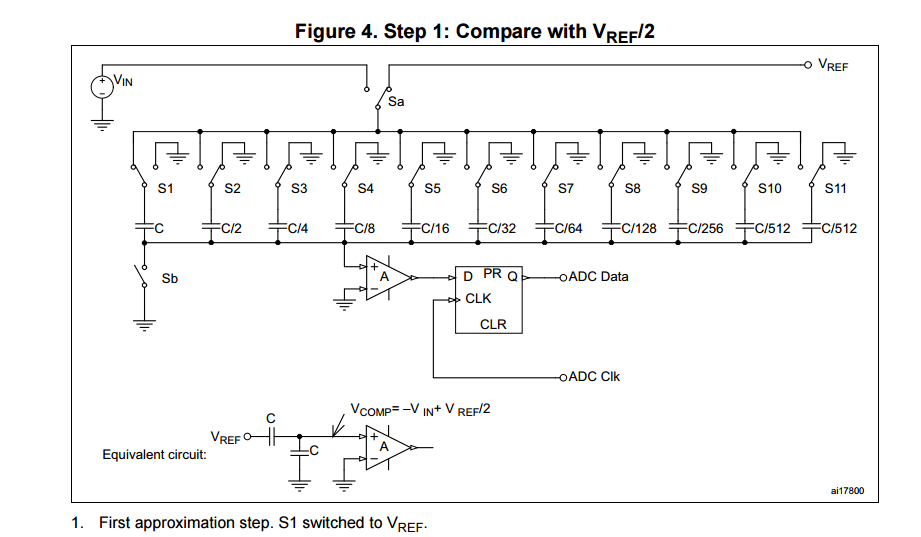

作为二进制搜索算法的第一步,MSB电容的底端与地断开并连接到VREF,驱动公共端电压向正端移动½VREF。

因此,VCOMMON = -VIN + ½ × VREF

如果VCOMMON < 0 (即VIN > ½ × VREF),比较器输出为逻辑1。如果VIN < ½ × VREF,比较器输出为逻辑0。

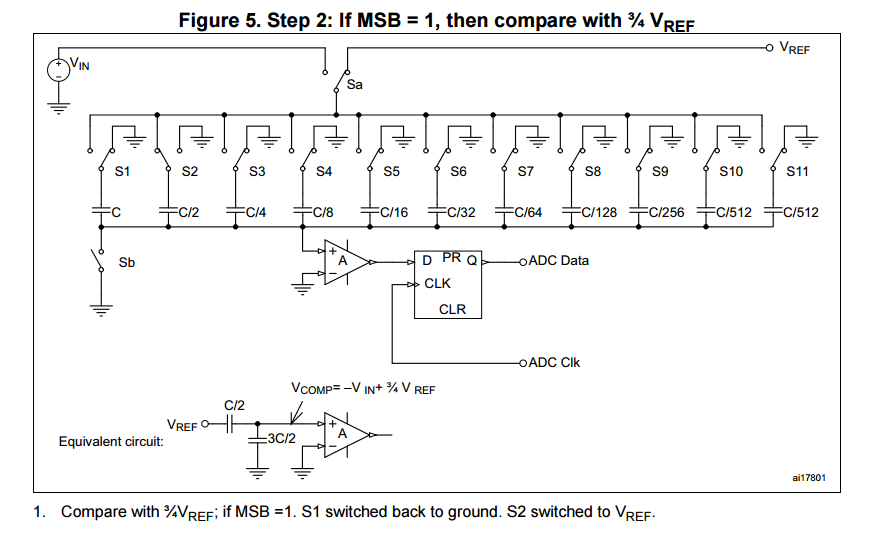

如果比较器输出为逻辑1,MSB电容的底端保持连接至VREF。否则,MSB电容的底端连接至地。

接下来,下一个较小电容的底端连接至VREF,将新的VCOMMON电压与地电位进行比较。

继续上述过程,直至所有位的值均确定下来。

简言之,VCOMMON = -VIN + BN-1 × VREF/2 + BN-2 × VREF/4 + BN-1 × VREF/8 + ... + B0 × VREF/2N-1 (B_为比较器输出/ADC输出位)。

比较器

比较器需要具有足够的速度和精度,尽管比较器的失调电压不影响整体的线性度,

它将给系统传输特性曲线带来一个偏差,为减小比较器的失调电压引入了失调消除技术。

然而,还必须考虑噪声,比较器的等效输入噪声通常要设计在1 LSB以内。

比较器必须能够分辨出整个系统精度以内的电压,也就是说比较器需要保证与系统相当的精度。

SAR ADC与其它ADC结构的比较

与流水线ADC相比

流水线ADC采用一种并行结构,并行结构中的每一级同时进行一位或几位的逐次采样。

这种固有的并行结构提高了数据的吞吐率,但要以功耗和延迟为代价。

所谓延迟,在此情况下定义为ADC采样到模拟输入的时间与输出端得到量化数据的时间差。

例如,一个5级流水线ADC至少存在5个时钟周期的延迟,而SAR只有1个时钟周期的延迟。

需要注意的是,延迟的定义只是相对于ADC的吞吐率而言,并非指SAR的内部时钟,该时钟是吞吐率的许多倍。

流水线ADC需要频繁地进行数字误差校准,以降低对流水线上每一级闪速ADC (即比较器)的精度要求。

而SAR ADC的比较器精度只需与整体系统的精度相当即可。

流水线ADC一般比同等级别的SAR需要更多的硅片面积。

与SAR一样,精度高于12位的流水线ADC通常需要一些某种形式的微调或校准。

与闪速ADC相比

闪速ADC由大量的比较器构成,每个比较器包括一个宽带、低增益预放大器和锁存器。

预放大器必须仅用于提供增益,不需要高线性度和高精度,这意味着只有比较器的门限值才需具有较高的精度。

所以,闪速ADC是目前转换速率最快的一种架构。

通常需要折衷考虑闪速ADC的速度以及SAR DAC的低功耗和小尺寸特性。

尽管极高速的8位闪速ADC (以及它们的折叠/内插变种)具有高达1.5Gsps的采样速率,但很难找到10位的闪速ADC,

而12位(及更高位)闪速ADC还没有商用化的产品。

这是由于分辨率每提高1位,闪速ADC中比较器的个数将成倍增长,同时还要保证比较器的精度是系统精度的两倍。

而在SAR ADC中,提高分辨率需要更精确的元件,但复杂度并非按指数率增长。

当然,SAR ADC的速度是无法与闪速ADC相比较的。

与Σ-Δ转换器相比

传统的过采样/Σ-Δ转换器被普遍用于带宽限制在大约22kHz的数字音频应用。

近来,一些宽带Σ-Δ转换器能够达到1MHz至2MHz的带宽,分辨率在12位至16位。

这通常由高阶Σ-Δ调制器(例如,4阶或更高)配合一个多位ADC和多位反馈DAC构成。

Σ-Δ转换器具有一个优于SAR ADC的先天优势:

即不需要特别的微调或校准,即使分辨率达到16位至18位。

由于该类型ADC的采样速率要比有效带宽高得多,因此也不需要在模拟输入端增加快速滚降的抗混叠滤波器。

由后端数字滤波器进行处理。Σ-Δ转换器的过采样特性还可用来“平滑”模拟输入中的任何系统噪声。

Σ-Δ转换器要以速率换取分辨率。由于产生一个最终采样需要采样很多次(至少是16倍,一般会更多),

这就要求Σ-Δ调制器的内部模拟电路的工作速率要比最终的数据速率快很多。

数字抽取滤波器的设计也是一个挑战,并要消耗相当大的硅片面积。

在不远的将来,速度最高的高分辨率Σ-Δ转换器的带宽将不大可能高出几兆赫兹很多。

总结

综上所述,SAR ADC的主要优点是低功耗、高分辨率、高精度、以及小尺寸。

由于这些优势,SAR ADC常常与其它更大的功能集成在一起。

SAR结构的主要局限是采样速率较低,并且其中的各个单元(如DAC和比较器),需要达到与整体系统相当的精度。

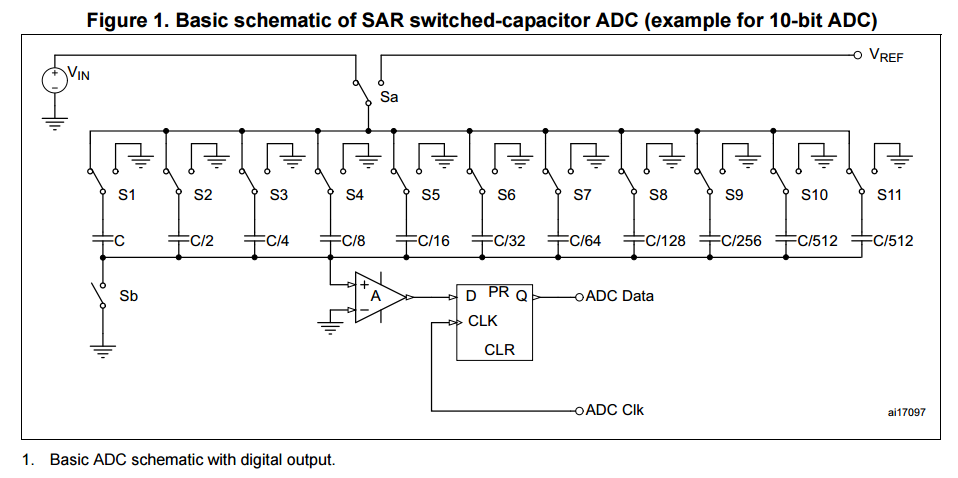

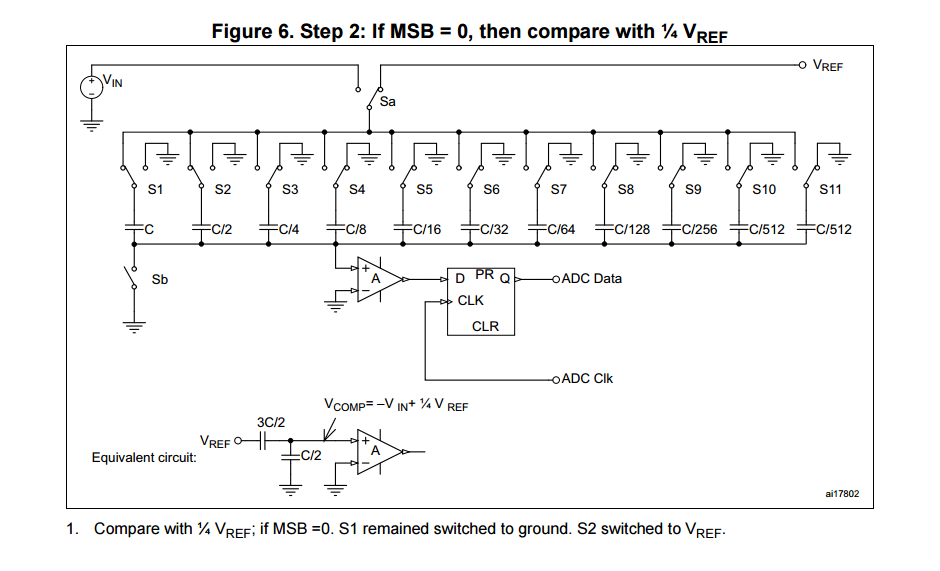

The ADC in STM32x microcontrollers uses the SAR (successive approximation register) principle,

by which the conversion is performed in several steps.

The number of conversion steps is equal to the number of bits in the ADC converter.

Each step is driven by the ADC clock.

Each ADC clock produces one bit from result to output.

ADC internal design is a switched-capacitor type.

The following figures (Figure 1 to Figure 6) explain the principle of ADC operation.

The example given below shows only the first steps of approximation

but the process continues till the LSB is reached.

STM32 逐次逼近寄存器型(SAR)模拟数字转换器(ADC)的更多相关文章

- SAR ADC : 逐次逼近寄存器型(SAR)模数转换器(ADC)

1.为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100... .00,MSB设置为1).这样,DAC输出(VDAC)被设为VREF/2,VREF是提供给ADC的基准电压.然后,比较判断VI ...

- 理解逐次逼近寄存器型ADC:与其它类型ADC的架构对比【转】

转自:http://bbs.dzsc.com/space/viewspacepost.aspx?postid=86760 摘要:逐次逼近寄存器型(SAR)模数转换器(ADC)占据着大部分的中等至高分辨 ...

- stm32寄存器版学习笔记07 ADC

STM32F103RCT有3个ADC,12位主逼近型模拟数字转换器,有18个通道,可测量16个外部和2个内部信号源.各通道的A/D转换可以单次.连续.扫描或间断模式执行. 1.通道选择 stm32把A ...

- STM32的备份寄存器和控制状态寄存器

STM32的备份寄存器和控制状态寄存器 1 备份寄存器用于RTC时钟 RTC时钟可以在掉电以后继续计数,保证时间的延续,但是重新上电以后需要配置,保证之前的计数不会被清除,可以借助备份寄存器实现,备份 ...

- Java 硬件同步机制 Swap 指令模拟 + 记录型信号量模拟

学校实验存档//.. 以经典的生产者消费者问题作为背景. 进程同步方式接口: package method; /** * P表示通过,V表示释放 */ public interface Method ...

- Java硬件同步机制Swap指令模拟+记录型信号量模拟

学校实验存档//.. 以经典的生产者消费者问题作为背景. 进程同步方式接口: package method; /** * P表示通过,V表示释放 */ public interface Method ...

- 【12】python 栈型数据结构模拟、队列型数据结构模拟

一.压栈操作模拟 #__author:"吉*佳" #date: 2018/10/21 0021 #function:栈 # 栈:即是先进后出的一种数据结构 # (1)模拟压栈操作 ...

- STM32的备份寄存器测试

1. 研究STM3的备份寄存器,注意,如果要测试这个例程的话,VBAT不能和VDD接一起,必须分开. 2. 理解,备份寄存器可以有VBAT独立供电,也就是外接电池,备份寄存器在VBAT供电情况下,如果 ...

- STM32先设置寄存器还是先使能时钟

http://zhidao.baidu.com/link?url=gdVNuIgLOJcV37QzbCx0IrFip5pskiPQDWpoZayr_xBEe120p4d_iWtrfDl1d4tSFaH ...

随机推荐

- 转载:分布式文件系统 - FastDFS 在 CentOS 下配置安装部署(2)

原文:http://blog.mayongfa.cn/193.html 一.安装 Nginx 和 fastdfs-nginx-module 安装 Nginx 请看:从零开始学 Java - CentO ...

- 使用console进行 性能测试 和 计算代码运行时间

原文:http://www.tuicool.com/articles/JrARVjv 对于前端开发人员,在开发过程中经常需要监控某些表达式或变量的值,如果使用用 debugger 会显得过于笨重,最常 ...

- C <string.h>常用函数介绍

1. strcpychar *strcpy(char *destin, char *source);功能:将source指向的字符串拷到destin. int main() { ]; "; ...

- vue渲染时对象里面的对象的属性提示undefined,但渲染成功

场景: 从后台请求的数据结构如下: 我的list是对象,而comment又是list里的对象,渲染成功了,却报如下错: 解决办法: 添加一个:v-if

- VeeValidate配置中文的两种方法

使用VeeValidate时遇到的问题,下面是我找到的一些解决办法: VeeValidate一直报错早不到addlocale方法 解决办法:1.卸载掉当前版本,重新安装低版本如2.0.0-rc.25 ...

- pytest六:parametrize-参数化

pytest.mark.parametrize 装饰器可以实现测试用例参数化. 1.这里是一个实现检查一定的输入和期望输出测试功能的典型例子 import pytest @pytest.mark.pa ...

- Tesseract_ocr 字符识别基础及训练字库、合并字库

字符训练网上一搜一大堆,但作为一个初学者而言,字符合并网上却写的很笼统 首先,需要 生成的字符集.tif文件,位置文件 .box ,只要有这两个文件在,就可以合并字典(这个说的很有道理的样子) 好了, ...

- python 全栈开发,Day26(hashlib文件一致性,configparser,logging,collections模块,deque,OrderedDict)

一.hashlib文件一致性校验 为何要进行文件一致性校验? 为了确保你得到的文件是正确的版本,而没有被注入病毒和木马程序.例如我们经常在网上下载软件,而这些软件已经被注入了一些广告和病毒等,如果不进 ...

- 关于trim,ltrim ,rtrim 的 移除问题

今天在PHP中遇到一个问题: echo ltrim('D:/wamp/www/phpnow/demo/','D:/wamp/www/'); echo ltrim('D:/wamp/www/phpnow ...

- 《JavaScript 高级程序设计》第四章:变量、作用域和内存问题

目录 变量的引用 执行环境及作用域 作用域链延长 块级作用域 垃圾回收机制 变量的引用 当一个变量保存了基本数据类型时,此时对于变量的操作(赋值,运算)就是操作这个基本数据的本身,就算是赋值操作,赋值 ...