SPI通信协议(SPI总线)学习

1、什么是SPI?

SPI是串行外设接口(Seria\1.12.ARM裸机第十二部分-I2C通信详解\SPI通信原理\机制.jpg) l Peripheral Interface)的缩写。是 Motorola 公司推出的一

l Peripheral Interface)的缩写。是 Motorola 公司推出的一

种同步串行接口技术,是一种高速的,全双工,同步的通信总线。

2、SPI优点

支持全双工通信

通信简单

数据传输速率块

3、缺点

没有指定的流控制,没有应答机制确认是否接收到数据,所以跟IIC总线协议比较在数据

可靠性上有一定的缺陷。

4、特点

1):高速、同步、全双工、非差分、总线式

2):主从机通信模式

5、协议通信时序详解

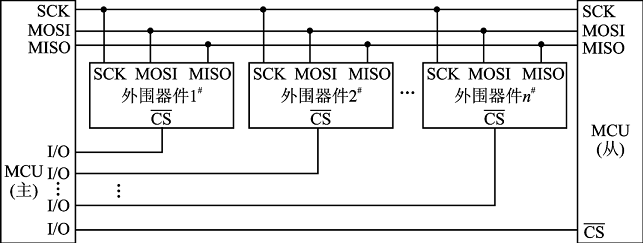

1):SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多

个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共

有的,它们是SDI(数据输入)、SDO(数据输出)、SCLK(时钟)、CS(片选)。

(1)SDO/MOSI – 主设备数据输出,从设备数据输入;

(2)SDI/MISO – 主设备数据输入,从设备数据输出;

(3)SCLK – 时钟信号,由主设备产生;

(4)CS/SS – 从设备使能信号,由主设备控制。当有多个从设备的时候,因为每个从设

备上都有一个片选引脚接入到主设备机中,当我们的主设备和某个从设备通信时将需

要将从设备对应的片选引脚电平拉低或者是拉高。

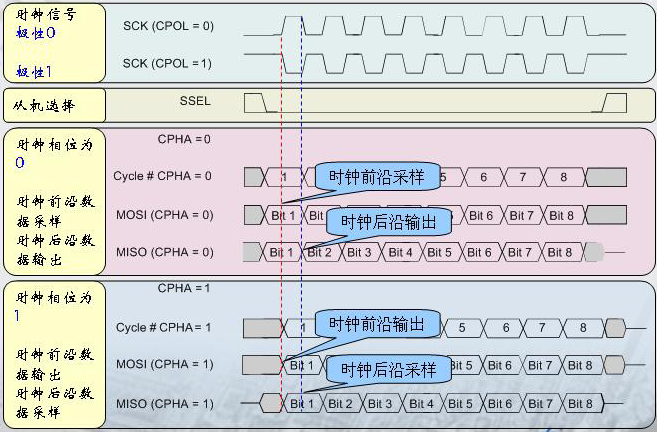

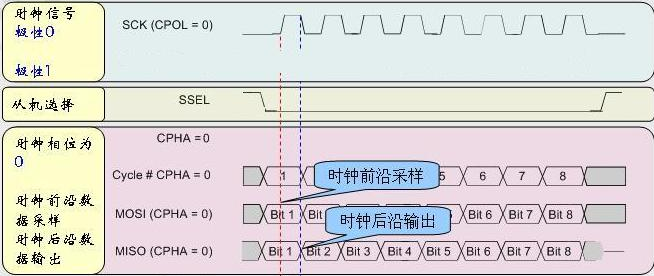

2):需要说明的是,我们SPI通信有4种不同的模式,不同的从设备可能在出厂是就是配

置为某种模式,这是不能改变的;但我们的通信双方必须是工作在同一模式下,所以我们

可以对我们的主设备的SPI模式进行配置,通过CPOL(时钟极性)和CPHA(时钟相位)来

控制我们主设备的通信模式,具体如下:

Mode0:CPOL=0,CPHA=0

Mode1:CPOL=0,CPHA=1

Mode2:CPOL=1,CPHA=0

Mode3:CPOL=1,CPHA=1

时钟极性CPOL是用来配置SCLK的电平出于哪种状态时是空闲态或者有效态,时钟相位CPHA

是用来配置数据采样是在第几个边沿:

CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时

CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时

CPHA=0,表示数据采样是在第1个边沿,数据发送在第2个边沿

CPHA=1,表示数据采样是在第2个边沿,数据发送在第1个边沿

例如:

CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是

SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。

CPOL=0,CPHA=1:此时空闲态时,SCLK处于低电平,数据发送是在第1个边沿,也就是

SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。

CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采集是在第1个边沿,也就是

SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。

CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第1个边沿,也就是

SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

需要注意的是:我们的主设备能够控制时钟,因为我们的SPI通信并不像UART或者IIC通信

那样有专门的通信周期,有专门的通信起始信号,有专门的通信结束信号;所以我们的

SPI协议能够通过控制时钟信号线,当没有数据交流的时候我们的时钟线要么是

保持高电平要么是保持低电平。

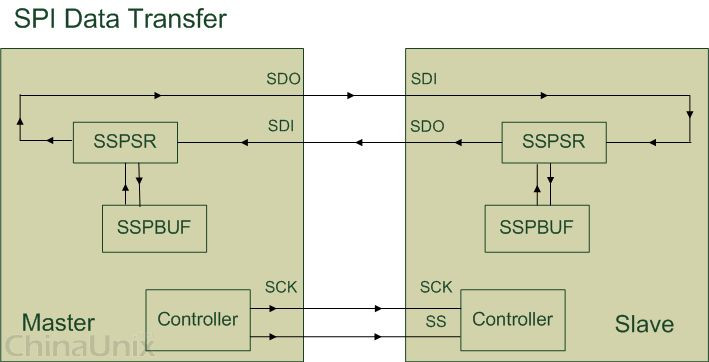

6、内部工作机制

SSPSR 是 SPI 设备内部的移位寄存器(Shift Register). 它的主要作用是根据 SPI

时钟信号状态, 往 SSPBUF 里移入或者移出数据, 每次移动的数据大小由 Bus-Width 以

及 Channel-Width 所决定.

SPI通信协议(SPI总线)学习的更多相关文章

- SPI通信协议(非原创,转载他人,用于学习)

SPI通信协议:1.SPI主从模式:2.数据信号的相位与极性:3.数据帧的格式. 一.什么是SPI? SPI是串行外设接口(Serial Peripheral Interface)的缩写.是 Moto ...

- CAN总线学习系列之二——CAN总线与RS485的比较

CAN总线学习系列之二——CAN总线与RS485的比较 上 一节介绍了一下CAN总线的基本知识,那么有人会问,现在的总线格式很多,CAN相对于其他的总线有什么特点啊?这个问题问的好,所以我想与其它总线 ...

- I2S音频总线学习

IIS音频总线学习(一)数字音频技术 一.声音的基本概念 声音是通过一定介质传播的连续的波. 图1 声波 重要指标: 振幅:音量的大小 周期:重复出现的时间间隔 频率:指信号每秒钟变化的次数 声音按频 ...

- Xilinx AXI总线学习(1)

Xilinx AXI总线学习 1. AXI GPIO 采用的是AXI4-Lite接口 AXI GPIO Block Diagram Block design: 端口描述: AXI GPIO核有哪些寄存 ...

- Avalon总线学习 ---Avalon Interface Specifications

Avalon总线学习 ---Avalon Interface Specifications 1.Avalon Interfaces in a System and Nios II Processor ...

- CAN总线学习系列之三——CAN控制器的选择

CAN总线学习系列之三——CAN控制器的选择 在进行CAN总线开发前,首先要选择好CAN总线控制器.下面就比较一些控制器的特点. 一些主要的CAN总线器件产品 制造商 产品型号 器件功能及特点 Int ...

- CAN总线学习系列之— CAN总线特点介绍

CAN总线学习系列之— CAN总线特点介绍 CAN 总线作为一种工业界的流行总线广泛应于工业自动化.多种控制设备.交通工具.医疗仪器以及建筑.环境控制等各个行业中,它是是一种多主机局域网,所以这样 一 ...

- CAN总线学习总结——错误帧和错误状态

CAN总线学习总结——错误帧和错误状态 标签: 数据 / 错误帧 / 错误状态 / CAN总线 / 总线协议 253 一.五种CAN总线可能发生的错误 1.CRC错误: 接收节点计算出的CRC校验值, ...

- UART,USART,SPI,I2C等总线的介绍与区别20160526

首先来说一下UART和USART的区别: 1.字面意义: UART:universal asynchronous receiver and transmitter通用异步收发器: USART:univ ...

随机推荐

- Ztree学习(-)简单例子

https://www.cnblogs.com/shinhwazt/p/5828031.html ztree包:https://pan.baidu.com/s/1vOgGm_elF-lF0VowoHw ...

- WP8.1 页面跳转,overwrite后退键

In 8.1 we use the below code to navigate between pages: this.Frame.Navigate(typeof(PivotPage)); In 8 ...

- How to Pronounce EVERY

How to Pronounce EVERY Share Tweet Share Tagged With: 2-Syllable Everybody should learn the word ‘ev ...

- Haskell语言学习笔记(44)Lens(2)

自定义 Lens 和 Isos -- Some of the examples in this chapter require a few GHC extensions: -- TemplateHas ...

- textbox显示定位到最后一行(最新一行)

this.textBox1.Select(this.txtMsgInfo.TextLength, 0); this.textBox1.ScrollToCaret();

- SOA (面向服务的架构)

面向服务的体系结构,是一个组件模型,它将应用程序的不同功能单元(称为服务)通过这些服务之间定义良好的接口和契约联系起来.接口是采用中立的方式进行定义的,它应该独立于实现服务的硬件平台.操作系统和编程语 ...

- Js获取iframe子页面全局变量

项目中通过iframe内嵌了一个子页面,子页面定义了一些全局变量,父页面需要获取子页面的全局变量,做了一些测试(我的环境IE10和Firefox32.0.3),得出如下结论: IE下: window. ...

- windows本地blast

详细可参考https://www.jianshu.com/p/2f125cdf8262:https://blog.csdn.net/qq_34296043/article/details/544277 ...

- distinct top執行順序

select distinct top 3 from table; 先distinct后top

- VS文件发布不了,这样设置可以解决

在VS里面新增一些文件的时候,往往发布的时候会发布不了,比如:(*.rdlc,*.p12).在项目里面,这些项目已经包含在项目里了,但是发布后,会发现这些文件并没有被发布出来 解决办法:邮件选择文件, ...