E203 bypass buffer

如果fifo中没有数据,且有输入,则是bypass fifo,同周期内直接把输入数据转到输出数据。如果fifo中有数据,则读取fifo,成为普通的同步fifo。

module sirv_gnrl_bypbuf # (

parameter DP = 8,

parameter DW = 32

) (

input i_vld,

output i_rdy,

input [DW-1:0] i_dat, output o_vld,

input o_rdy,

output [DW-1:0] o_dat, input clk,

input rst_n

); wire fifo_i_vld;

wire fifo_i_rdy;

wire [DW-1:0] fifo_i_dat; wire fifo_o_vld;

wire fifo_o_rdy;

wire [DW-1:0] fifo_o_dat; sirv_gnrl_fifo # (

.DP(DP),

.DW(DW),

.CUT_READY(1)

) u_bypbuf_fifo(

.i_vld (fifo_i_vld),

.i_rdy (fifo_i_rdy),

.i_dat (fifo_i_dat),

.o_vld (fifo_o_vld),

.o_rdy (fifo_o_rdy),

.o_dat (fifo_o_dat),

.clk (clk ),

.rst_n (rst_n)

); // This module is a super-weapon for timing fix,

// but it is tricky, think it harder when you are reading, or contact Bob Hu assign i_rdy = fifo_i_rdy; // The FIFO is bypassed when:

// * fifo is empty, and o_rdy is high

wire byp = i_vld & o_rdy & (~fifo_o_vld); // FIFO o-ready just use the o_rdy

assign fifo_o_rdy = o_rdy; // The output is valid if FIFO or input have valid

assign o_vld = fifo_o_vld | i_vld; // The output data select the FIFO as high priority

assign o_dat = fifo_o_vld ? fifo_o_dat : i_dat; assign fifo_i_dat = i_dat; // Only pass to FIFO i-valid if FIFO is not bypassed

assign fifo_i_vld = i_vld & (~byp); endmodule

module sirv_gnrl_dffs_tb; reg clk=0,rst_n;

reg i_vld, o_rdy;

reg [31:0] i_dat; wire i_rdy, o_vld;

wire [31:0] o_dat; sirv_gnrl_bypbuf #(.CUT_READY(1),.DP(4),.DW(32)) mybuf(.i_vld(i_vld),.i_rdy(i_rdy),.i_dat(i_dat),.o_vld(o_vld),.o_rdy(o_rdy),.o_dat(o_dat),.clk(clk),.rst_n(rst_n)); always #10 clk=~clk; initial

begin

rst_n=1'b1;

i_vld = 1'b0;

o_rdy = 1'b0;

i_dat = 32'h12345678;

#20

rst_n=1'b0;

#80

rst_n=1'b1;

#80

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h8;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h12;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h2;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h11;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h13;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h6;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h22;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h99;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h33;

#20

i_vld = 1'b0;

o_rdy = 1'b1;

i_dat = 32'h17;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h3;

#500 $finish;

end initial

$monitor($time,,,"clk=%b,rst_n=%b,i_vld=%b,o_rdy=%b, i_rdy=%b, o_vld=%b,",clk,rst_n,i_vld,o_rdy,i_rdy,o_vld);

initial

begin

//$dumpfile("dump.vcd");

//$dumpvars;

$fsdbDumpfile("dump.fsdb");

$fsdbDumpvars("+all");

end endmodule

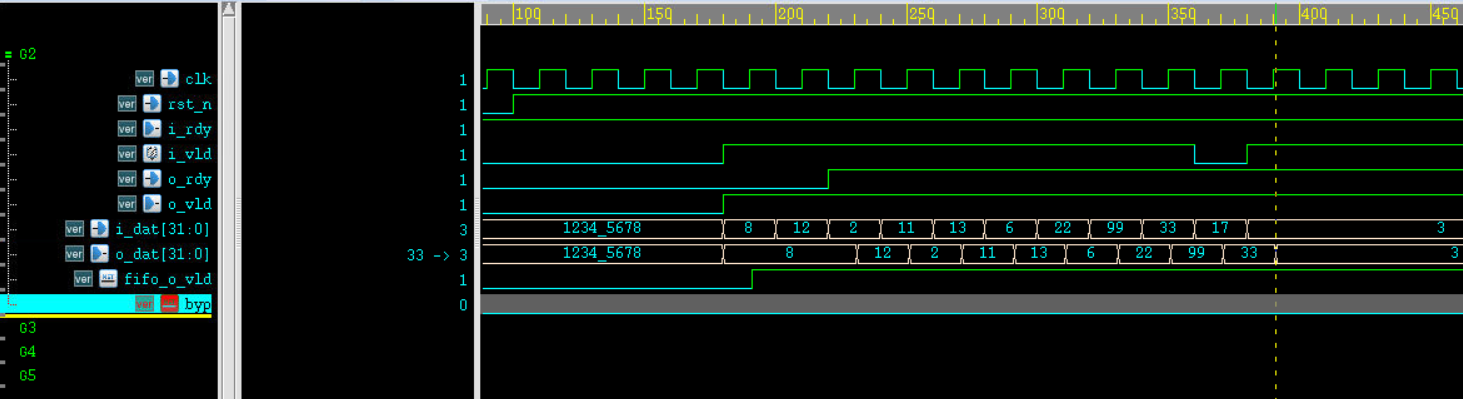

用上面的testbench,可以看到是bypass buffer,fifo_o_vld总为0

module sirv_gnrl_dffs_tb; reg clk=0,rst_n;

reg i_vld, o_rdy;

reg [31:0] i_dat; wire i_rdy, o_vld;

wire [31:0] o_dat; sirv_gnrl_bypbuf #(.CUT_READY(1),.DP(4),.DW(32)) mybuf(.i_vld(i_vld),.i_rdy(i_rdy),.i_dat(i_dat),.o_vld(o_vld),.o_rdy(o_rdy),.o_dat(o_dat),.clk(clk),.rst_n(rst_n)); always #10 clk=~clk; initial

begin

rst_n=1'b1;

i_vld = 1'b0;

o_rdy = 1'b0;

i_dat = 32'h12345678;

#20

rst_n=1'b0;

#80

rst_n=1'b1;

#80

i_vld = 1'b1;

o_rdy = 1'b0;

i_dat = 32'h8;

#20

i_vld = 1'b1;

o_rdy = 1'b0;

i_dat = 32'h12;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h2;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h11;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h13;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h6;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h22;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h99;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h33;

#20

i_vld = 1'b0;

o_rdy = 1'b1;

i_dat = 32'h17;

#20

i_vld = 1'b1;

o_rdy = 1'b1;

i_dat = 32'h3;

#500 $finish;

end initial

$monitor($time,,,"clk=%b,rst_n=%b,i_vld=%b,o_rdy=%b, i_rdy=%b, o_vld=%b,",clk,rst_n,i_vld,o_rdy,i_rdy,o_vld);

initial

begin

//$dumpfile("dump.vcd");

//$dumpvars;

$fsdbDumpfile("dump.fsdb");

$fsdbDumpvars("+all");

end endmodule

如果用上面的testbench,则变成普通的buffer,没有bypass

E203 bypass buffer的更多相关文章

- Method and system for early speculative store-load bypass

In an embodiment, the present invention describes a method and apparatus for detecting RAW condition ...

- 优化ABAP性能(摘录)

1.使用where语句不推荐Select * from zflight.Check : zflight-airln = ‘LF’ and zflight-fligh = ‘BW222’.Endsele ...

- abap 常用 function

ABAP常用函数总结 alv .smartform. excel .text.邮件 .远程访问,FTP服务器... **********常用功能function REUSE_ALV_GRID_DI ...

- Kingsoft Office Writer 2012 8.1.0.3385 - (.wps) Buffer Overflow Exploit (SEH)

#!/usr/bin/python # Exploit Title: Kingsoft Office Writer v2012 8.1.0.3385 .wps Buffer Overflow Expl ...

- Buffer Data

waylau/netty-4-user-guide: Chinese translation of Netty 4.x User Guide. 中文翻译<Netty 4.x 用户指南> h ...

- Tuning 04 Sizing the Buffer Cache

Buffer Cache 特性 The buffer cache holds copies of the data blocks from the data files. Because the bu ...

- Speculative store buffer

A speculative store buffer is speculatively updated in response to speculative store memory operatio ...

- 蜂鸟E203 IFU模块

E203的IFU(instruction fetch unit)模块主要功能和接口如下: IFU的PC生成单元产生下一条指令的PC. 该PC传输到地址判断和ICB生成单元,就是根据PC值产生相应读指请 ...

- E203 同步fifo

1. 输入端, 输入信号, i_vld,表示输入请求写同步fifo,如果fifo不满,则fifo发送i_rdy 到输入端,开始写fifo.i_vld和i_rdy是写握手信号. 2.输出端 o_rdy表 ...

随机推荐

- IntelliJ IDEA UML插件

在IntelliJ IDEA Ultimate 版本中自带了一个UML插件:UMLSupport 查看了Community版本和AndroidStudio 发现没有这个插件. 要使用这个插件导出需要的 ...

- 论文学习-混沌系统以及机器学习模型-11-29-wlg

混沌系统以及机器学习模型 概述: 必要条件下: negative values of the sub-Lyapunov exponents. 通过rc方法, 可以在参数不匹配的情况下,实现输入信号,混 ...

- Netty高性能组件——FastThreadLocal源码解析(细微处见真章)

1. 前言 netty自行封装了FastThreadLocal以替换jdk提供的ThreadLocal,结合封装的FastThreadLocalThread,在多线程环境下的变量提高了ThreadLo ...

- [20190515]热备份模式与rman冲突.txt

[20190515]热备份模式与rman冲突.txt --//别人的系统做dg时打开热备份模式,忘记关闭,做rman备份时报错.做一个记录.--//实际上也怪自己,实施时没有讲清楚.通过例子说明: 1 ...

- PHP配置篇(一)--php开启redis扩展

因为最近要用到Redis,下面记录下如何给PHP开启redis的扩展. 一.安装redis 1.安装redis:https://github.com/MSOpenTech/redis/releases ...

- SQL Server阻塞的检查

1. 阻塞 除了内存.CPU.I/O这些系统资源以外,阻塞和死锁是影响数据库应用性能的另一大因素. 所谓的「阻塞」,是指当一个数据库会话中的事务,正在锁定其他会话事务想要读取或修改的资源,造成这些 ...

- Python中 if __name__ == '__main__' 的作用

Python文件可以直接运行,也可以 import 到其它文件中使用 if __name__ == '__main__' 就是控制代码在这两种情况下的执行过程 每个Python模块都包含内置变量,直接 ...

- CodeForces - 1236B (简单组合数学)

题意 有n种物品和m个背包,每种物品有无限个,现将若干个物品放到这些背包中,满足: 1.每个背包里不能出现相同种类的物品(允许有空背包): 2.在所有的m个背包中,每种物品都出现过. 求方案数,对10 ...

- 6、zabbix自定义监控

一.概述 为什么需要自定义监控呢? 虽然zabbix已经给我们准备好了很多的模板,但是有的东西还是无法监控,这时候就要我们自定义监控了. 自定义监控的思路? 比如我们现在想要监控这个值,如下所示,模板 ...

- LeetCode 二进制问题

338. Counting Bits(计算小于n的各个数值对应的二进制1的个数) 思路:通过奇偶判断,if i是偶数,a[i]=a[i/2],if i是奇数,a[i]=a[i-1]+1. class ...