基于FPGA的1553B通信模块的设计(转)

reference:http://www.21ic.com/app/eda/201808/798483.htm

https://www.milstd1553.com/

摘 要: 提出一种将FPGA与PowerPC芯片结合,实现MIL-STD-1553B通信模块的技术方案。详细讨论了该系统的结构、1553B总线协议在FPGA上的实现以及系统的软件结构等关键技术。该系统方案与采用专用的协议芯片实现1553总线接口的方法相比,具有更灵活、成本更低、可移植性好等特点。

关键词: MIL-STD-1553B;FPGA;PowerPC

MIL-STD-1553总线是美国国防部制定的一种具有可确定性且传输可靠的数据总线,被广泛应用于军用飞机、军用车辆以及舰载等领域中。目前,1553B总线接口模块的实现主要有2种方式:一种是采用专用的协议芯片(如DDC公司的BU-61580、HOLT公司的HI-6110等);另一种是采用FPGA与CPU结合实现1553B的协议模块。

本系统采用后一种方式,硬件上采用PowerPC芯片PPC405EP与Xilinx的FPGA芯片XC3S200为系统的核心芯片,使用VHDL语言实现1553B的总线协议。与采用专用的协议芯片实现1553总线接口的方法相比,该方案的成本很低,也很容易根据需要进行功能扩展,使用灵活。

1、 1553总线分析

在MIL-STD-1553总线上有总线控制器、远程终端和监视器3种设备。其中,最重要的是总线控制器(BC-Bus Controller),总线上的任何操作都是由BC发起的(通过发不同的命令控制总线上的数据传输);远程终端(RT-Remote Terminal)接收BC的命令,并按命令进行相应数据传输;总线监视器(BM-Bus Monitor)对总线上的数据进行接收和存储。

1553B总线上数据的交互是基于消息机制的。该标准定义了10种消息传输格式,而这10种传输格式都采用前述的3种字类型,总线上的数据传输就是采用这10种消息传输格式中的一种。其传输过程如下:BC通过总线发送某种命令字,所有的RT接收该命令字,并将命令字中的地址域与自己的地址相比较,相同则接收该命令字;随后,RT对命令字进行解析,根据命令完成相应的操作(接收数据字、发送数据字、同步、自检等)。这些操作都会产生相应的状态字发送给BC。BC通过状态字来判断RT是否工作正常。如果RT接收到的命令字中的终端地址是广播地址,则所有的RT都接收该命令,但都不返回状态字给BC。

2 、系统设计

2.1 系统结构

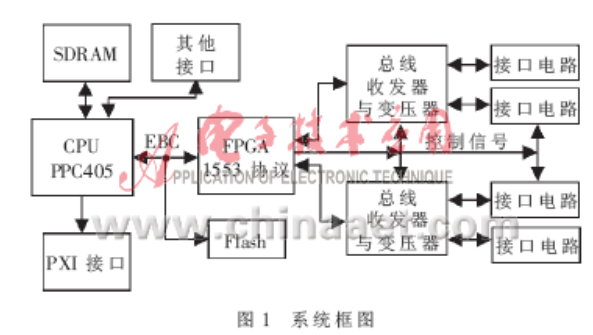

系统结构如图1所示。1553B的协议处理以及编解码都由FPGA实现。在同一电路上集成BC、BM和R/T功能,可以通过软件设置来选择所需的功能。同时,其综合了通信和测试功能,既能够检测出各种可能出现的错误,又能根据测试要求产生各种错误。

CPU芯片采用AMCC公司的PowerPC405EP。该芯片不仅包括一个高性能的RISC处理器内核,还有SDRAM控制器、PCI总线接口、以太网接口、外部ROM和周边资源控制及串行口、IIC接口、通用I/O口等,支持DMA功能。

系统中的PXI接口是用PowerPC405EP的PCI接口与外部的开关电路扩展实现的。CPU通过EBC总线与1553模块通信,其接口电路由FPGA实现。图1所示接口电路主要完成通道选择、数据环回等功能。

2.2 总体方案

1553B总线协议由硬件和软件配合实现。整体设计思路是:硬件和软件采用中断和查询2种方式,通过一个共享的数据Buffer进行信息交互。下面介绍系统整体数据收发流程。本系统的软硬件功能就是根据该流程进行分工和实现的。

2.2.1 数据发送流程

上层软件以数据结构的形式将控制和数据信息传输给硬件逻辑电路,硬件电路自动地将数据按照控制信息发送到1553B总线上。CPU向硬件逻辑发送数据时,首先应检测上次的发送是否已经结束。具体方法是:读通道状态寄存器发送完成位,如果有效,表示上次发送已经结束了。只有检测到上次发送结束了,才能进行数据的发送操作。硬件电路在将数据发送完之后,会产生中断请求。软件根据中断请求去查询状态寄存器,决定下一步的操作。传输流程简述如下:

(1)CPU向数据发送FIFO写入1个指令字/状态字和错误控制信息;

(2)CPU向通道控制寄存器写入发送使能信号;

(3)CPU向数据发送FIFO写入0~32次数据和错误控制信息;

(4)硬件逻辑检测到发送使能信号;

(5)硬件逻辑自动将存储在FIFO中的数据顺序取出;

(6)硬件逻辑根据错误控制信息对数据进行相应处理后将数据发送到1553B总线上;

(7)硬件逻辑在发送消息结束2 μs后,置发送完成状态位,并产生中断信号。

2.2.2 数据接收流程

硬件逻辑接收到1553B总线上的数据后,对该数据进行错误检测,并将相应的状态信息和数据组合起来一起存入到接收FIFO中。当接收FIFO达到一定容量后,便向CPU产生中断信号。CPU对FIFO进行读操作,将数据和状态取出。接收步骤如下:

(1)硬件逻辑接收总线上的数据;

(2)硬件逻辑对数据进行错误检测,产生状态信息;

(3)硬件逻辑将数据和状态信息写入接收FIFO中;

(4)当接收FIFO达到一定容量时便产生中断信号;

(5)CPU响应外部中断;

(6)CPU对FIFO进行读操作,将状态信息和数据取走;

(7)CPU对状态信息进行解析,决定对数据的处理。

3 、总线编解码的FPGA实现

本系统中的FPGA芯片采用Xilinx公司的Spartan-3A XC3S200。该系列产品采用了90 nm工艺,支持业界最广泛的I/O标准(26种),具备独特的功耗和配置功能以及防克隆(anti-cloning)安全性优势。

FPGA的功能全部采用VHDL语言实现,其功能框图如图2所示。其主要完成的工作有:(1)曼彻斯特码的编解码,包括串/并转换。(2)1553B协议的消息的解析,包括同步头的识别,以及各种错误的识别、奇偶校验等。(3)1553B协议的消息发生,包括同步头的产生、各种状态位的产生以及各种错误信息的产生。(4)与CPU接口的实现。(5)各种中断信号的实现。(6)定时和超时控制电路等。

3.1 总线发送电路实现

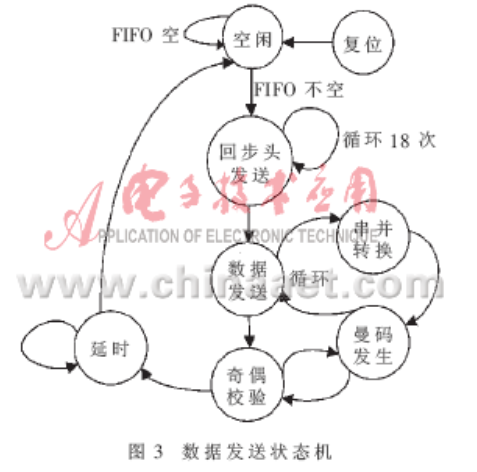

如果没有注入错误的要求,编码器的实现就比较简单,只需要用若干倍1553B的传输速率(本设计采用12倍频)将并行数据转换为串行数据,加上相应的同步头即可。在硬件上数据发送电路主要由一个状态机、双口FIFO、注入错误标志寄存器以及控制电路组成。状态机的状态图如图3所示。复位之后,该状态机在每个时钟的上升沿都检测FIFO中是否有数据,若为空则停留在空闲状态。一旦上层软件通过EBC接口向FIFO写入数据后, 硬件电路自动将数据读出。进入到同步头发送状态,硬件电路根据命令寄存器的控制字送出相应的串行同步头,随后进入数据发送状态。在每个时钟沿,移位寄存器将数据寄存器的数据移出,进行曼码编码后发出,同时,数据计数器自动加1。当计数值为16时,则转入到奇偶校验状态,将异或得到的检验位编码后发出。

本系统要求具有测试功能,主要有以下注入错误的要求:

(1)EI_BITCOUNT:消息中指定数据的位数错误(不为16位);

(2)EI_PARITY:消息中指定数据的校验位错误;

(3)EI_SYNC:错误的同步头;

(4)EI_WORDCOUNT:使消息中的数据长度不等于命令字中的长度;

(5)EI_MIDBIT:指定数据位过零点错误,比期望位置延时300 ns;

(6)EI_MIDSYNC:同步头的过零点错误,比期望位置延时300 ns;

(7)EI_BIPHASE:整个位时无过零点。

硬件电路要求在状态机中加入对应的电路,检测错误寄存器中的标志位,并产生对应的错误。

3.2 总线接收电路实现

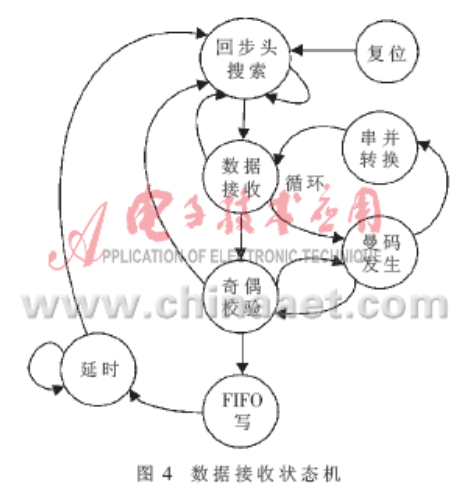

无论是BC还是RT都需要对收到的数据进行解析。接收电路的主要功能有:曼码的解码、串并转换、同步头检测、奇偶校验以及各种错误的检测。如图4所示,状态机复位之后进入同步头搜索状态。硬件电路以12倍1553总线传输速率的频率去检测几种同步头。若收到同步头,则将状态寄存器中的对应位置位,并转入数据接收状态;否则,停留在该状态下。数据接收状态下,移位寄存器在时钟沿将经过解码的数据移入。在数据计数器计数到16之后转入到奇偶校验状态;之后,将数据和状态写入到FIFO中。硬件电路在状态机的每个阶段都要检测各种错误,如果出错则回到同步头搜索状态。同时,产生错误标志和中断信号。

3.3 硬件中断功能的实现

如上所述,本系统软件和硬件的通信主要通过中断和查询的方式进行信息交互。硬件电路实现了如下中断功能:

(1)每收到1个命令/状态字产生中断;

(2)数据长度计数器中断和使能。软件对收到的命令/状态字进行解析,如果有数据准备接收,将数据长度值写入数据长度计数器,同时使能计数器。硬件收到1个数据字,递减计数器,直到0产生中断,同时禁止该数据计数器中断;

(3)接收FIFO半满或3/4满产生中断;

(4)接收FIFO全满(overflow)产生中断;

(5)发送FIFO为空产生中断;

(6)中断状态/使能寄存器;

(7)等待超时中断(接收数据长度不够);

(8)数据计数器中断处,打上时间戳;收到每个命令/状态字打上时间戳;发送的命令/状态字的同步头过零点打上时间戳。

4 、软件设计

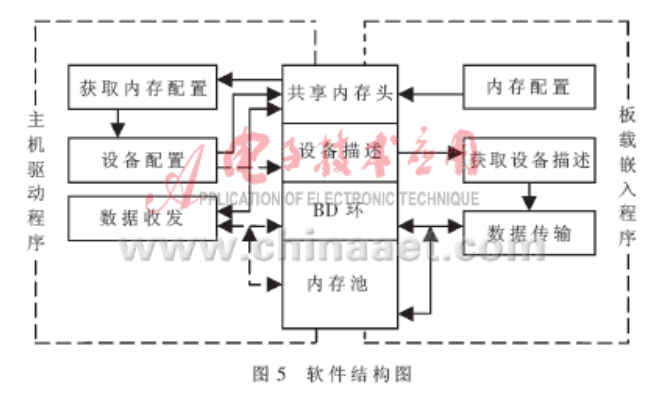

软件设计包括板载嵌入程序、主机驱动程序设计。板载嵌入程序和主机驱动程序通过共享PPC外挂内存来完成数据交互,板载嵌入式程序通过访问FPGA的寄存器和FIFO来完成硬件操作和数据收发。其结构如图5所示。

主机驱动程序的开发平台是LabWindows/CVI,为用户提供方便实用的API接口函数及其定义。

嵌入式程序的开发平台是Tornado2.2。该程序主要完成模块的初始化、各通道BCRTBM的消息解析、中断服务处理、与主机交互等功能。其中消息解析是嵌入式程序的核心部分。

当模块选项为多功能模块时,要求各通道在同一个工作时期可同时作为BC、BM和最多31个RT进行工作。当被测系统的可得终端有限时,又希望获得充足完备的测试,多功能模块将提供充足的终端用以测试。为了能同时且正确充当BC、BM、RT 3个不同的角色,模块的嵌入式程序设计引入了可编程逻辑设计的状态机设计思想。BC、BM、RT各自拥有自己的状态机。

5 、测试与结论

图6所示为1553收发器仿真波形图。由于篇幅原因,只显示了部分功能。该仿真主要验证了如下过程:软件通过EBC总线接口将3个待传输数据以及对应的控制字写入到FIFO中,经过硬件电路转换为串行数据输出到差分输出端;输出再环回到差分输入端,经过解码电路再写入到FIFO中,产生中断信号,并被软件通过EBC总线将数据和状态读回。

经过仿真和实际验证,本系统满足1553B总线协议的要求。同时,该设计已经成为产品,在实际中得到了应用。

参考文献

[1] Condor Engineering Inc.MIL-STD-1 553 Tutorial[Z].2000.

[2] Data Device Corporation.MIL-STD-1 553 DESIGNER′S GUIDE[Z].1998.

[3] Applied Micro Circuits Corporation.PowerPC 405EP Embedded Processor datasheet[EB/OL].http://www.appliedmicro. com/MyAMCC/retrieveDocument/PowerPC/405EP/PPC405EP_DS2003.pdf,2003.

[4] Xilinx INC.Spartan-3 FPGA Family:Complete Data Sheet [EB/OL].http://www.xilinx.com/support/documentation/data_sheets/ds099.pdf,2008.

基于FPGA的1553B通信模块的设计(转)的更多相关文章

- 基于FPGA的XPT2046触摸控制器设计

基于FPGA的XPT2046触摸控制器设计 小梅哥编写,未经许可,文章内容和所涉及代码不得用于其他商业销售的板卡 本实例所涉及代码均可通过向 xiaomeige_fpga@foxmail.com 发 ...

- 基于FPGA的SPI FLASH控制器设计

1.SPI FLASH的基本特征 本文实现用FPGA来设计SPI FLASH,FLASH型号为W25Q128BV.支持3种通信方式,SPI.Dual SPI和Quad SPI.FLASH的存储单元无法 ...

- 012 基于FPGA的网口通信实例设计【转载】

一.网口通信设计分类 通过上面其他章节的介绍,网口千兆通信,可以使用TCP或者UDP协议,可以外挂PHY片或者不挂PHY片,总结下来就有下面几种方式完成通信: 图8‑17基于FPGA的网口通信实例设计 ...

- verilog实验2:基于FPGA的59秒计时器设计

一.实验任务 利用四个数码管显示59秒计时器. 二.代码实现 将开发板的48M晶振分频出1M,然后计数器累加,将计数器结果显示在数码管上.低位逢十进一,第二位逢五进一,依次构成59秒计时器. 部分代码 ...

- 基于FPGA的Cordic算法实现

CORDIC(Coordinate Rotation Digital Computer)算法即坐标旋转数字计算方法,是J.D.Volder1于1959年首次提出,主要用于三角函数.双曲线.指数.对数的 ...

- 优化基于FPGA的深度卷积神经网络的加速器设计

英文论文链接:http://cadlab.cs.ucla.edu/~cong/slides/fpga2015_chen.pdf 翻译:卜居 转载请注明出处:http://blog.csdn.net/k ...

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- 基于FPGA的HDMI显示设计(三)

上一篇:基于FPGA的VGA显示设计(二) 10月10日 ~ 20日期间实习,令我万万没想到的是实习题目是 “便携式高清电视显示屏测试系统原型设计” 也就是 “基于FPGA的视频显示”. 实习要求用 ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

随机推荐

- Olap学习笔记

数据仓库建设--OLAP和数据立方体概念 http://student-lp.iteye.com/blog/2263154 OLAP(On-LineAnalysis Processing)在线分析处理 ...

- os.path.join

os.path.join()函数: 第一个以”/”开头的参数开始拼接,之前的参数全部丢弃. 以上一种情况为先.在上一种情况确保情况下,若出现”./”开头的参数,会从”./”开头的参数的上一个参数开始拼 ...

- 记录tiny6410 jlink 命令行调试linux-2.6.38内核

1\首先启动nandflash uboot->linux内核->文件系统,进入文件系统命令行 2\启动JLinkGDBServer -device ARM11 3\启动arm-none-e ...

- python fabric的用法

1. Fabric的任务运行规则根据Fabric Execution model的说明,fabric默认以串行方式运行tasks,具体而言: 1)在fabfile及其import文件中定义的task对 ...

- Porsche Piwis Tester II V14.000 with CF30 Laptop at autonumen.com

Porsche piwis tester ii is the latest professional tester for Porshe,the most poweful diagnose and o ...

- LR访问Https接口

实操篇 第一步:需要跟开发或者运维要到要访问的https接口的证书(有关证书的问题我们在原理中有解释). 第二步:确定要来的证书的格式是否为pem格式的.首先,LR只能够识别pem格式的证书而且是DE ...

- Redis学习-sorted set数据类型

sorted set 是有序集合,它在 set 的基础上增加了一个顺序属性,这一属性在添加修 改元素的时候可以指定,每次指定后,会自动重新按新的值调整顺序. zadd key score member ...

- centos7救援模式--单机模式(单用户模式)

前序 经典问题: 单机模式, 当系统忘记某用户登录密码的时候可以解决密码重置问题 操作 1 开机的时候出现选择进入系统的界面时, 按E键 2 选择定位到ro这里, 替换成rw init=/sysroo ...

- D7 割点 割边 强连通分量

今天几道是模板题: 第一道:(粘不了链接呜呜呜) 题目描述 n个城市之间有通讯网络,每个城市都有通讯交换机,直接或间接与其它城市连接.因电子设备容易损坏,需给通讯点配备备用交换机. 但备用 交换机数量 ...

- 王之泰201771010131《面向对象程序设计(java)》第八周学习总结

第一部分:理论知识学习部分 第六章 第六章知识点主要分为1. 接口 2. lambda表达式 3. 内部类 4. 代理 1. 接口 1) Java为了克服单继承的缺点,Java使用了接口, 一个类可以 ...