Verilog 加法器和减法器(8)-串行加法器

如果对速度要求不高,我们也可以使用串行加法器。下面通过状态机来实现串行加法器的功能。

设A=an-1an-2…a0, B=bn-1bn-2…b0,是要相加的两个无符号数,相加的和为:sum=sn-1sn-2…s0。我们现在要设计一个电路,在时钟周期内处理一位相加的串行加法。加法过程一开始进行a0,b0的相加,在下一个时钟周期完成 a1,b1和第0位进位的相加,并依次完成所有的加法。

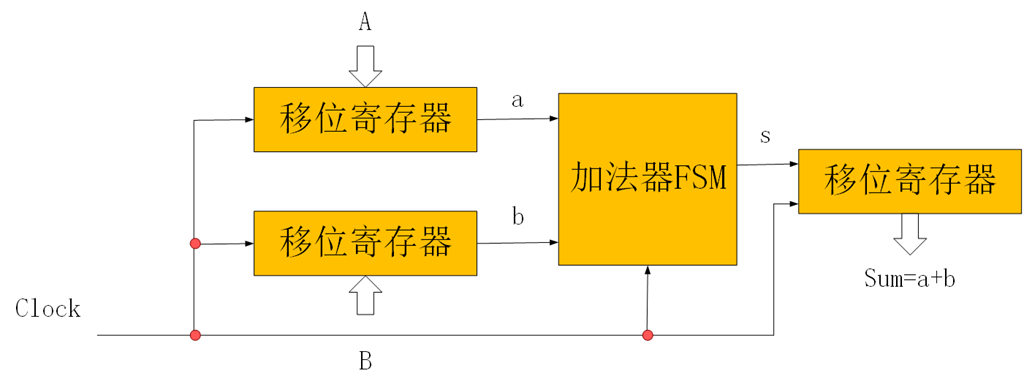

下图的方案中,3个移位寄存器用来保存A,B以及和Sum。假设这些寄存器有并行加载功能,先将加A,B的值载入这些寄存器,在时钟的每个周期,通过加法器FSM控制每位相加,在周期的最后把输出的结果移入Sum寄存器。我们使用上升沿触发的触发器,这样所有数据在时钟的上升沿及各个触发器的传播延迟后发生变化,此时三个移位寄存器内容右移:将加法结果移入Sum,并将下一对 ai,bi加载至加法器FSM。

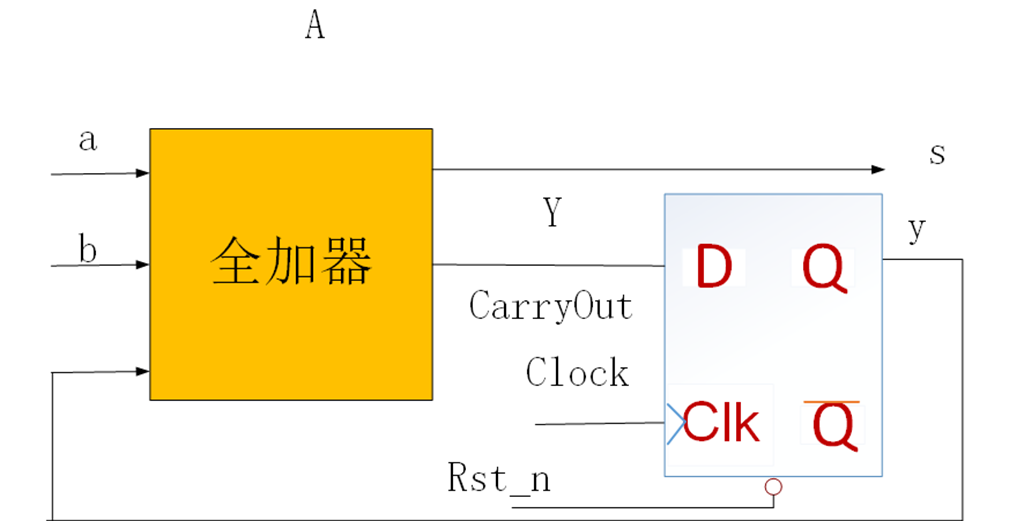

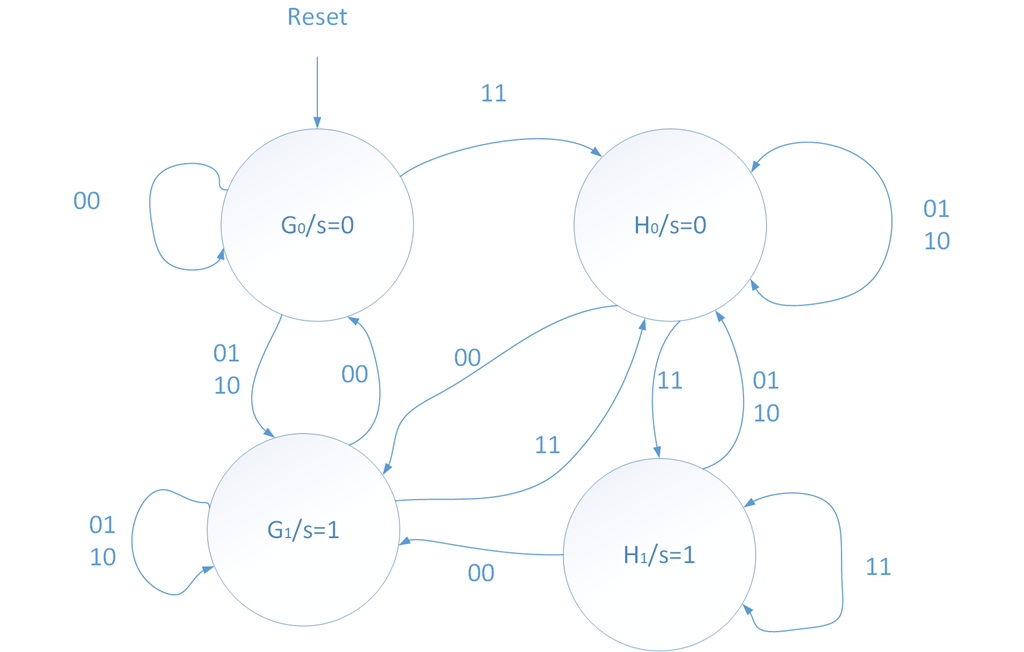

下面是加法器FSM的图:

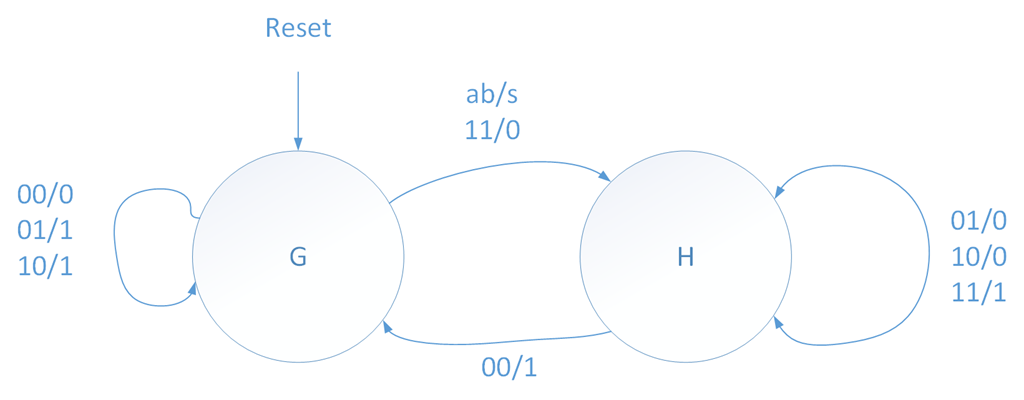

我们来设计状态机,假设有两个状态:状态G,进位为0,状态H,进位为1。则状态图如下,输出s取绝与当前状态(进位)和输入a,b的值,所以这是mealy型状态机。

在状态G中,输入00,则仍在状态G,输出为0,为01和10时候,仍在状态G,输出为1,如果输入为11,则转到状态H,输出0。

在状态H中,输入11,仍在状态H,输出1,输入为01和10时候,仍在状态H,输出为0,如果输入为00,则转到状态G,输出为1。

这个mealy型串行加法器的状态表如下:

根据状态表,利用卡诺图简化,有下列表达式,显然它就是全加器的输出表达式。

Y = ab+ay+by

s = a^b^y

| 现在状态 | 下一状态(ab) | 输出s | ||||||

| 00 | 01 | 10 | 11 | 00 | 01 | 10 | 11 | |

| G | G | G | G | H | 0 | 1 | 1 | 0 |

| H | G | H | G | G | 1 | 0 | 0 | 1 |

| 现在状态 | 下一状态(ab) | 输出(ab) | ||||||

| 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | |

| y | Y | s | ||||||

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

下面是verilog实现代码,首先是移位寄存器的代码,该移位寄存器带有使能输入E,E=1时,寄存器的内容将在时钟的上升沿开始从左到右。E=0,可以阻止移位寄存器内容发生改变。

module shiftrne(R,L,E,w,clk,Q); parameter n=8;

input [n-1:0] R;

input L,E,w,clk;

output reg [n-1:0] Q; integer k; always @(posedge clk) begin

if(L)

Q<=R;

else if(E) begin

for(k=n-1; k>0; k=k-1)

Q[k-1] <= Q[k];

Q[n-1] <=w;

end end endmodule

下面是mealy型串行加法的代码,代码中首先例化了三个移位寄存器。代码中还包括一个递减计数器,用来完成n位加法并输出至移位寄存器后,停止加法器。

代码中我们采用高电平复位信号。输出端的使能信号为Run信号,只要Run信号为1,递减计数器每个时钟周期都会递减。

module serialadd(A,B,Rst,clk,S);

input [7:0] A,B;

input Rst,clk;

output wire [7:0] S; reg [3:0] Count;

reg s,y,Y;

wire [7:0] QA,QB;

wire Run;

parameter G=1'b0, H=1'b1; shiftrne #(.n(8)) shift_A(.R(A),.L(Rst),.E(1'b1),.w(1'b0),.clk(clk),.Q(QA));

shiftrne #(.n(8)) shift_B(.R(B),.L(Rst),.E(1'b1),.w(1'b0),.clk(clk),.Q(QB));

shiftrne #(.n(8)) shift_S(.R(8'b0),.L(Rst),.E(Run),.w(s),.clk(clk),.Q(S)); //adder FSM

//output and next state cominatioal circuit always @(QA,QB,y) begin case (y)

G:

begin

s = QA[0]^QB[0];

if(QA[0]&QB[0]) Y=H;

else Y=G; end

H:

begin

s = QA[0]~^QB[0];

if(~QA[0]&~QB[0]) Y=G;

else Y=H; end

default:

Y = G;

endcase

end //sequential block

always @(posedge clk)

if(Rst)

y<=G;

else

y<=Y; //control shift proecess

always @(posedge clk)

if(Rst) Count=8;

else if(Run) Count = Count-1; assign Run = |Count;

endmodule

testbench代码为:

`timescale 1ns/1ns

`define clock_period 20 module serialadd_tb;

reg clk;

reg Rst; reg [7:0] A,B;

wire [7:0] S; serialadd serialadd0(.A(A),.B(B),.Rst(Rst),.clk(clk),.S(S));

//serialadd_moore serialadd_moore0(.A(A),.B(B),.Rst(Rst),.clk(clk),.S(S));

always #(`clock_period/2) clk = ~clk; initial begin

clk=0;

A = 8'd35;

B = 8'd99;

Rst = 0;

#(`clock_period)

Rst = 1;

#(`clock_period)

Rst = 0; #(`clock_period*10) $stop; end endmodule

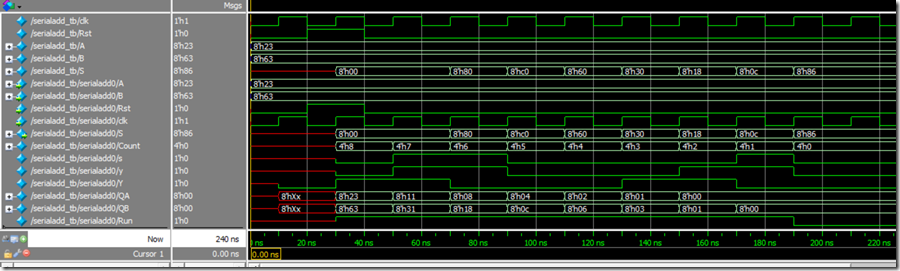

下面是mealy型串行加法的波形,输入35,99,输出134

我们把状态图做如下调整,拆分G为G0,G1,拆分H为H0,H1, 则输出之和状态有关,为moore型串行加法器状态图。

下面是该状态机的状态表:

| 现在状态 | 下一状态(ab) | 输出 | |||

| 00 | 01 | 10 | 11 | s | |

| G0 | G0 | G1 | G1 | H0 | 0 |

| G1 | G0 | G1 | G1 | H0 | 1 |

| H0 | G1 | H0 | H0 | H1 | 0 |

| H1 | G1 | H0 | H0 | H1 | 1 |

| 现在状态 | 下一状态(ab) | 输出 | |||

| 00 | 01 | 10 | 11 | s | |

| y2y1 | Y2Y1 | ||||

| 00 | 00 | 01 | 01 | 10 | 0 |

| 01 | 00 | 01 | 01 | 10 | 1 |

| 10 | 01 | 10 | 10 | 11 | 0 |

| 11 | 01 | 10 | 10 | 11 | 1 |

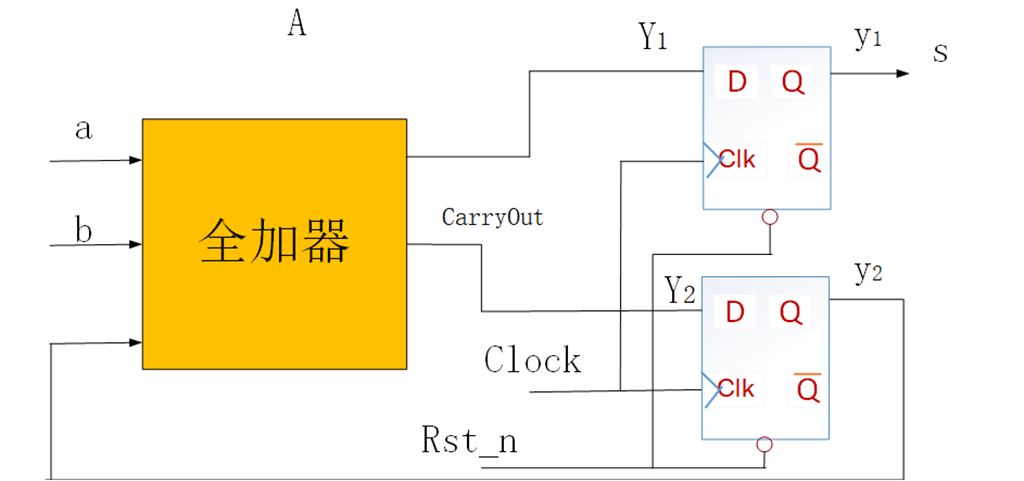

可以推导出

Y1=a^b^y2

Y2=ab+ay2+by2

s=y1

下面是其可能的实现电路。moore型加法输出比mealy型加法多了一个时钟周期的时延。

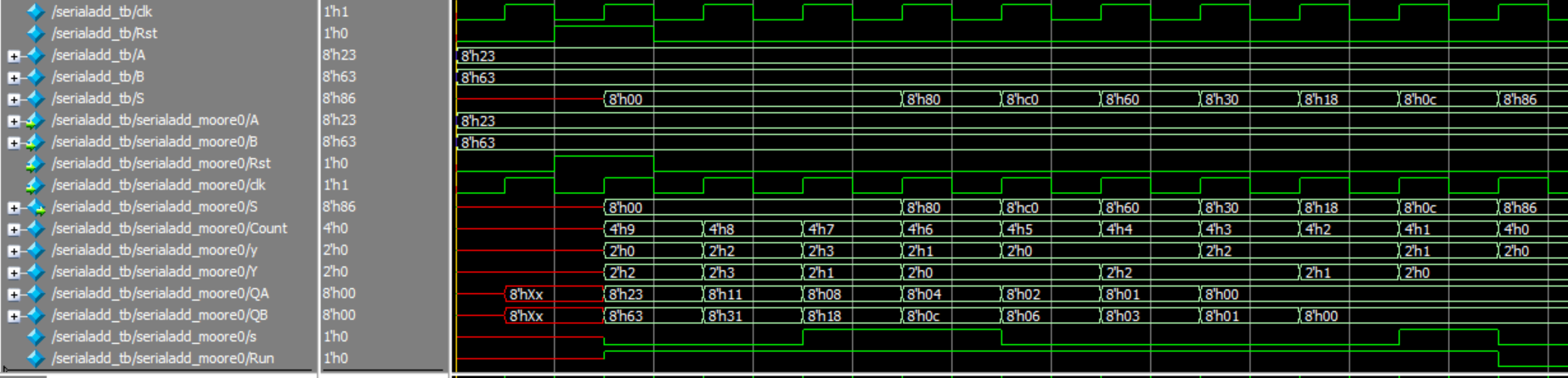

moore型串行加法器verilog代码如下,其中也例化了3个移位寄存器。注意Count复位后为9,

module serialadd_moore(A,B,Rst,clk,S);

input [7:0] A,B;

input Rst,clk;

output wire [7:0] S; reg [3:0] Count;

reg [1:0] y,Y;

wire [7:0] QA,QB;

wire s,Run;

parameter G0=2'b00, G1=2'b01,H0=2'b10, H1=2'b11; shiftrne #(.n(8)) shift_A(.R(A),.L(Rst),.E(1'b1),.w(1'b0),.clk(clk),.Q(QA));

shiftrne #(.n(8)) shift_B(.R(B),.L(Rst),.E(1'b1),.w(1'b0),.clk(clk),.Q(QB));

shiftrne #(.n(8)) shift_S(.R(8'b0),.L(Rst),.E(Run),.w(s),.clk(clk),.Q(S)); //adder FSM

//output and next state cominatioal circuit always @(QA,QB,y) begin case (y)

G0:

begin

if(QA[0]&QB[0]) Y=H0;

else if(~QA[0]&~QB[0]) Y=G0;

else Y=G1; end

G1:

begin

if(~QA[0]&~QB[0]) Y=G0;

else if (QA[0]&QB[0])Y=H0;

else Y=G1; end

H0:

begin

if(QA[0]&QB[0]) Y=H1;

else if(~QA[0]&~QB[0]) Y=G1;

else Y=H0; end

H1:

begin

if(~QA[0]&~QB[0]) Y=G1;

else if (QA[0]&QB[0])Y=H1;

else Y=H0; end

endcase

end //sequential block

always @(posedge clk)

if(Rst)

y<=G0;

else

y<=Y; //control shift proecess

always @(posedge clk)

if(Rst) Count=9;

else if(Run) Count = Count-1; assign Run = |Count;

assign s = (y==H0?1'b0:(y==G0?1'b0:1'b1));

endmodule

`timescale 1ns/1ns

`define clock_period 20 module serialadd_tb;

reg clk;

reg Rst; reg [7:0] A,B;

wire [7:0] S; //serialadd serialadd0(.A(A),.B(B),.Rst(Rst),.clk(clk),.S(S));

serialadd_moore serialadd_moore0(.A(A),.B(B),.Rst(Rst),.clk(clk),.S(S));

always #(`clock_period/2) clk = ~clk; initial begin

clk=0;

A = 8'd35;

B = 8'd99;

Rst = 0;

#(`clock_period)

Rst = 1;

#(`clock_period)

Rst = 0; #(`clock_period*10) $stop; end endmodule

输出波形为:

Verilog 加法器和减法器(8)-串行加法器的更多相关文章

- Verilog 加法器和减法器(4)

类似于行波进位加法器,用串联的方法也能够实现多位二进制数的减法操作. 比如下图是4位二进制减法逻辑电路图. 8位二进制减法的verilog代码如下: module subn(x, y, d,cin) ...

- Verilog 加法器和减法器(7)

在计算机中浮点数 表示通常采用IEEE754规定的格式,具体参考以下文章. https://www.cnblogs.com/mikewolf2002/p/10095995.html 下面我们在Veri ...

- Verilog 加法器和减法器(6)

为了减小行波进位加法器中进位传播延迟的影响,可以尝试在每一级中快速计算进位,如果能在较短时间完成计算,则可以提高加法器性能. 我们可以进行如下的推导: 设 gi=xi&yi, pi = xi ...

- Verilog 加法器和减法器(3)

手工加法运算时候,我们都是从最低位的数字开始,逐位相加,直到最高位.如果第i位产生进位,就把该位作为第i+1位输入.同样的,在逻辑电路中,我们可以把一位全加器串联起来,实现多位加法,比如下面的四位加法 ...

- Verilog 加法器和减法器(2)

类似半加器和全加器,也有半减器和全减器. 半减器只考虑当前两位二进制数相减,输出为差以及是否向高位借位,而全减器还要考虑当前位的低位是否曾有借位.它们的真值表如下: 对半减器,diff = x ^y, ...

- Verilog 加法器和减法器(1)

两个一位的二进制数x,y相加,假设和为s,进位为cout,其真值表为: 从真值表中,我们可以得到:s = x^y, cout = x&y,实现两个一位数相加的逻辑电路称为半加器. 实现该电路的 ...

- Verilog 加法器和减法器(5)

前面二进制加法运算,我们并没有提操作数是有符号数,还是无符号数.其实前面的二进制加法对于有符号数和无符号数都成立.比如前面的8位二进制加法运算,第一张图我们选radix是unsigned,表示无符号加 ...

- 基于Xilinx的Synthesize

所谓综合.就是讲HDL语言.原理图等设计输入翻译成由与.或.非们和RAM.触发器登记本逻辑单元的逻辑连接(即网表).并依据目标和要求(约束条件)优化生成的逻辑连接. ISE-XST XST是Xilin ...

- 乘法器——基于Wallace树的4位乘法器实现

博主最近在学习加法器乘法等等相关知识,在学习乘法器booth编码加Wallace树压缩时,发现在压缩部分积的时候用到了进位保留加法器(Carry Save Adder),博主对这种加法器不是很理解,而 ...

随机推荐

- php中静态方法和静态属性的介绍

静态分为两个部分:静态属性和静态方法 静态的东西都是给类用的(包括类常量),非静态的都是给对象用的 静态属性 在定义属性的时候,使用关键字static修饰的属性称之为静态属性. 静态方法 使用stat ...

- appium自动化测试之元素定位

方法一 使用SDK中附带的uiautomatorviewer来定位 在SDK安装目录下的tools下有个uiautomatorviewer.bat批处理文件点击运行 运行后(注意appium desk ...

- Python3-RabbitMQ 3.7.2学习——环境搭建(一)

学习消息队列,就要把环境先装好,本人使用的是python3.5.2和RabbitMQ 3.7.2,在装RabbitMQ之前,先要装Erlang,一定要. 1.环境:win10系统 python3 ...

- jquery的clone方法应用于textarea和select的bug修复不能copy值,clone id重复的解决

textarea和select的值clone的时候会丢掉,在clone的时候将val再重新赋值一下,如果知道这个了就简单了, 测试发现,textarea和select的jquery的clone方法有问 ...

- .net的架构模式

一:ADO.NET实现三层架构 不用三层的普通的查询写法: string sql = string.Format("select * from Studnet where StuName l ...

- 第一个Struts2实例之hello world!

Struts官网:http://struts.apache.org/ Struts2框架预先实现了一些功能 1:请求数据自动封装 2:文件上传的功能 3:对国际化功能的简化 4 ...

- Mac上c语言连接mysql遇到的问题

参照<Beginning Linux Programming>上的例程写了一个连接mysql的c语言小程序connect1.c.但是按照书上的编译命令无法编译.然后经过查阅资料解决了问题. ...

- JavaScript开发区块链只需200行代码

用JavaScript开发实现一个简单区块链.通过这一开发过程,你将理解区块链技术是什么:区块链就是一个分布式数据库,存储结构是一个不断增长的链表,链表中包含着许多有序的记录. 然而,在通常情况下,当 ...

- ESLint + lint-staged 禁用老项目中的es6

前言 ESLint作为插件化的javascript代码检测工具,为我们的平时的开发保驾护航,好处就不多说了详情查看官网. 问题 有这么一个五年前开发的老项目,机缘巧合到了我们这边来维护. 项目是zep ...

- NIO 中的读和写

概述 读和写是I/O的基本过程.从一个通道中读取很简单:只需创建一个缓冲区,然后让通道将数据读到这个缓冲区中.写入也相当简单:创建一个缓冲区,用数据填充它,然后让通道用这些数据来执行写入操作. 从文件 ...