《FPGA全程进阶---实战演练》第四章之Quartus II使用技巧

技巧1:“新”技能 hierarchies警告寻找

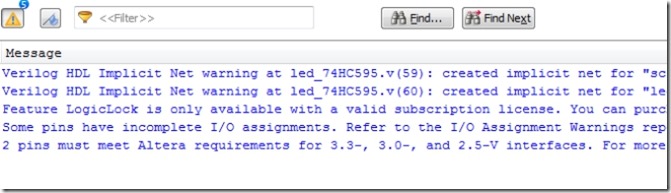

在编译之后,警告中“hierarchies”这个单词大家估计都很熟悉了,一看到这个警告,基本上就是例化时出现的问题。一般例化时,要是哪个连线没引出,没接上,或者是位宽不匹配就会出这个警告。而我们一般就会定位到例化文件,或者是观察RTL视图去寻找,但是工程一大可不是那么好找的啊!

Warning: 1 hierarchies have connectivity warnings - see the Connectivity Checks report folder

解决方法如下:

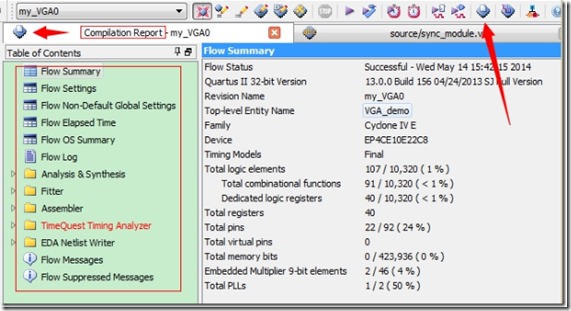

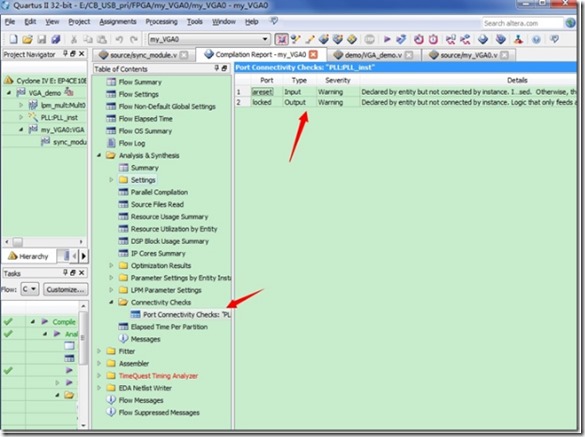

点击图6.1中的图标,然后在Analysis & Synthesis 文件中找到 connectivity checks,如图6.2所示,点击即可查看到说明例化时哪里出现问题。

图6.1 操作(一)

图6.2 操作(二)

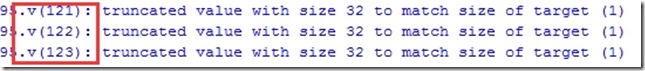

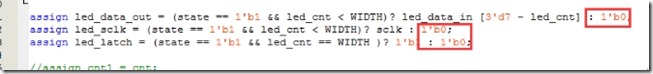

技巧2:位宽不匹配

在很多对reg变量进行赋值时,往往会遇到位宽不匹配的情况,如图6.3所示。其中前面括号中的数字代表在程序中所在的行标,说明赋值是32位宽,被赋值为1位宽,也就是将32位宽进行截断去匹配1位宽。若是在程序中知道确实是赋值reg类型变量是一位一位传送的,可以不用关注此警告,如图6.4所示的程序。可以看到确实需要赋值reg变量中的一位即可。若是想消除此警告,可以利用图6.5所示的修改程序。即将0改成1’b0即可,Quartus中若是对变量不进行赋位数,按32位处理。编译后的结果如图6.6所示。

图6.3 位宽不匹配

图6.4 源程序

图6.5修改后的程序

图6.6编译后的结果

技巧3:tcl文件的利用

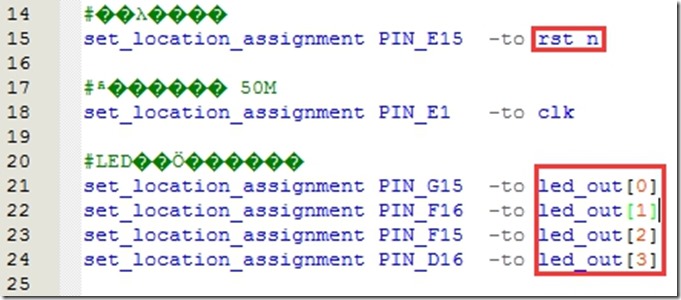

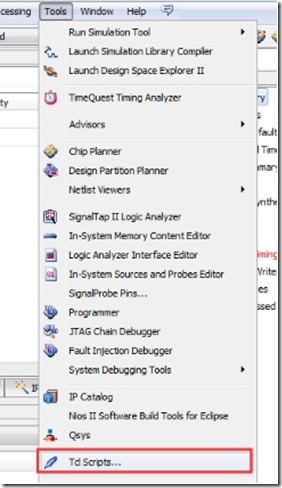

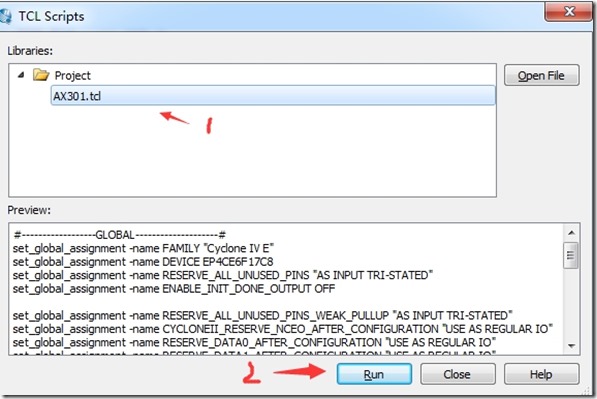

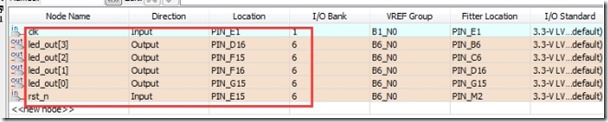

在引脚分配时,往往对于一个浩大的工程来说,引脚数量是很多的,若是一个一个去分配,费时费力,劳民劳财,其实可以利用tcl文件,只需更改几个信号说明就可以。如图6.7所示,图中标注的更改成模块中所用的信号名字即可。图6.8是quartus ii中的操作步骤,点击Tcl scripts,再点击图6.9中所出现的位置,即可。图6.10是pin planner中分配情况。

图6.7 tcl文件

图6.8 quartus ii中的操作(一)

图6.9 quartus ii中的操作(二)

图6.10 pin planner分配情况

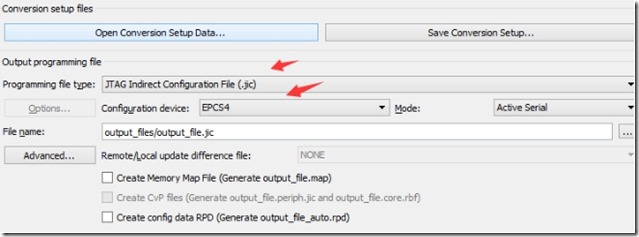

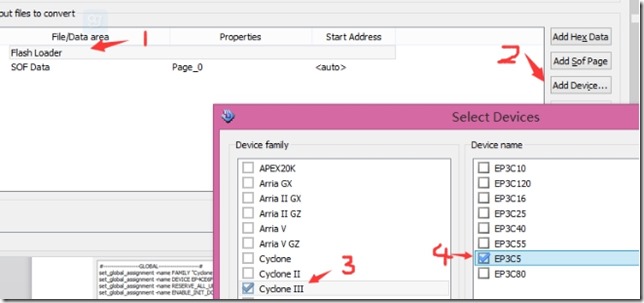

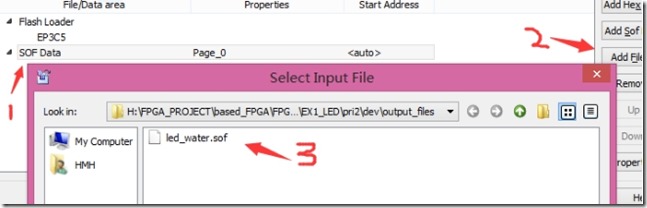

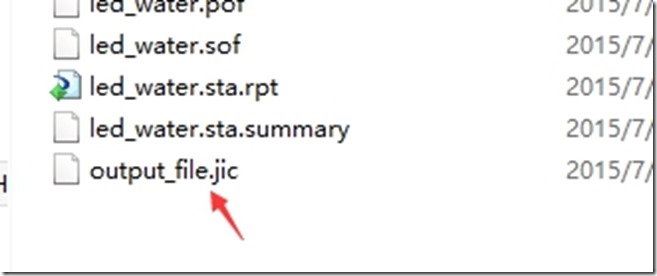

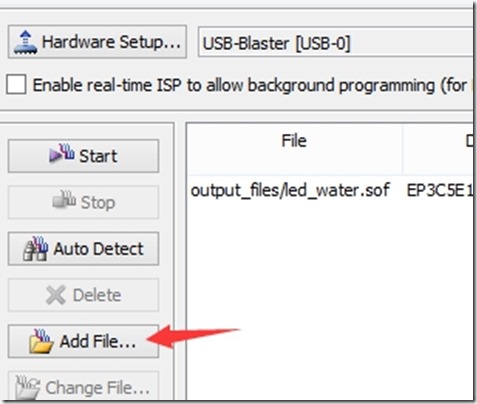

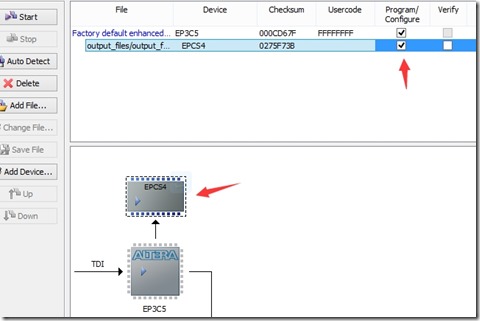

技巧4:jic固化文件的生成

点击file ---- convert programming file,出现如图6.11所示的界面。在programming file type中选择.jic,在configuration device中选择 EPCS4(这个根据你使用板卡的配置芯片选择,笔者设计的是EPCS4),然后在选择图6.12中的flash loader,点击device,然后选择器件类型,笔者设计的是EP3C5芯片。在选择 sof data,将sof文件加载过来,点击 generate出现生成成功界面。然后打开工程目录下中的output files就可以看到所生成的jic文件,如图6.14所示。然后再进入到编程下载界面,如图6.15所示,点击add file,将刚才生成的jic文件加载过来,如图6.16所示,将原sof文件删掉,并选择 program/configure,点击start即可,然后重新上电观察效果。

图6.11 配置界面(一)

图6.12 配置界面(二)

图6.13 配置界面(三)

图6.14 生成的jic文件

图6.15 下载界面

图6.16 添加jic文件

《FPGA全程进阶---实战演练》第四章之Quartus II使用技巧的更多相关文章

- 《FPGA全程进阶---实战演练》第二章之焊接板子及调试注意事项

1.若是读者第一次做板子,强烈建议画完PCB板后将PCB图打印出来,然后对照你买的芯片将芯片放置对 应的位置,然后查看所有的封装格式适不适合,否则等你做出板子来后再试,为时晚矣.笔者虽然知道要这么 做 ...

- 《FPGA全程进阶----实战演练》第二章之系统搭建

1 系统方案 对于设计一款硬件平台,首先要确定整体框架,确定各个模块所需要的芯片以及电压分配情况.图2.6是笔者曾经设计的硬件平台系统. 图2.6系统框图 对于选定一个系统方案之后,接下来做的要先去查 ...

- 《FPGA全程进阶---实战演练》第一章之FPGA介绍

1 什么是FPGA FPGA也即是Field Programmable Gate Array的缩写,翻译成中文就是现场可编程门阵列.FPGA是在PAL.GAL.CPLD等可编程器件的基础上发展起来的新 ...

- 《FPGA全程进阶---实战演练》第九章 计数器要注意

本小节我们来做一个好玩的事情,就是计数器,还记得在做LED自加实验时我们就曾经提到过关于计数器的相关议题,那么这节我们就来讨论讨论. 探讨一下如下的问题:请用verilog记八个数的写法,分析这个可以 ...

- 《FPGA全程进阶---实战演练》第一章之如何学习FPGA

对于很多初学者,大部分都是急于求成,熟不知越是急于求成,最终越是学无所成,到头来两手空空,要学好FPGA,必须弄懂FPGA本质的一些内容. 1.FPGA内部结构及基本原理 FPGA是可以编程的,必须通 ...

- 《FPGA全程进阶---实战演练》第二章之硬件平台的搭建

学习FPGA,多多少少应该要懂得硬件电路的设计,这样不单单增加了自己的技能,而且还能够对FPGA的硬件实现有更好的了解. 1 模块划分 对于一个基本的FPGA硬件平台,常用的几个电路部分:(1)电源电 ...

- 《FPGA全程进阶---实战演练》第二章之PCB layout注意事项以及投板几点说明

上一篇博客讲述了各个部分的原理图,那么根据原理图画出PCB,其实PCB是一门很大的学问,想要掌握谈何容易.就笔者在画PCB时的一些注意事项做一些说明. 1.电源部分的电源线 ...

- 《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新<FPGA全程进阶---实战演练&g ...

- 《FPGA全程进阶---实战演练》第四章之实验平台软硬件使用简介

本章主要是讲解读者在进行FPGA逻辑设计之前的准备工作,需要下载Quartus II软件和 Modelsim 软件,一个是用来进行FPGA逻辑设计,一个是用来对逻辑进行理论分析与验证. 1.1 qua ...

随机推荐

- linux系统调用sysconf

1.前言 当前计算机都是多核的,linux2.6提供了进程绑定cpu功能,将进程指定到某个core上执行,方便管理进程.linux提供了sysconf系统调用可以获取系统的cpu个数和可用的cpu个数 ...

- 三十道linux内核面试题

1. Linux中主要有哪几种内核锁? Linux的同步机制从2.0到2.6以来不断发展完善.从最初的原子操作,到后来的信号量,从大内核锁到今天的自旋锁.这些同步机制的发展伴随Linux从单处理器 ...

- Snail—OC学习之类别Category

类别就是向类加入一些实用的功能或者方法 利于开发 类能够是系统类.能够是自己定义类 类别跟子类是不一样的.类别仅仅能加入一些方法 属性变量什么的不能够加入 不创建新类,就可以对已有类进行扩展 做项目的 ...

- mysql-5.7.20 版本的 mysql-group-replication 可用性测试报告

一.喜迎 mysql-5.7.20 事实上mysql-group-replication 功能是在mysql-5.7.17这个版本上引入的,它实现了mysql各个结点间数据强一致性, 这个也成为了我 ...

- unity5, custom PBS shader

unity5中引入了基于物理着色(PBS)的Standard shader.由于这种着色器通过调节参数和贴图可逼真模拟各种硬质表面,所以不必再像unity4时代那样需要对各种质感材质单独编写着色器,而 ...

- PHP笔试题

1.不用新变量直接交换现有两个变量的值 (1)list($a,$b)=array($b,$a); (2)a=a+b,b=a-b,a=a-b 2.PHP数字金额转大小格式,同时说明思路 function ...

- U3D-LookAt插值动画

var qua = Quaternion.FromToRotation(Vector3.forward, target.transform.position - transform.position) ...

- Error LNK2019:Unresolved External Symbol 的解决方案

当头文件中声明了一个函数,但是在相应的源文件中却没有对该函数进行定义,则会出现为“解决的外部符号”(unresolved external symbol )错误.另外,当一个函数调用了外部的一个库文件 ...

- 【Linux】VMware中为CentOS设置静态IP(非动态获取IP)

在VMware上安装好Linux后,默认设置的动态IP,每次启动的IP都不同,远程连接挺费劲的. 于是,需要设置静态的IP,至少我从远程工具连接上去方便多了.另外,为了安装一些软件,也需要访问互联网. ...

- lua连续随机数

号外:惭愧,工作后几乎没有写博客了,其实是有时间的(每周单休),只是厌烦对着屏幕了,还有懒. 现在老板换人了,时间会多点,估计正常就每周双休了,决定还是每周写两篇(不一定是love2d), 写不出就翻 ...