FPGA开发流程(创建工程,选择芯片,变量位置,文件命名,reg和wire数据类型,开发流程)

- 开发流程(以二选一选择器为例)

1.设计定义:设计一个可以从两个输入端中选择其中一个并输出的逻辑电路

2.设计输入

2.1.逻辑抽象:三个输入端,一个用来选择,记sel,另两个被选择,记a,b,加上一个输出端y。

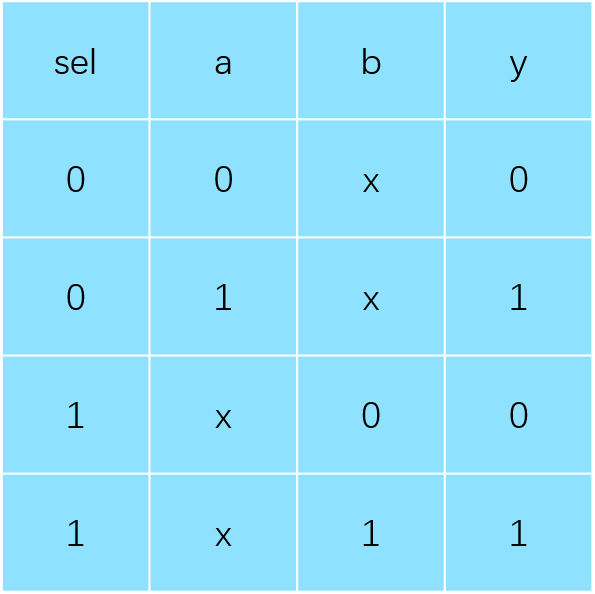

2.2.画真值表

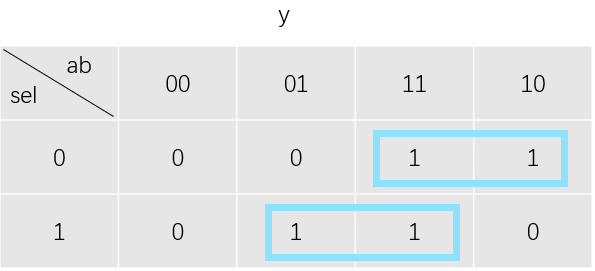

2.3卡诺图化简

2.4 逻辑表达式

y=(~sel)*a+sel*a

或者y=if(sel==1)?a:b

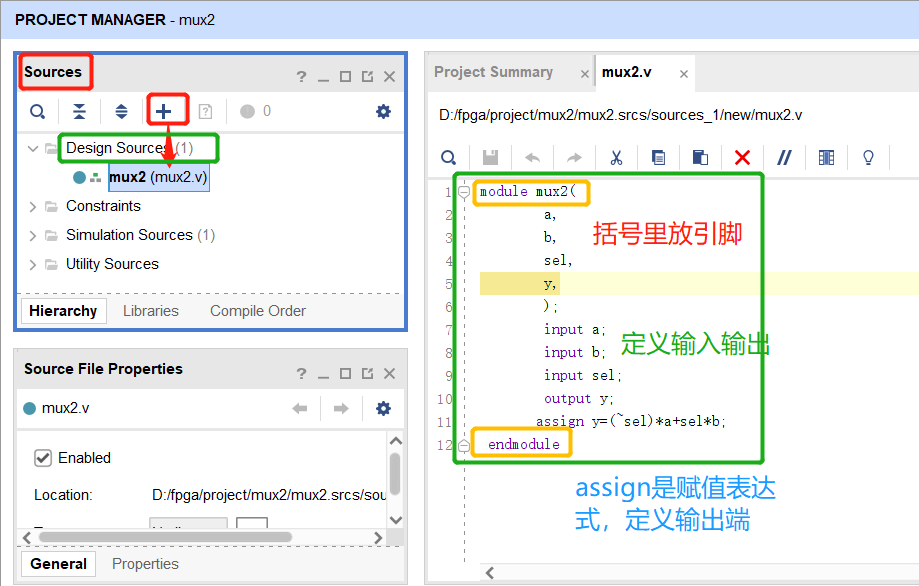

2.5在Vivado创建design sources 源文件并写入代码

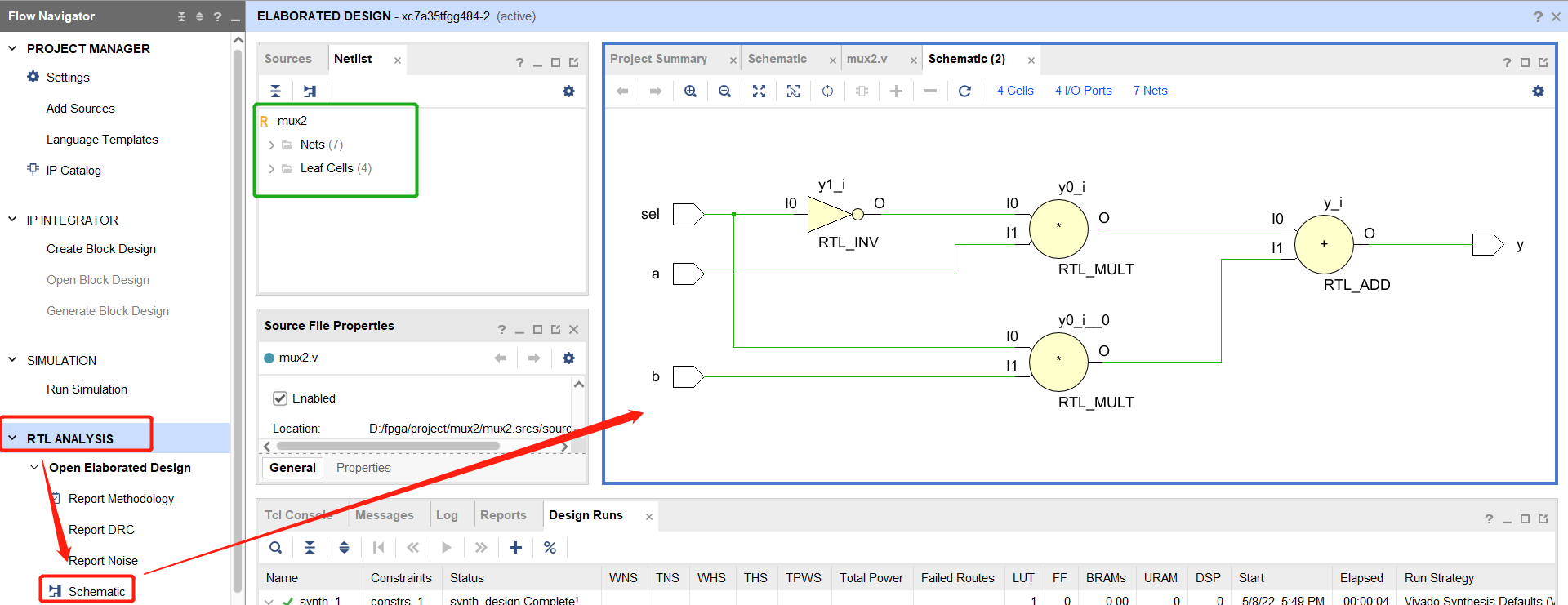

保存,然后在RTL analysis中查看用逻辑符号表示的示意图

设计输入完毕!

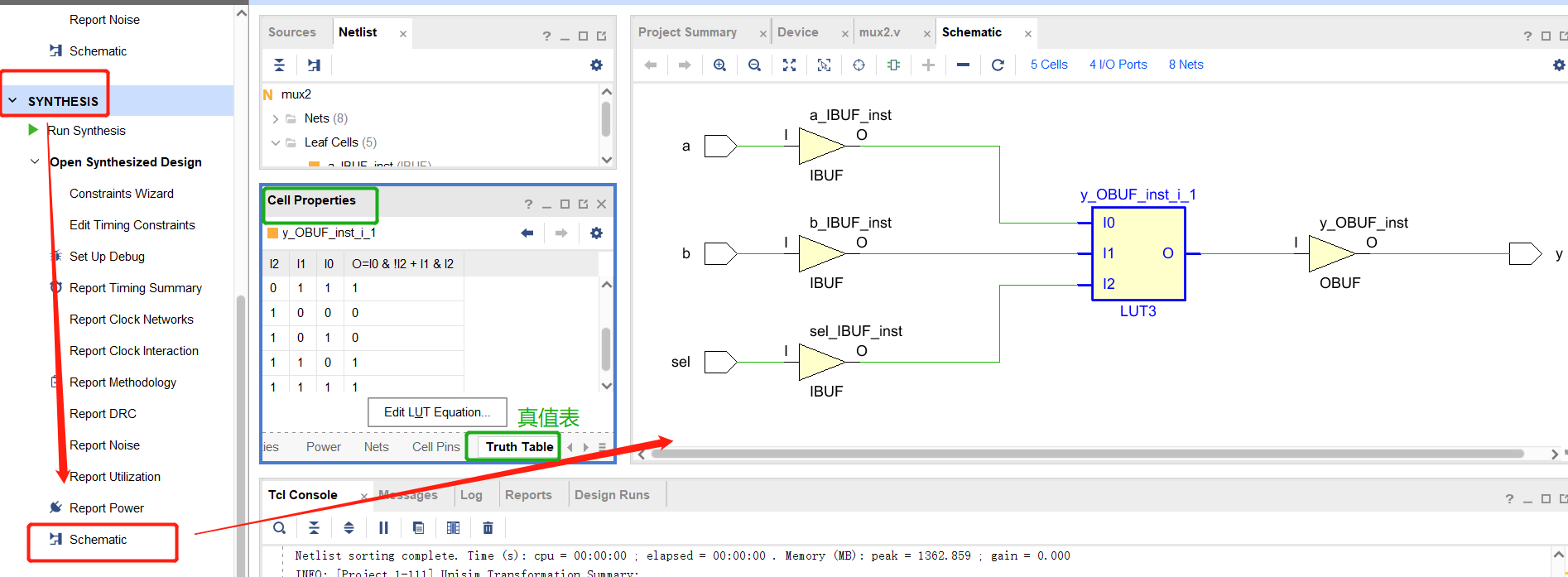

3.综合(synthsize)

3.1 run synthesis

3.2查看用fpga底层器件画的综合后的示意图

综合完毕!把逻辑符号等较低层较细化的零件综合成输出,输出。

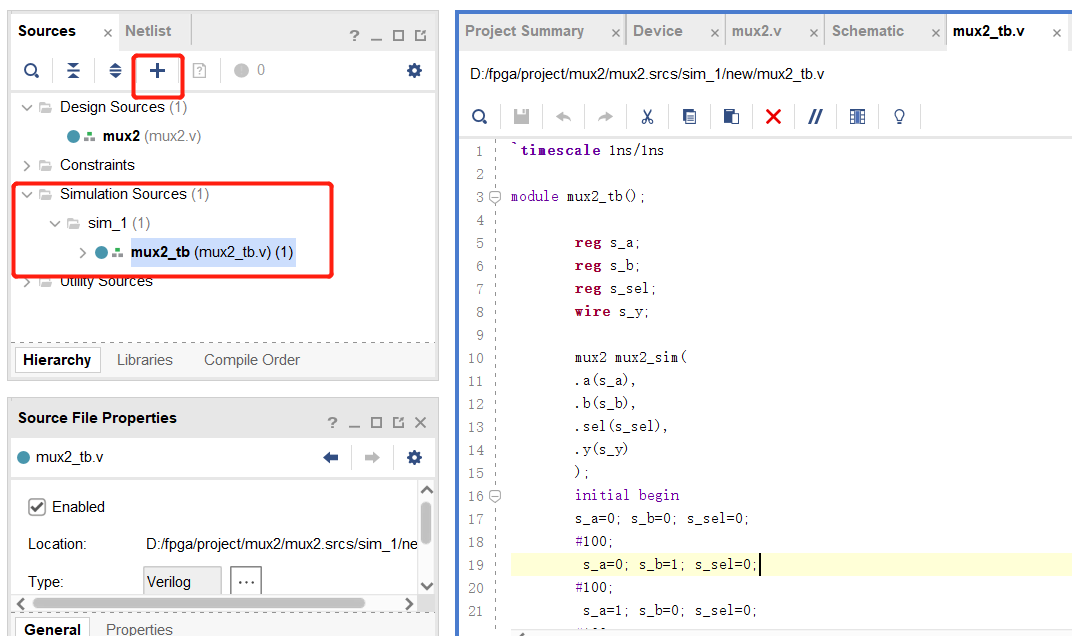

4.功能仿真验证(function simulation)

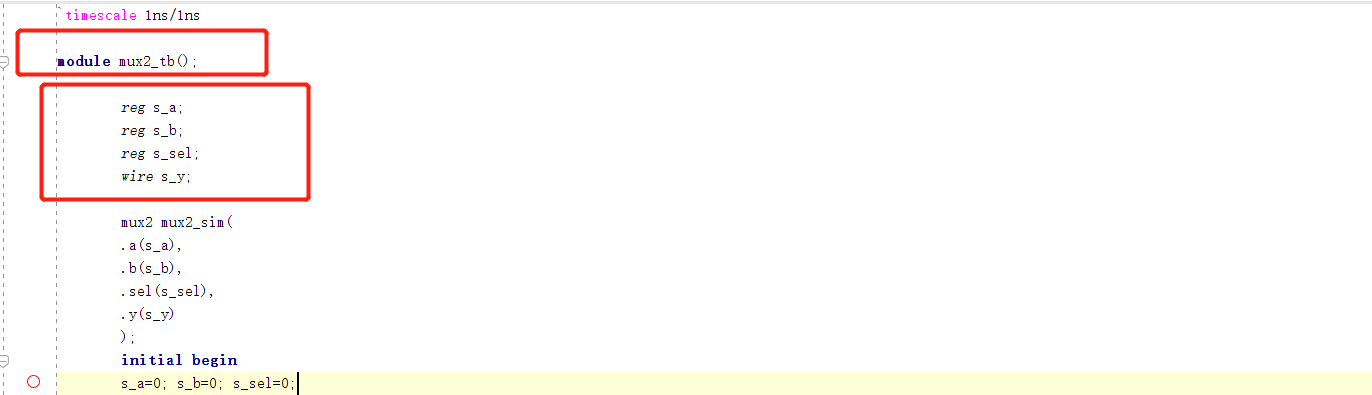

4.1创建一个simulational sources源文件并写入代码,保存。create simulation sources

1 `timescale 1ns/1ns //标点不能丢(注意是1左边的点,不是引号键), 单位/精度

2

3 module mux2_tb();

4

//定义变量的数据类型,必须放在module里面,reg和wire的区别在后面

5 reg s_a;

6 reg s_b;

7 reg s_sel;

8 wire s_y;

9 // 模型 新名字 (给引脚起新名字,...用来仿真验证)

10 mux2 mux2_sim(

11 .a(s_a), //a是端口,s_a是驱动,下面同理

12 .b(s_b),

13 .sel(s_sel),

14 .y(s_y)

15 );

//初始化,给输入端赋值,依次变化,时许仿真,注意#加数字表示停顿多久,单位在第一行就定义了

16 initial begin

17 s_a=0; s_b=0; s_sel=0;

18 #100;

19 s_a=0; s_b=1; s_sel=0;

20 #100;

21 s_a=1; s_b=0; s_sel=0;

22 #100;

23 s_a=1; s_b=1; s_sel=0;

24 #100;

25 s_a=0; s_b=0; s_sel=1;

26 #100;

27 s_a=0; s_b=1; s_sel=1;

28 #100;

29 s_a=1; s_b=0; s_sel=1;

30 #100;

31 s_a=1; s_b=1; s_sel=1;

32 #100;

33 $stop;//停止仿真

34 end

35 endmodule

36

4.2 run behavioral simulation或者run post-synthsis functional simulation 功能仿真,不考虑延时

run post-synthsis timing simulation 综合后时许仿真 会考虑延迟。

获得时序图,检验功能的正确性。

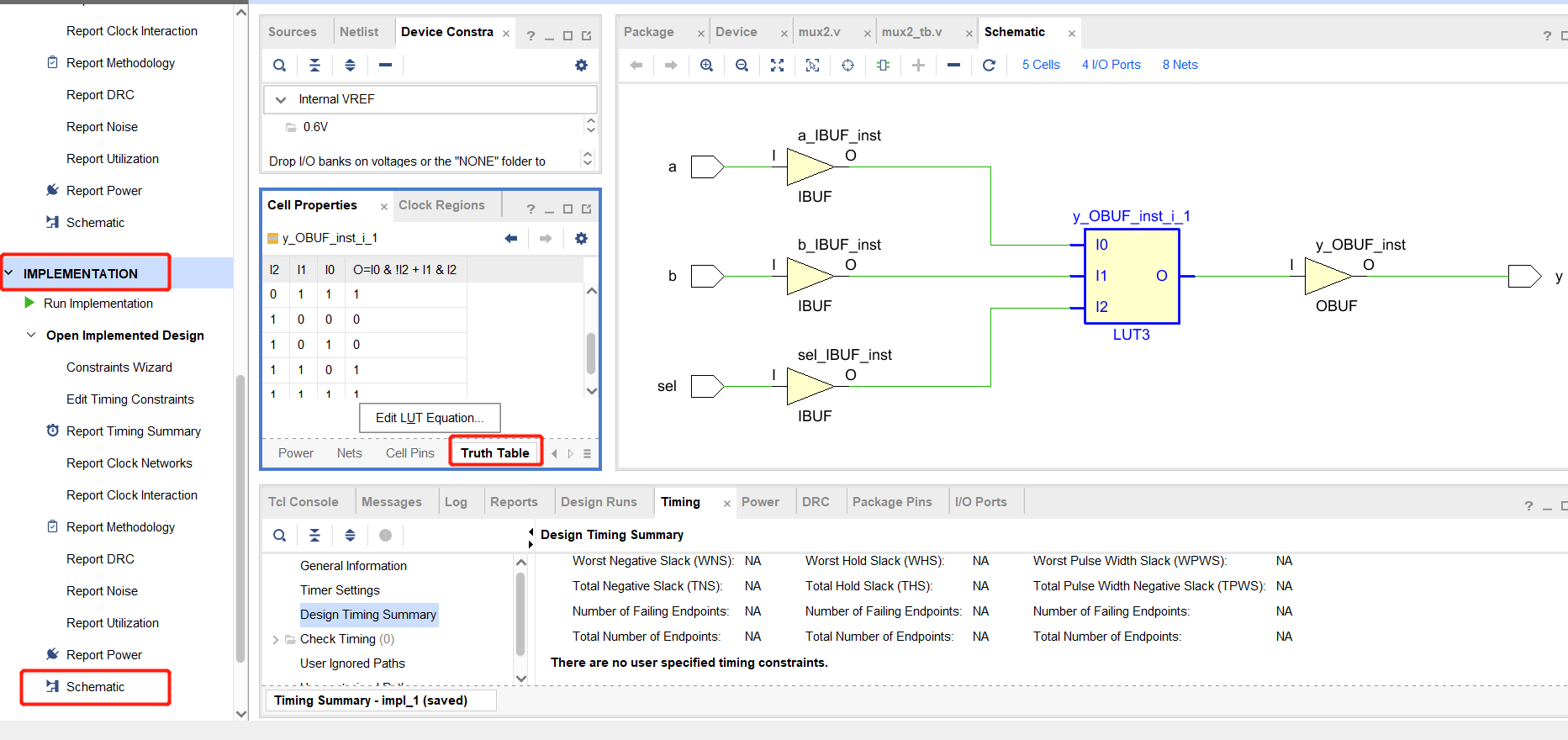

5.布局布线

5.1 run implementation

5.2 查看布局布线后的示意图

6.性能分析

6.1run post-implementation functional simulation 功能仿真 无延时

run post-implementation timing simulation 时序仿真,有延时,可能可以看到毛刺(竞争冒险)

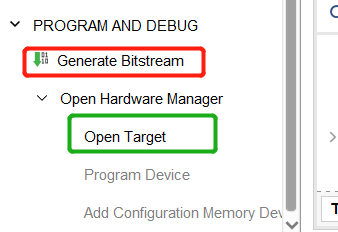

7.板级调试

7.1I/O planing 设置I/O口 其中,I/O STD是电平标准,根据开发板的接口电平来设定。package pin是管脚位置,把逻辑输入和开发板的实际引脚对应上。

7.2 生成数据流,传输到开发板

program device 下载到开发板,即可使用,验证等。

还没买板子,暂时没法尝试。到时候记得给电脑装驱动,看教程即可。

流程结束

注意事项

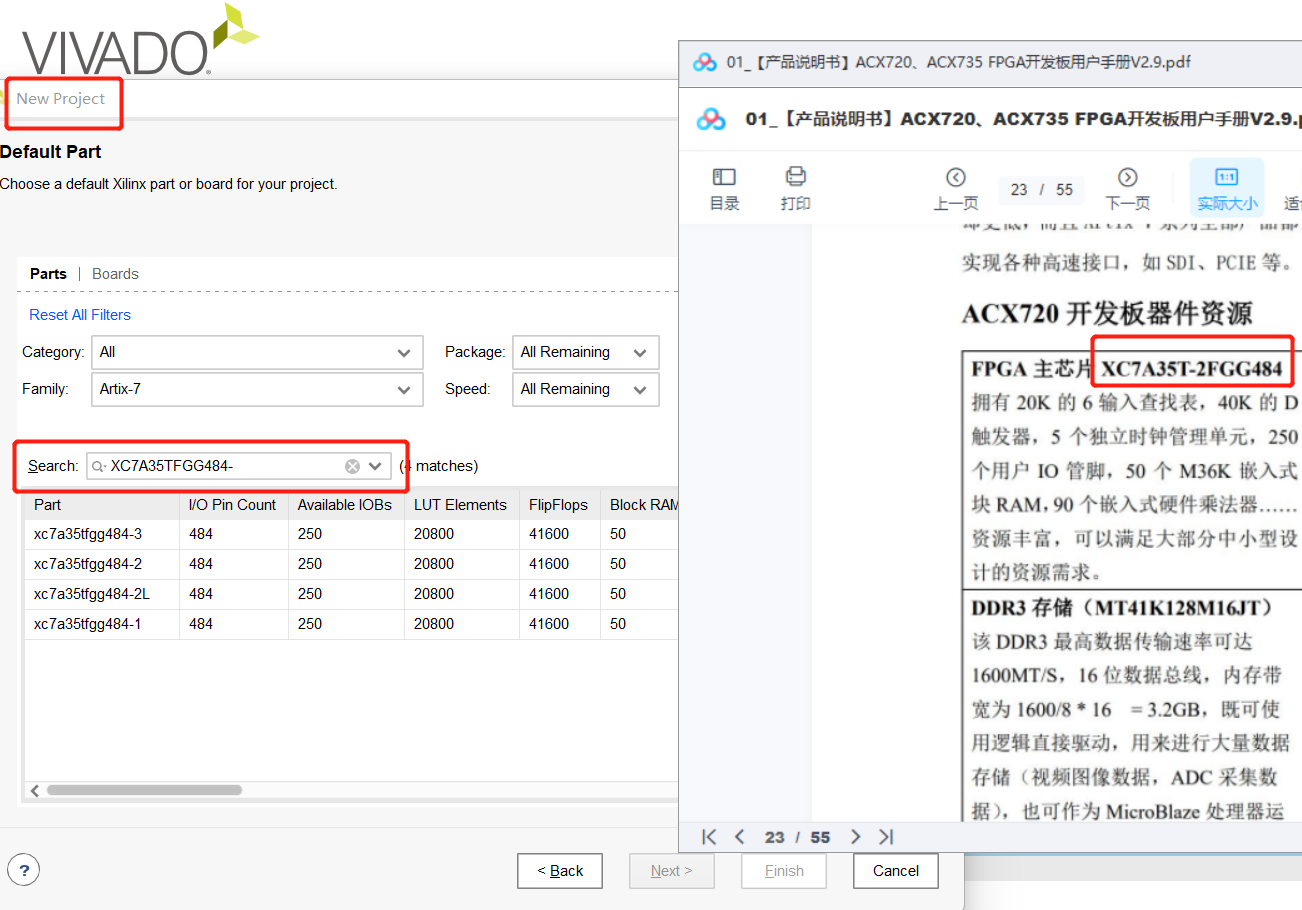

- 创建工程

注意芯片型号中-2是速度等级,要放在最后,直接输入右边红框的内容是找不到的。

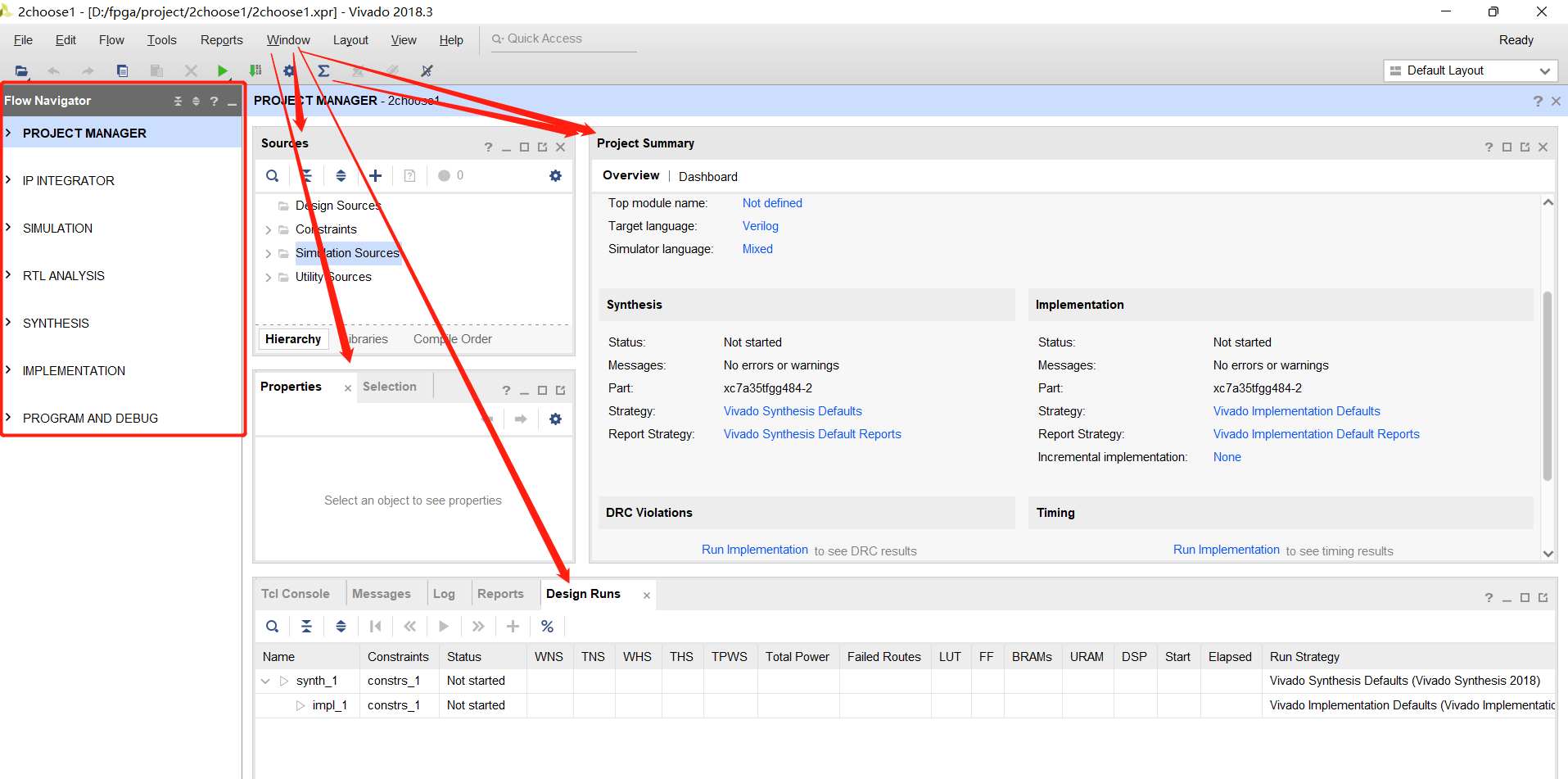

- 注意窗口的名字,有用。

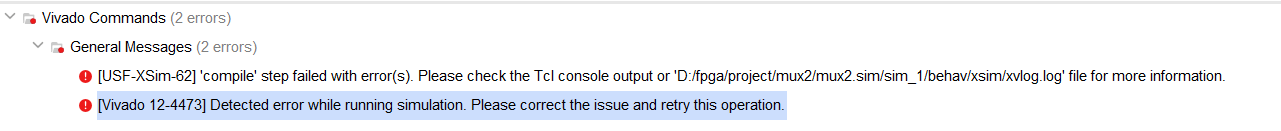

- 命名最好以英文字母开头,以数字开头会出现如下的错误:

关联notepad之后使用它来写程序有个缺点就是不会在编辑页面提示具体的语法错误。

- 变量的定义要放在module里面,否则会出现以下编译错误。

- reg和wire数据类型的区别

wire,就是相当于一条连线,用来连接电路,不能存储数据,无驱动能力,是组合逻辑,只能在assign左侧赋值,不能在always @ 中赋值;

但reg可以综合成register,latch,甚至wire(当其只是中间变量的时候),可以用于组合逻辑或者时序逻辑,能存储数据,有驱动能力,在always @模块表达式左侧被赋值。

两个共同具有性质:都能用于assign与always @模块表达式的右侧。

wire型数据常用来表示以assign关键字指定的组合逻辑信号。模块的输入输出端口类型都默认为wire型。默认初始值是z,高阻态。

reg型表示的寄存器类型。always模块内被赋值的信号,必须定义为reg型,代表触发器。默认初始值是x,不定态。reg相当于存储单元,wire相当于物理连线。

verilog 中变量的物理数据分为线型和寄存器型。这两种类型的变量在定义时要设置位宽,缺省为1位。变量的每一位可以是0,1,X,Z。其中x代表一个未被预置初始状态的变量或者是由于由两个或多个驱动装置试图将之设定为不同的值而引起的冲突型线型变量。z代表高阻状态或浮空量。

线型数据包括wire,wand,wor等几种类型在被一个以上激励源驱动时,不同的线型数据有各自决定其最终值的分辨办法。

两者的区别是:寄存器型数据保持最后一次的赋值,而线型数据需要持续的驱动

输入端口可以由net/reg驱动,但输入端口只能是net,如a = b & c,输入端口a 只能是net型,但其驱动b,c可以是net/reg型;输出端口可以使net/reg类型,输出端口只能驱动net,如a = b & c,模块的输出端口b,c可以是net/reg型,但它们驱动的a必须是net型;若输出端口在过程块(always/initial)中赋值则为reg型,若在过程块外赋值则为net型。用关键词inout声明一个双向端口, inout端口不能声明为寄存器类型,只能是net类型。

wire表示直通,即只要输入有变化,输出马上无条件地反映;reg表示一定要有触发,输出才会反映输入。组合与时序的区别。

2022-05-08 21:30:07

FPGA开发流程(创建工程,选择芯片,变量位置,文件命名,reg和wire数据类型,开发流程)的更多相关文章

- (android 地图实战开发)2 创建MapActivity,根据设备当前位置,显示地图

(android 地图实战开发)2 创建MapActivity,根据设备当前位置,显示地图 http://www.cnblogs.com/macroxu-1982/archive/2011/09/13 ...

- XMPP之ios即时通讯客户端开发-创建工程添加XMPPFramework及其他框架(三)

XMPPFramework GitHub: https://github.com/robbiehanson/XMPPFramework 获取源代码 git clone https://github.c ...

- 【C语言探索之旅】 第二部分第六课:创建你自己的变量类型

内容简介 1.课程大纲 2.第二部分第六课: 创建你自己的变量类型 3.第二部分第七课预告: 文件读写 课程大纲 我们的课程分为四大部分,每一个部分结束后都会有练习题,并会公布答案.还会带大家用C ...

- Android项目开发全程(一)--创建工程

每个程序员都知道,项目工程的整体架构对开发有着决定性的影响,在后续的开发工作中,能不能有效的减少代码的重复量和有效的人员分工取决于前期工程整体的架构.刚参加工作还不到一个月就意识到之前做的项目在架构方 ...

- 【转载】salesforce 零基础开发入门学习(二)变量基础知识,集合,表达式,流程控制语句

salesforce 零基础开发入门学习(二)变量基础知识,集合,表达式,流程控制语句 salesforce如果简单的说可以大概分成两个部分:Apex,VisualForce Page. 其中Apex ...

- xilinx Vivado的使用详细介绍(2):创建工程、添加文件、综合、实现、管脚约束、产生比特流文件、烧写程序、硬件验证

xilinx Vivado的使用详细介绍(2):创建工程.添加文件.综合.实现.管脚约束.产生比特流文件.烧写程序.硬件验证 Author:zhangxianhe 新建工程 打开Vivado软件,直接 ...

- Xilinx Vivado的使用详细介绍(1):创建工程、编写代码、行为仿真

Xilinx Vivado的使用详细介绍(1):创建工程.编写代码.行为仿真 Author:zhangxianhe 新建工程 打开Vivado软件,直接在欢迎界面点击Create New Projec ...

- 【Android开发】创建你的第一个Android项目

原文:http://android.eoe.cn/topic/summary 本文中你将了解到: 1. 使用Eclipse创建项目 2. 使用命令行创建项目 你还应该阅读: 1. 安装SDK(官网页面 ...

- 如何搭建SBT编译Scala开发的Android工程

作者:戚明峰 最近接触了shadowsocks的Android客户端项目源码(https://github.com/shadowsocks/shadowsocks-android),刚好这个项目是使用 ...

随机推荐

- 使用FastJson导出JSON

概述 fastjson是目前java语言中最快的json库,比自称最快的jackson速度要快,比gson快大约6倍. https://github.com/alibaba/fastjson Fast ...

- 《计算机组成原理/CSAPP》网课总结(一)

现在是2022年4月17日晚10点,本月计划的网课<csapp讲解>视频课看到了第八章"异常"第三讲,视频讲的很好但更新很慢,暂时没有最新的讲解,所以先做一个简单总结. ...

- Linux启动故障排查和修复技巧

一个执着于技术的公众号 我发现Linux系统在启动过程中会出现一些故障,导致系统无法正常启动,我在这里写了几个应对单用户模式.GRUB命令操作.Linux救援模式的故障修复案例帮助大家了解此类问题的解 ...

- 掌握AI学习路上核心理论知识,你绝对不能错过这份最全资料包

人工智能成为当下科技发展的代表之一,持续受到了不少追捧,不管你是否是这一专业的学生或者职场人,学习并掌握一项新潮技能总是不会被同龄人淘汰的.我曾经问过别人.也被别人问过关于学习人工智能(AI)最好的方 ...

- 手脱无名壳tslgame_rl

1.使用Detect It Easy查壳,该壳未显示出壳信息,至于为何有壳,我们使用IDA打开,查看其的导入表,其中没有太多函数使用: 2.我们使用x32dbg打开,运行至入口点,此处没有pushad ...

- JavaScript 任务池

JavaScript 任务池 本文写于 2022 年 5 月 13 日 线程池 在多线程语言中,我们通常不会随意的在需要启动线程的时候去启动,而是会选择创建一个线程池. 所谓线程池,本意其实就是(不止 ...

- 从 rails 窥探 web 全栈开发(零)

从 rails 窥探 web 全栈开发(零) 本文将讲述在学习之前几个必须要知道的概念,这些词汇在 rails 中都会出现. 本文前置条件:安装好 Ruby. 从 rails 窥探 web 全栈开发( ...

- API 工程化分享

概要 本文是学习B站毛剑老师的<API 工程化分享>的学习笔记,分享了 gRPC 中的 Proto 管理方式,Proto 分仓源码方式,Proto 独立同步方式,Proto git sub ...

- for循环+数字类型补充

一.for循环 1.循环取值 1.1列表类型: 定义l=['a','b','c'],要提取列表中的值 如果采用while循环的话: print(len(l)) i=0 while i& ...

- 词云图value传递数据不显示(已解决)

问题描述: 今天在做词云图时,虽然词云图能够展现出来,但是后台传递过来的数据(每个词出现的次数)却不显示. 错误原因: 错误的将tooltip写在了series内部,如图: 解决方案: 将toolti ...