数电第11周周结_by_yc

Lab7_时序逻辑验证

一、简易电子时钟

功能描述:

设计一简易电子时钟,支持时、分、秒显示,其中HEX7-HEX6显示时,HEX5-HEX4显示分,HEX1-HEX0显示秒,假设进制为:18秒=1分钟;13分钟=1小时;9小时=1天。设计方案:

首先,设计三个寄存器分别用来存储当前时、分、秒的计时结果,并将秒级作为最低级,进行嵌套循环:

①每逢时钟上升沿,秒加一,并对其进行判断,若符合进位条件,则该位置零,同时上一位加一;若上一位同时也符合进位条件,则继续向上一位进位。

②时钟上升沿出现的时间间隔为1s,则对应时钟频率为1Hz,初始时钟采用开发板自带的50MHz振荡器,对该信号进行分频,其中M=50M关键代码:

module elec_clk(input clk,output reg [7:0] second=8'b00000000,output reg [7:0] minute=8'b00000000,output reg [7:0] hour=8'b00000000);always@(posedge clk) beginsecond <= second + 8'b00000001;if(second == 8'b00010001) begin //second:18second <= 8'b00000000;minute <= minute + 8'b00000001;if(minute == 8'b00001100) begin //minute:13minute <= 8'b00000000;hour <= hour + 8'b00000001;if(hour == 8'b00001000) //hour:9hour <= 8'b00000000;endendendendmodulemodule fpga_clk(input CLOCK_50,output [6:0] HEX0,output [6:0] HEX1,output [6:0] HEX4,output [6:0] HEX5,output [6:0] HEX6,output [6:0] HEX7);wire clock;wire [7:0] second_bin;wire [7:0] second_bcd;wire [7:0] minute_bin;wire [7:0] minute_bcd;wire [7:0] hour_bin;wire [7:0] hour_bcd;clk_div U0(.clk(CLOCK_50),.rstn(1),.clk_out(clock));elec_clk U1(.clk(clock),.second(second_bin),.minute(minute_bin),.hour(hour_bin));bin2bcd U3(.bin_code(second_bin),.bcd_code(second_bcd));bin2bcd U4(.bin_code(minute_bin),.bcd_code(minute_bcd));bin2bcd U5(.bin_code(hour_bin),.bcd_code(hour_bcd));led_display H0(.ctrl(0),.data(hour_bcd[3:0]),.dev0(HEX6));led_display H1(.ctrl(0),.data(hour_bcd[7:4]),.dev0(HEX7));led_display M0(.ctrl(0),.data(minute_bcd[3:0]),.dev0(HEX4));led_display M1(.ctrl(0),.data(minute_bcd[7:4]),.dev0(HEX5));led_display S0(.ctrl(0),.data(second_bcd[3:0]),.dev0(HEX0));led_display S1(.ctrl(0),.data(second_bcd[7:4]),.dev0(HEX1));endmodule

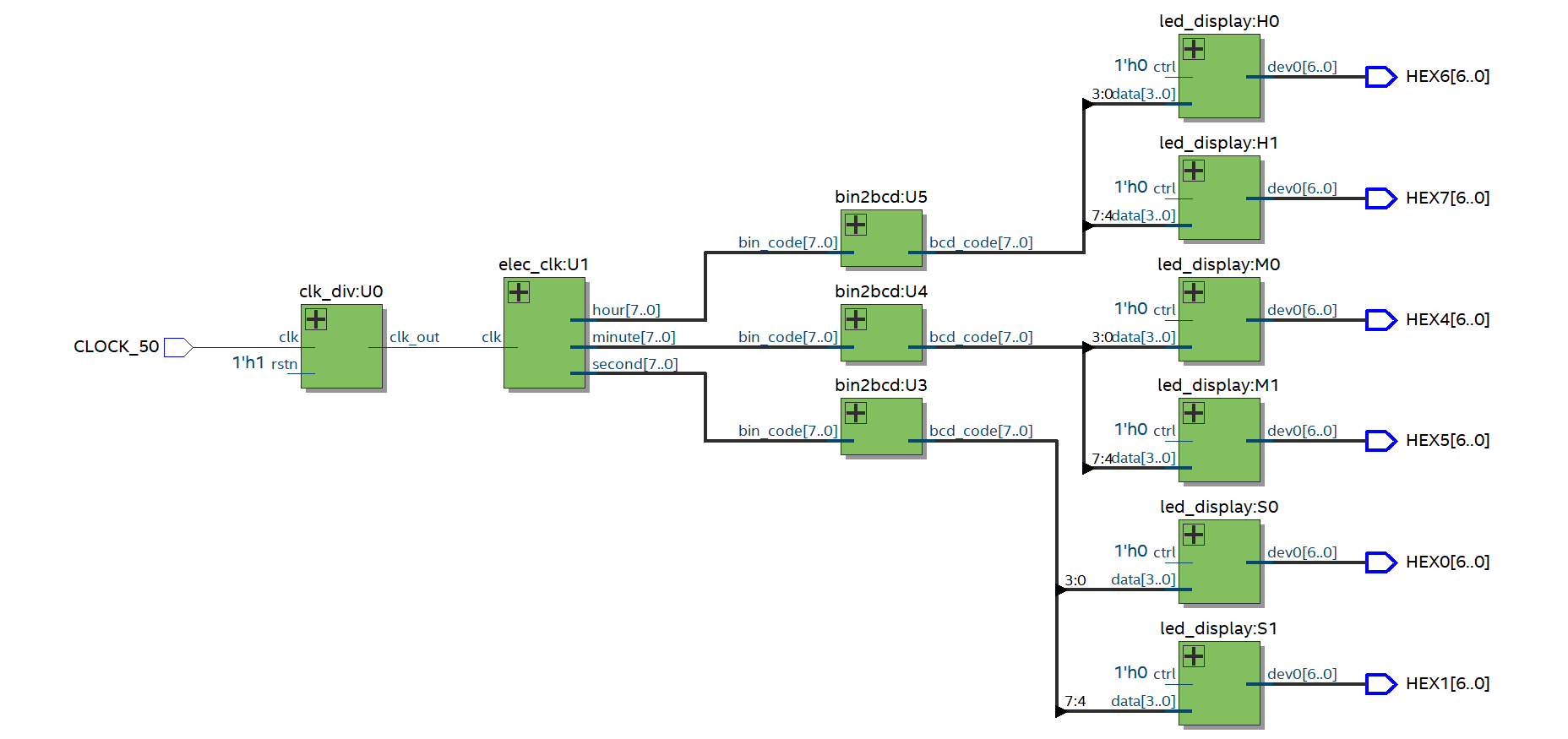

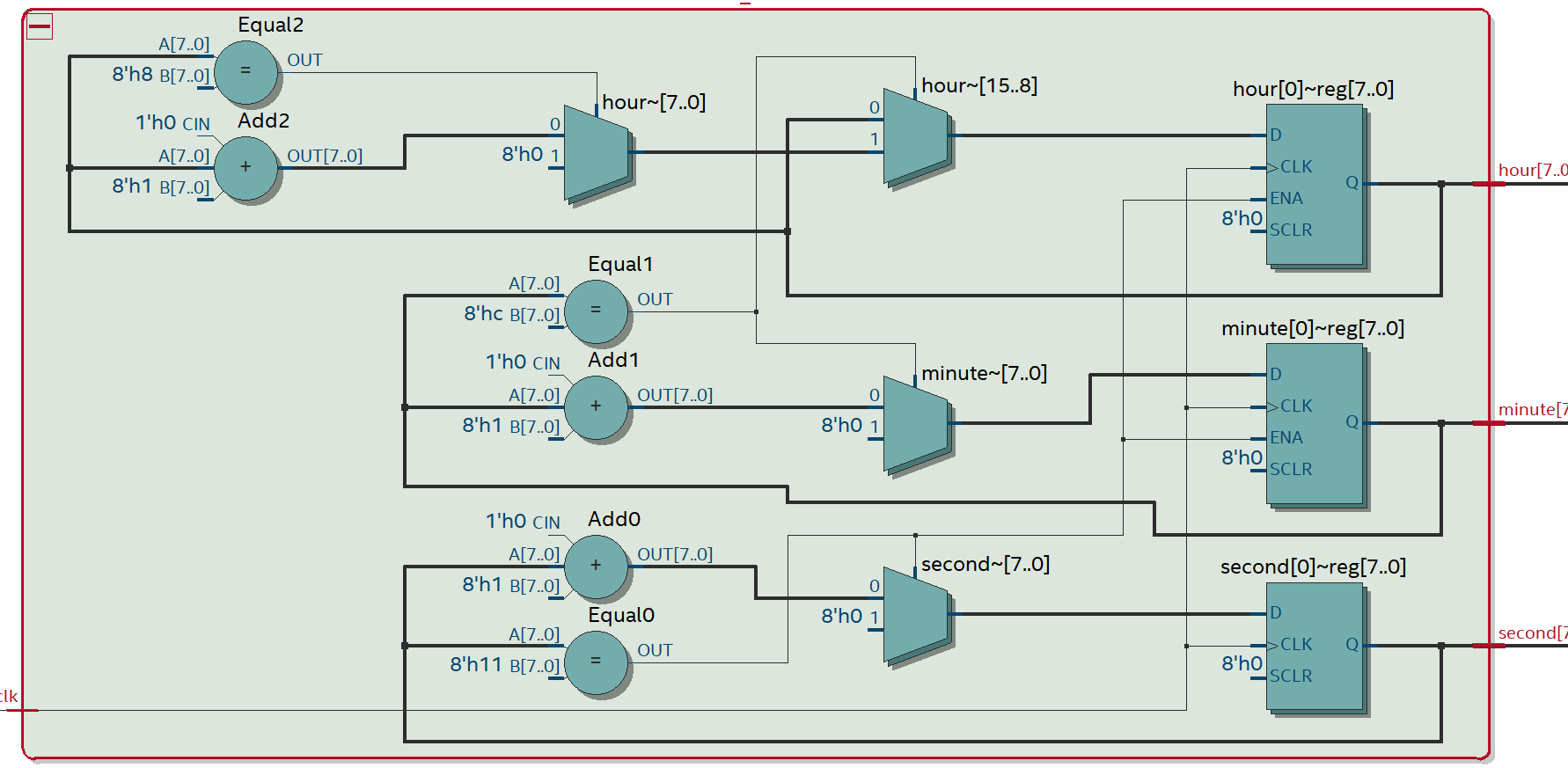

- 综合结果:

顶级模块的综合结果如图1,仅由分频模块和字符循环模块组成:

elec_clk模块的综合结果如图2:

summary结果如图3:

总结分析:

可以尝试将进位数据作为parameter,从而便于整个函数在后续过程中被调用。运行结果:

另附视频。

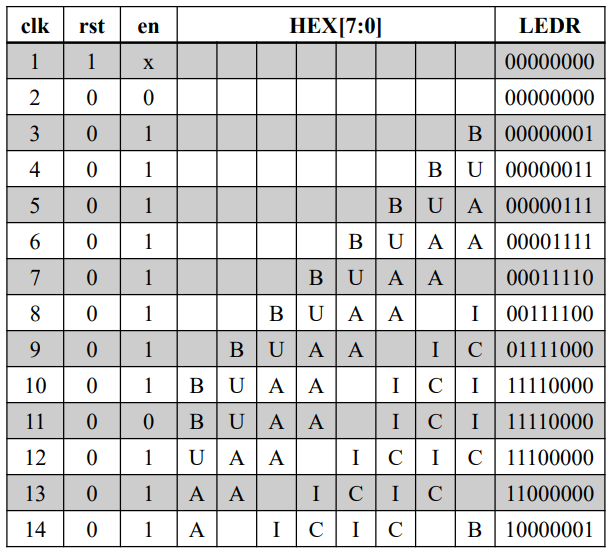

二、七段管循环显示

- 功能描述:

①在8个七段管上循环显示字符串:BUAA_1952-2022_(其中_表示七段管全灭);

②同时四个LED灯(LEDR[14-7])随BUAA的移动而移动;

③SW[17]作为复位信号,高电平有效,LED灯全灭;

④SW[0]作为使能信号,高电平有效,七段管和LED灯正常循环,低电平时,二者暂停循环;

⑤循环显示时间间隔为0.5s,即每隔0.5s字符串向左移一位。

- 设计方案:

①循环显示的时间间隔为0.5s,我们选择每逢时钟上升沿进行一次移位,则对应时钟的频率为2Hz,初始时钟采用开发板自带的50MHz振荡器,对该信号进行分频,其中M=25M;

②使用一个长度为7N的寄存器变量来存储字符,每个字符占七位,同时考虑到复位信号有效时,能够回复到初始状态,则应分别创建一个初始寄存器来寄存初始字符串,另一个寄存器来存储循环移位的结果,与此同时设置一个7*8的寄存器用来存储七段管上字符情况;

③对于LED灯,可知不同循环阶段时对应的亮暗情况是不同的,这里选择用i循环的状态做标记,遍历出i的状态及相应的LED灯亮暗情况。 - 关键代码:

module str_display(input clk,input reset,input ensignal,input [104:0] str,output reg [55:0] seven,output reg [7:0] LED_state);reg [104:0] shift_str;reg [3:0] i=14;always@(posedge clk) beginif(reset) beginshift_str[104 -: 105] <=str[104 -: 105];seven[55 -: 56] <= 56'b1;LED_state <= 8'b00000000;endelse if(!ensignal) beginshift_str[104 -: 105] <= shift_str[104 -: 105];seven[55 -: 56] <= seven[55 -: 56];LED_state <= LED_state;endelse beginseven[55:0] <= {seven[48 -: 49],shift_str[104 -: 7]};shift_str[104:0] <= {shift_str[97 -: 98],shift_str[104 -: 7]};case(i)4'b1110: LED_state <= 8'b00000001;4'b1101: LED_state <= 8'b00000011;4'b1100: LED_state <= 8'b00000111;4'b1011: LED_state <= 8'b00001111;4'b1010: LED_state <= 8'b00011110;4'b1001: LED_state <= 8'b00111100;4'b1000: LED_state <= 8'b01111000;4'b0111: LED_state <= 8'b11110000;4'b0110: LED_state <= 8'b11100000;4'b0101: LED_state <= 8'b11000000;4'b0100: LED_state <= 8'b10000000;default: LED_state <= 8'b00000000;endcaseif(i==0)i<=14;elsei<=i-1'b1;endendendmodulemodule fpga_seven(input CLOCK_50,input [17:0] SW,output [17:0] LEDR,output [6:0] HEX0,output [6:0] HEX1,output [6:0] HEX2,output [6:0] HEX3,output [6:0] HEX4,output [6:0] HEX5,output [6:0] HEX6,output [6:0] HEX7);wire clk;wire [55:0] seven;wire [7:0] LED_state;reg [104:0] str=105'b000000010000011001000100100011111111111001001000000100100100100011111101001001000000010010001001001111111;clk_div U0(.clk(CLOCK_50),.rstn(1),.clk_out(clk));str_display U1(.clk(clk),.reset(SW[17]),.ensignal(SW[0]),.str(str),.seven(seven),.LED_state(LED_state));assign LEDR[14 -: 8]=LED_state[7 -: 8];assign HEX7=seven[55 -: 7];assign HEX6=seven[48 -: 7];assign HEX5=seven[41 -: 7];assign HEX4=seven[34 -: 7];assign HEX3=seven[27 -: 7];assign HEX2=seven[20 -: 7];assign HEX1=seven[13 -: 7];assign HEX0=seven[6 -: 7];endmodule

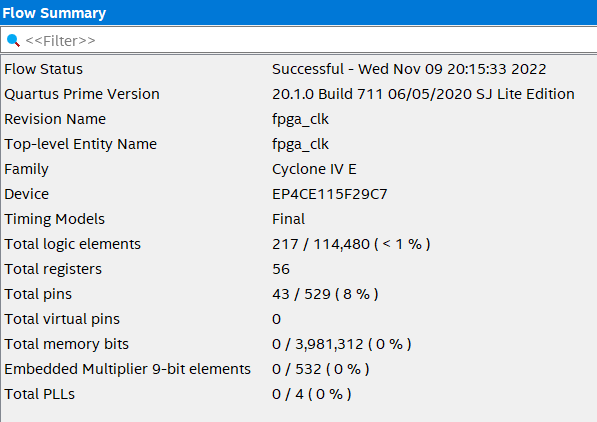

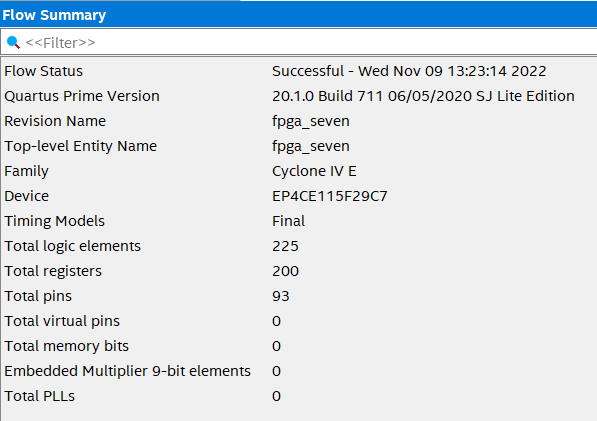

- 综合结果:

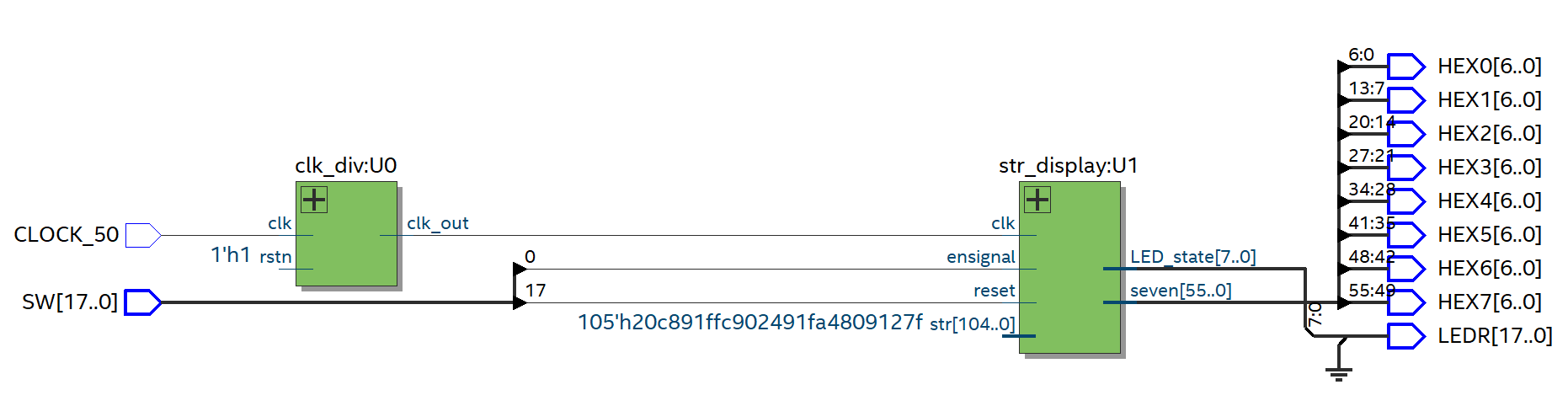

顶级模块的综合结果如图5,仅由分频模块和字符循环模块组成:

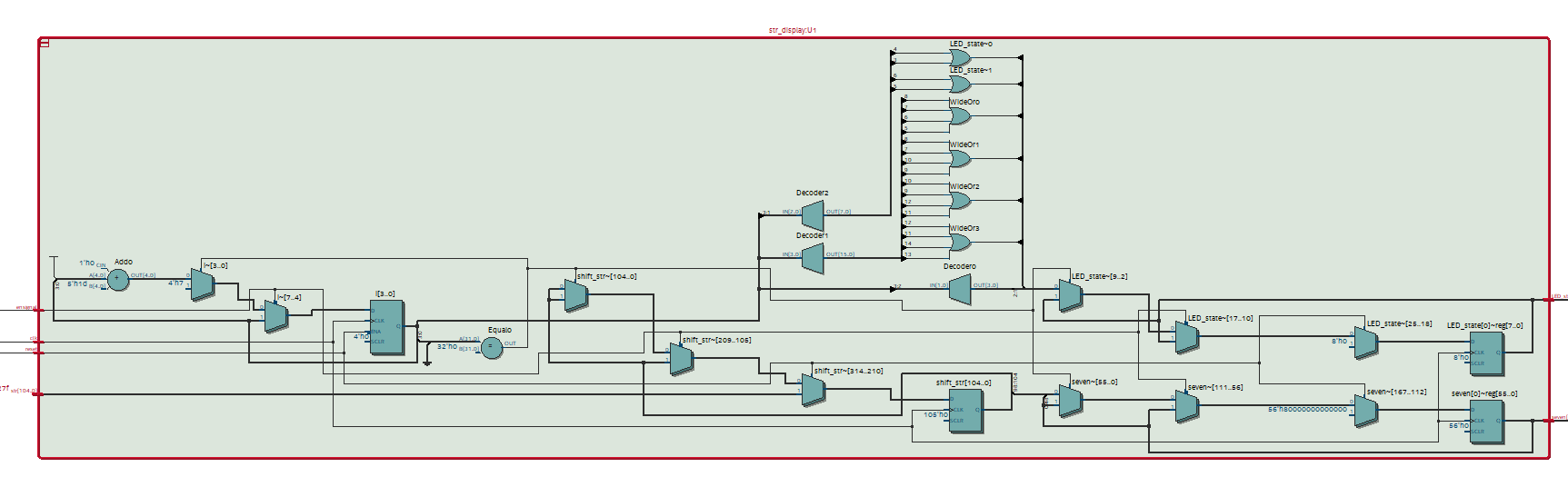

str_display模块的综合结果如图6:

7

总结分析:

最初进行设计时,将大部分功能的实现全部放在了顶级模块中,结果造成在调整思路时异常混乱,将功能模块和顶级模块的实现分开可以使得整体设计的脉络更加清晰,同时有利于在不同的电路中进行复用。运行结果:

另附视频。

数电第11周周结_by_yc的更多相关文章

- 模电&数电知识整理(不定期更新)

模电总复习之爱课堂题目概念整理 Chapter 1 1) 设室温情况下某二极管的反偏电压绝对值为1V,则当其反偏电压值减少100mV时,反向电流的变化是基本不发生变化. 2) 二极管发生击穿后,在击穿 ...

- 数电课设——琐碎

这几天没有更新过网站了,也没继续开发VellLock了,可是感觉还是没有闲着,一直在跟下面的一些元器件在打交道,当然下面的都是小儿科,英文文档都看得我快吐血了.数电基本属于棺材边上过的我,是各种头大, ...

- java第二周周学习总结

java运算符和循环 java运算符 一.for 语句 for 语句的基本结构如下所示:for(初始化表达式;判断表达式;递增(递减)表达式){ 执行语句; //一段代码} 初始化表达式:初 ...

- web前端笔记整理,从入门到上天,周周更新

由于大前端知识点太多,所以一一做了分类整理,详情可见本人博客 http://www.cnblogs.com/luxiaoyao/ 一.HTML 1.注释 格式:<!-- 注释内容 --> ...

- FPGA大公司面试笔试数电部分,看看你会多少

1:什么是同步逻辑和异步逻辑?(汉王) 同步逻辑是时钟之间有固定的因果关系.异步逻辑是各时钟之间没有固定的因果关系. 答案应该与上面问题一致 [补充]:同步时序逻辑电路的特点:各触发器的时钟端全部连接 ...

- 数电基础之《OC门》

OC门,又称集电极开路门,Open Collector. 为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去 ...

- 指尖上的电商---(11)Windows平台部署SolrCloud

SolrCloud是一种分布式解决方式,是基于zookeeper和solr的,能够简单理解为一种集群,能够提供分布式查询.分布式写索引. SolrCloud的结构大致是这种,一个SolrCloud包含 ...

- Flutter实战视频-移动电商-11.首页_屏幕适配方案讲解

11.首页_屏幕适配方案讲解 国人写的屏幕适配插件: https://github.com/OpenFlutter/flutter_screenutil 最新版本是0.5.1 在pubspec.yam ...

- STM32f103的数电采集电路的DMA设计和使用优化程序

DMA,全称为:Direct Memory Access,即直接存储器访问.DMA传输方式无需CPU直接控制传输,也没有中断处理方式那样保留现场和恢复现场的过程,通过硬件为RAM与I/O设备开辟一条直 ...

- 数电——全减器分析(用74HC138设计提示)

-1=1(即Di=1). Di=(Y1' * Y2' * Y4' * Y7')'可以得到74HC138来表示,(注意:Ai,Bi,Ci-1的各自位权对应A2,A1,A0) Ci同理可得.

随机推荐

- Elasticsearch:单节点数据迁移

Elasticsearch数据迁移:windows单节点迁移到windows 将源数据中的ES安装目录下的data/nodes目录整体拷贝到目标ES的对应目录下 迁移前请备份:迁移后需要重启ES: E ...

- rollup汇总作业-合并索引

文章转载自:https://blog.csdn.net/UbuntuTouch/article/details/106194800

- 使用 Elastic Stack 分析地理空间数据 (二)

文章转载自:https://blog.csdn.net/UbuntuTouch/article/details/106546064 在之前的文章 "Observability:使用 Elas ...

- 面试突击86:SpringBoot 事务不回滚?怎么解决?

在 Spring Boot 中,造成事务不自动回滚的场景有很多,比如以下这些: 非 public 修饰的方法中的事务不自动回滚: 当 @Transactional 遇上 try/catch 事务不自动 ...

- 谣言检测——(PSA)《Probing Spurious Correlations in Popular Event-Based Rumor Detection Benchmarks》

论文信息 论文标题:Probing Spurious Correlations in Popular Event-Based Rumor Detection Benchmarks论文作者:Jiayin ...

- 「产品运营」研发效能之DevOps平台如何运营?

有人常说「酒香不怕巷子深」.不是的,如果这个巷子是酒吧街,那最深的那家酒吧肯定是租金最便宜的.酒吧的地段好坏已经在租金价格上体现出来了.现在已经不是那个工具缺乏.有个工具就拍手称快.欣然去试用的时代了 ...

- 大数据常用的Linux命令

Linux文件系统基础知识 要想熟练使用命令,就先要熟练掌握Linux文件系统基础知识: 三个路径 当前路径:也叫当前工作目录,就是当前状态下用户所处的位置 相对路径:相对于当前工作目录开始的路径,会 ...

- 洛谷P4147 玉蟾宫 (单调栈)

要求我们去找一个最大矩形面积. 单调栈做法(和P1950 长方形那道题类似(一模一样)). 1 #include<bits/stdc++.h> 2 using namespace std; ...

- Tomcat实战之路

目录 第一节.安装升级 1.1.linux初始化 1.2.安装 1.3.升级 第二节.配置 2.1.虚拟主机 2.2.默认网站首页路径 2.3.跳转 2.4.配置Tomcat日志 第三节.安全 3.1 ...

- java 入土--集合详解

java 集合 集合是对象的容器,实现了对对象的常用的操作,类似数组功能. 和数组的区别: 数组长度固定,集合长度不固定 数组可以存储基本类型和引用类型,集合只能存储引用类型 使用时需要导入类 Col ...